# Workshop on Practical Use of Coloured Petri Nets and Design/CPN

Aarhus, Denmark, 10-12 June 1998

Kurt Jensen (Ed.)

DAIMI PB – 532 May 1998

# Preface

This booklet contains the proceedings of the 1998 Workshop on Practical Use of Coloured Petri Nets and Design/CPN. The papers are also available in electronic form via the CPN Web pages at University of Aarhus: http://www.daimi.aau.dk/CPnets/

Coloured Petri Nets and the Design/CPN tools are now used by more than 400 organisations in 38 countries all over the world (including 100 commercial companies). The aim of the workshop is to bring together some of the users and in this way provide a forum for those who are interested in the practical use of Coloured Petri Nets and their tools.

The workshop is organised by the CPN group at Department of Computer Science, University of Aarhus, Denmark. It takes place June 10-12, 1998 and it is preceded by a CPN tutorial, June 8-9.

The submitted papers were evaluated by a programming committee with the following members:

| H. Ammar       | USA           | ammar@ece.wvu.edu               |

|----------------|---------------|---------------------------------|

| J. Billington  | Australia     | j.billington@unisa.edu.au       |

| C. Capellmann  | Germany       | capellmann@tzd.telekom.de       |

| S. Christensen | Denmark       | schristensen@daimi.aau.dk       |

| H. Genrich     | Germany       | hartmann.genrich@gmd.de         |

| N. Husberg     | Finland       | Nisse.Husberg@hut.fi            |

| K. Jensen      | Denmark chair | kjensen@daimi.aau.dk            |

| D. Moldt       | Germany       | moldt@informatik.uni-hamburg.de |

| L. Petrucci    | France        | petrucci@iie.cnam.fr            |

| D. Simpson     | UK            | Dan.Simpson@brighton.ac.uk      |

| R. Valette     | France        | robert@laas.fr                  |

| R. Valk        | Germany       | valk@informatik.uni-hamburg.de  |

| K. Voss        | Germany       | klaus.voss@gmd.de               |

The programming committee has accepted 17 papers for presentation. Two thirds of the accepted papers deal with different projects in which Coloured Petri Nets and their tools have been put to practical use - most of these in an industrial setting. The remaining papers deal with different tool extensions.

After an additional round of reviewing and revision, some of the best papers from the workshop will be published as a special section in the International Journal on Software Tools for Technology Transfer (STTT).

Kurt Jensen

# Table of Contents

| S. Gordon and J. Billington Applying Coloured Petri Nets and Design/CPN to an Air-to-Air Missile Simulator                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| F. Burns, A. Koelmans, and A. Yakovlev:  Modelling of Superscalar Processor Architectures with Design/CPN                                               |

| S. Bulach, H. Baur, HJ. Pfleiderer, and Z. Kucerovsky: ALPiNe: A Hardware Computing Platform for High-Level Petri Nets                                  |

| R.B. Lyngsø and T. Mailund Textual Interchange Format for High-Level Petri Nets                                                                         |

| C. Maier, D. Moldt, and H. Rölke SNIFF: An Input/Output Library for Design/CPN                                                                          |

| W. Hielscher, L. Urbszat, C. Reinke, and W. Kluge On Modelling Train Traffic in a Model Train System                                                    |

| L. Jansen, M. Meyer zu Hörste, and E. Schnieder Technical Issues in Modelling the European Train Control System                                         |

| B. Lindstrøm and L. Wells Simulation Based Performance Analysis in Design/CPN                                                                           |

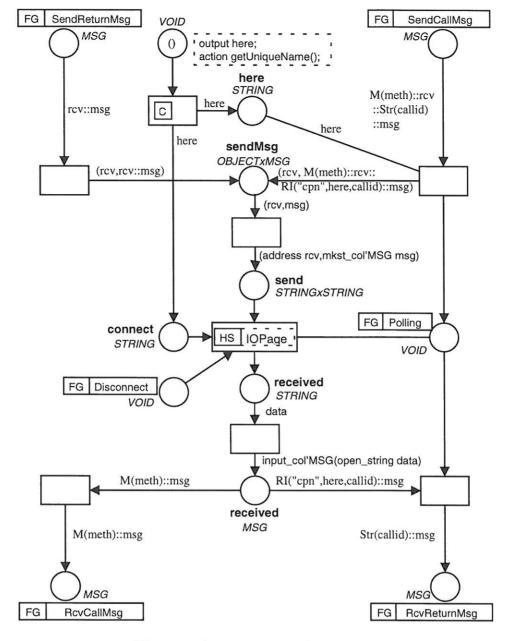

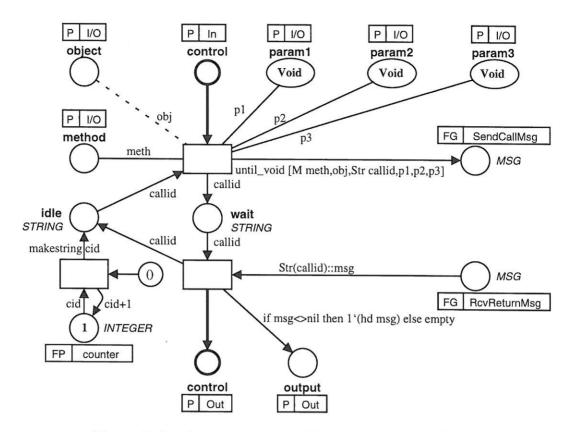

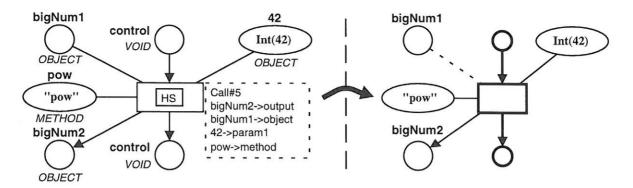

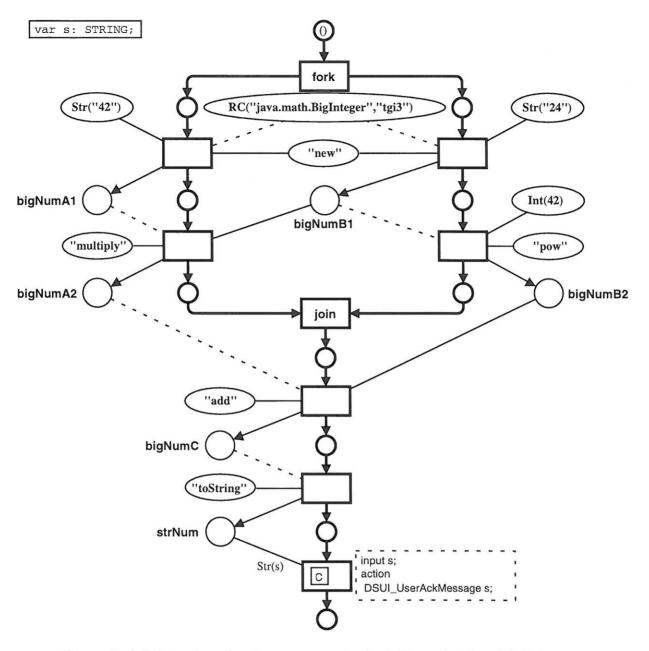

| O. Kummer, D. Moldt, and F. Wienberg A Framework for Interacting Design/CPN- and Java-Processes                                                         |

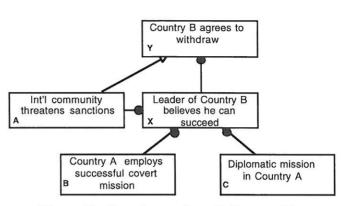

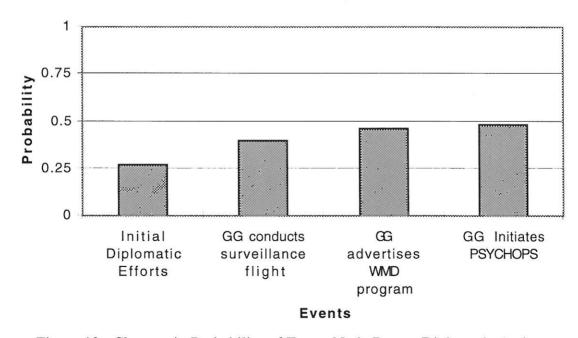

| L W. Wargenhals, I. Shin, and A.H. Levis Executable Models of Influence Nets Using Design/CPN                                                           |

| H.J. Genrich Experimental Symbolic Analysis of Net Systems                                                                                              |

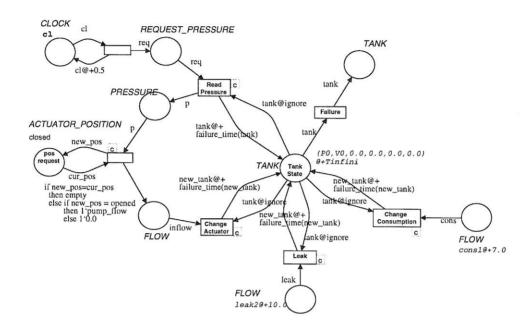

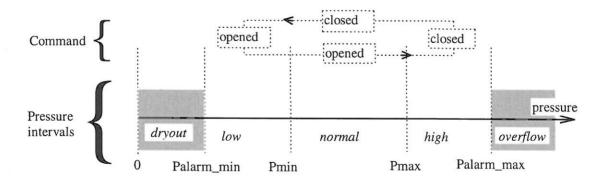

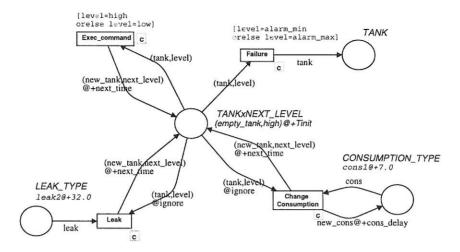

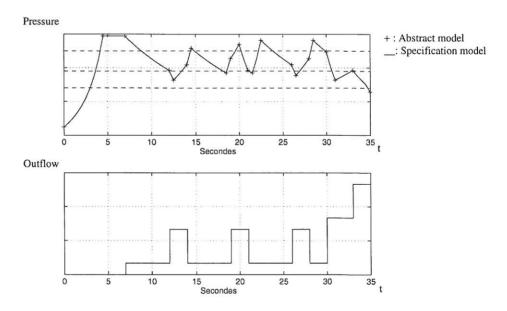

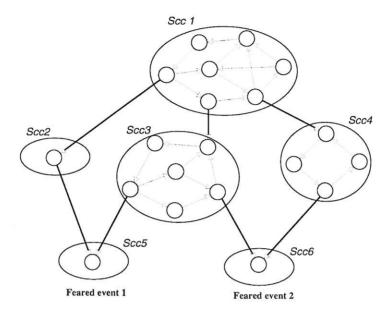

| G. Moncelet, S. Christensen, H. Demmou, M. Paludetto, and J. Porras  Dependability Evaluation of a Simple Mechatronic System Using  Coloured Petri Nets |

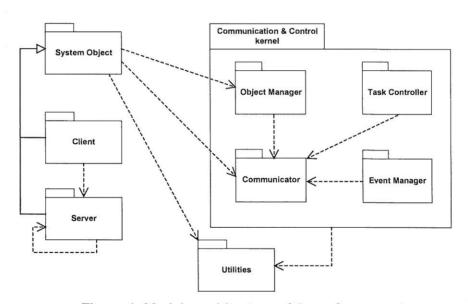

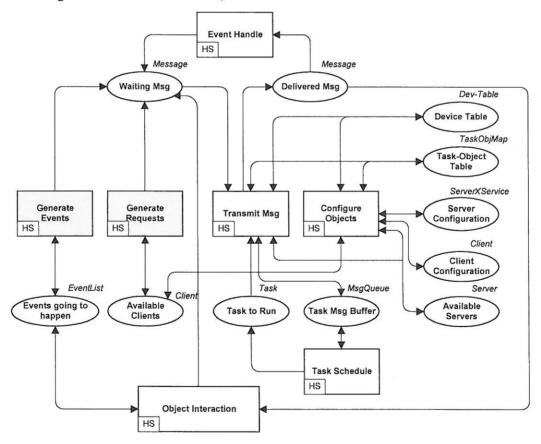

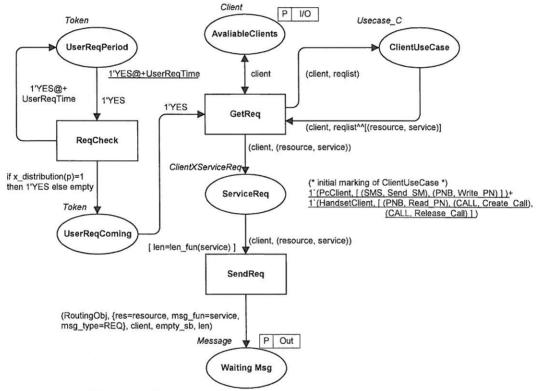

| J. Xu and J. Kuusela  Modelling The Execution Architecture of Mobile Phone Software Systems by  Coloured Petri Nets                                     |

| M.A. Jiffry Petri Net Analysis of the MASCOT Pool IDA Communication Mechanisms                                                                          |

| B. Kolics and K.M. Hangos A CPN Model of an Internet Object Cache                                                                                       |

| W.M. Zuberek, R. Govindarajan, and F. Suciu Timed Colored Petri Net Models of Distributed Memory Multithreaded Multiprocessors                          |

| L. Nigro and F. Pupo Using Design/CPN for the Schedulability Analysis of Actor Systems with Timing Constraints                                          |

# Applying Coloured Petri Nets and Design/CPN to an Air-to-Air Missile Simulator

Steven Gordon and Jonathan Billington

School of Physics and Electronic Systems Engineering, University of South Australia, Adelaide, SA 5095, Australia Email: [sgordon, jb]@spri.levels.unisa.edu.au

#### Abstract

In this paper the communication mechanisms of a missile engagement simulator are modelled and analysed. The simulator is developed as a testing platform for missile guidance and control algorithms. The simulation uses concurrency and remote execution concepts to enhance performance. Coloured Petri nets are a well suited formal approach for modelling and analysis of these concepts. Design/CPN is used to create and analyse the model of the simulation. A new requirement of the graphical user interface is identified for the simulation to operate successfully. The communication mechanisms are without deadlocks and are suitable for the simulator.

**Keywords:** Missile Simulator Design, Distributed Systems, Coloured Petri Nets, Formal Analysis

# 1 Introduction

Computer simulations of a missile engaging its target provide an environment for testing the guidance and control functions of the missile. The accuracy of the tests depends on the detail of the models used (eg. target, missile, etc.) and correct communication between the models. This paper addresses the problem of analysing the communication mechanisms for an Integrated Weapons Simulator (IWS) [CGW97a].

IWS is an Air-to-Air missile engagement simulator with a graphical user interface (GUI). Its development, from requirements specification through to testing and delivery, was part of a final year undergraduate project in Computer Systems Engineering at the University of South Australia. The three project members had joint supervision from staff of University of South Australia and the Defence Science and Technology Organisation (DSTO) Australia.

DSTO Australia, the research arm of Australia's Department of Defence, will use IWS to test various algorithms for the guidance and control of Air-to-Air missiles. To provide accurate simulations, the complexity of these algorithms may be large. Therefore, in designing IWS, two important features are desired so that the performance of the

system is adequate: concurrent execution and remote execution of separate components of the simulation. In providing these features it is necessary to verify that communication between the components is correct. Coloured Petri Nets (CP-nets) [Jen92] are well suited to modelling concurrency and hence are a suitable formal method for this problem. CP-nets have been successfully used to model and simulate concurrency in many applications [Jen97], and also for applications that use concepts of distributed execution [JM96].

In this paper CP-nets are used to model the communication mechanisms in IWS and to analyse them for deadlocks. An overview of the operation of IWS and its components is given. Then the CP-net models of IWS are described. An analysis of the entire simulation model is made, and finally the conclusions drawn from the analysis are presented.

# 2 The Missile Engagement Simulation

#### 2.1 Structure and Function of IWS

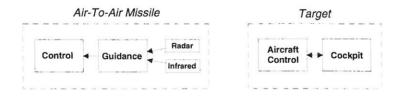

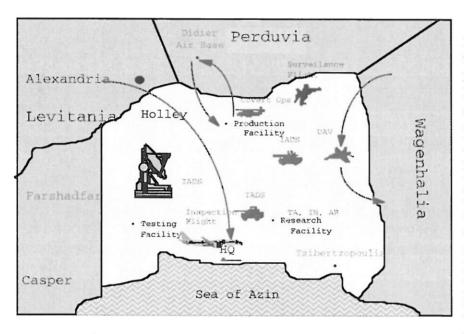

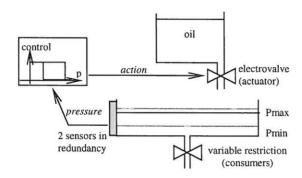

IWS is developed to give DSTO Australia a testing platform for missile guidance and control algorithms. Hence, IWS is required to provide appropriate testing functionality and mechanisms for easily changing the algorithms. The first requirement is implemented by the GUI. The second requirement is met by structuring IWS into components that represent the relevant functions of a missile engaging a target. Figure 1 shows the physical system IWS models.

Figure 1: Physical System

When the engaging aircraft detects the target, it launches an Air-to-Air missile. After launching, the missile uses its own guidance system to track the target. IWS begins simulation from this stage - it does not simulate the launching aircraft or procedure.

Figure 2: Missile and Target Physical Structure

The physical components of the missile and target that IWS is concerned with are shown in figure 2. The Air-to-Air missile has two detection mechanisms - a Radar (RF) and an Infrared (IR) sensor. These are physical devices on the missile that detect the location of a target. Both mechanisms are used to improve accuracy. For example, the

Radar may give inaccurate data if electronic counter measures are taken by the target. In this case, the Infrared data will be used. The data to be used is determined by the fusion mechanism in the Guidance component of the missile. The Guidance component then calculates the trajectory of the missile required to intercept the target. The Control algorithm controls the thrusters on the missile for it to maintain the calculated trajectory.

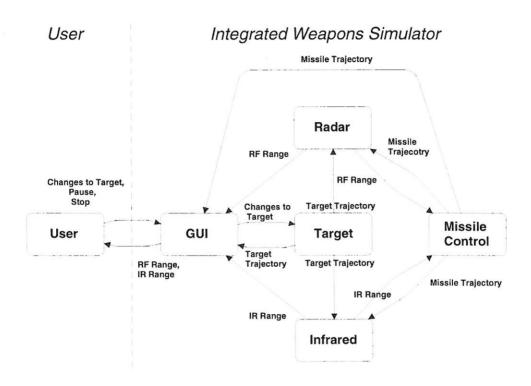

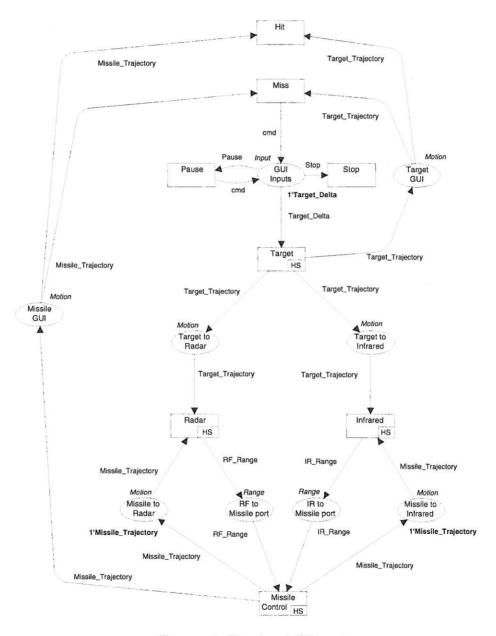

To simulate this physical system, IWS is divided into five components: Target, Radar, Infrared, Missile Control, and GUI. The components, and the interaction with the user, are shown in figure 3.

Figure 3: IWS Components

- User. The user of IWS plays three roles during the simulation:

- 1. running the simulation, eg. issuing "pause" and "stop" commands,

- 2. controlling the target by giving required changes to the target's trajectory, and

- 3. viewing the target from the missile's point of view, ie. using the radar and infrared ranges.

To do this, the user interacts with the GUI. (Future versions of IWS could separate the roles by introducing a new user who controls the target, while the first user runs the simulation from the missile's point of view [CGW97b].)

• GUI. The GUI component accepts inputs from, and presents the results of the simulation to, the user. Data from the Radar and Infrared systems are shown, and continuously updated, on a display for the missile. Inputs to Target are entered via a target controller window. This window, which allows changes in speed, elevation and azimuth, represents the throttle and control stick of the target aircraft.

The GUI also starts and stops the other four simulation components. It begins by sending the user inputs (changes to target trajectory) to the Target component. Once results from Target and Missile Control are received, the GUI compares the target and missile positions. If the two are the same, ie. the missile has hit the target, the simulation stops. Otherwise, the next user input is sent to Target and the simulation continues.

- Target. The Target component models a target for the simulation. The model must be able to perform realistic maneuvers so the guidance and control functions of the missile can be fully tested. A trajectory is calculated by Target based on inputs from the user (via the GUI). The inputs indicate a change in speed and direction. With these changes, the new position and velocity of the target are sent to the GUI, Radar and Infrared. Note that only a single target is modelled IWS does not consider multiple targets [CGW97a].

- Radar. The Radar component simulates the physical radar sensor on the missile. It requires both the missile and target current positions and velocities. The Radar calculates the range (distance, elevation, and azimuth) of the target from the missile. To model the inaccuracies of the radar, small amounts of noise are added to these calculations. The range is sent to Missile Control.

- Infrared. The Infrared component simulates the physical infrared sensor on the missile. It requires the same inputs as the Radar and sends a calculated range to Missile Control. Again, the inaccuracies of the infrared sensor (due to, for example, cloud coverage) are modelled by adding noise to the calculations.

- Missile Control. The Missile Control component includes the guidance and control functions of the missile. The ranges from the Infrared and Radar systems are used to calculate the required missile trajectory. In IWS, the magnitude of the missile velocity (the speed) is constant. Once these guidance and control functions are performed, Missile Control then simulates the actual motion of the missile. The resulting position and velocity are sent to the GUI, Radar and Infrared. Once successfully tested, it is proposed that the guidance and control algorithms used in Missile Control can be included in the software onboard an Air-to-Air missile.

#### 2.2 Communication Mechanisms

To achieve a likeness to the real-life situation, IWS executes each component concurrently. However, as the inputs of some components depend on the output of others, they cannot always be executing at the same time. For example, although in the real world the target and missile are independent, in IWS parts of the missile (Radar and Infrared) are synchronised with the target. There are several advantages of this mode of execution [SG94], the main one being computation speedup. This is particularly useful when the GUI must update its display (a CPU intensive task) and the other components can continue. The concurrent components are known as threads (eg. Target thread, Radar thread, etc.).

In addition to concurrency, the four simulation components (Target, Radar, Infrared, and Missile Control) will have the ability to be executed remotely. This will allow the resources for IWS (for the simulation) to be distributed across multiple computers [Tan92]. The section of each component executing remotely is called a *process*. The process will perform the calculations for models used in each simulation component.

Using both threads and processes in IWS introduces three communication mechanisms.

- 1. Thread-to-thread Each of the five threads use shared memory to communicate, with access guarded by semaphores. This is a simple and common technique for multithread communication. The threads are required to run on the same computer.

- 2. Thread-to-process The four simulation threads communicate with their corresponding processes using TCP/IP sockets. TCP/IP is the most common set of protocols used for communication over the Internet [Los95]. TCP/IP sockets are a standard feature of UNIX and as IWS will be developed for a UNIX environment [CGW97a], this method of interprocess communication allows IWS to run on almost any UNIX-based computer.

- 3. Process-to-process Direct communication is used between the Radar and Missile Control processes and between the Infrared and Missile Control processes. The ranges are sent directly to Missile Control because the GUI is not required to control the missile components (Radar, Infrared and Missile Control). However, there is a need for the GUI to control the Target and the missile components separately, hence there is no direct communication between the Target and Radar or Infrared.

For successful operation of IWS, it is required that each of the above mechanisms are tested to operate correctly. This includes analysis to determine whether the flow of data is correct and that the terminal state (the state the system is expected to stop in) is always reached.

## 3 CP-nets

CP-nets [Jen92, Jen94] are a class of high level nets that extend the features of basic Petri nets. The two most basic and important differences are that CP-nets use: tokens which are arbitrarily complex data, and inscriptions on arcs and transitions. With the use of hierarchies, these features make CP-nets a powerful modelling tool for large applications.

The CP-nets in this paper were edited, simulated and analysed using Design/CPN [Sof93]. The Occurrence Graph (OG) tool [CJ95] of Design/CPN was used for analysis. This tool allows the creation of the full occurrence (or reachability) graph and also provides the capability to query the OG to determine properties of the system being modelled.

The choice of CP-nets as a formal method for modelling and analysis of IWS was based on: the existing experience with CP-nets, and their natural capability of modelling concurrent events.

The CP-nets were created by one member of the IWS Project group. Previous experience with CP-nets and Design/CPN consisted of: 9 x 2 hour lectures introducing Petri nets, High-level nets and example applications, and a 2 hour practical session introducing Design/CPN.

The project member also had experience with SDL [CCI89], but lack of available software tools for analysis made it an unsuitable method for this problem.

A major component of this work was the exploration of different approaches to modelling IWS and the levels of abstraction that were appropriate. This process was slowed by the lack of experience with some Design/CPN features (eg. hierarchies). Including this initial work and reporting on results, the modelling and analysis consisted of approximately 11 man weeks of work.

### 4 Missile Simulation Model

#### 4.1 General Structure

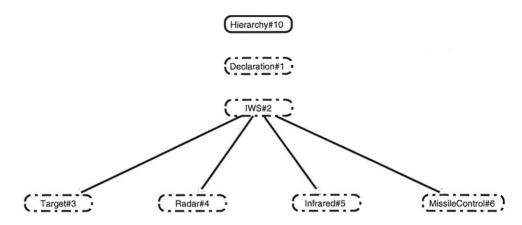

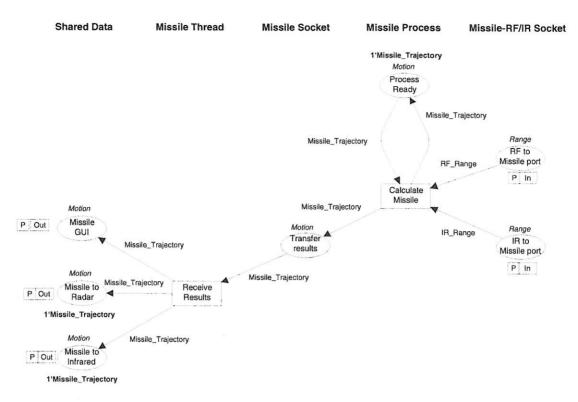

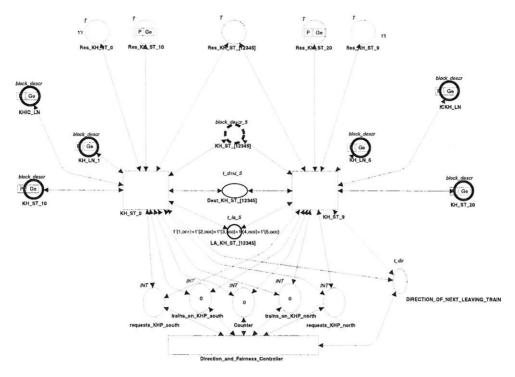

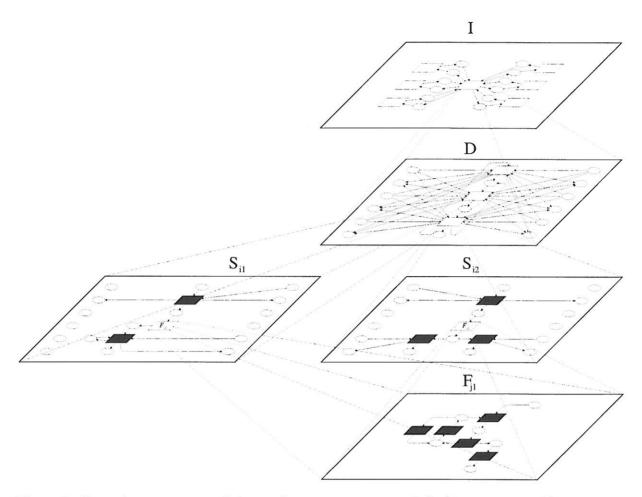

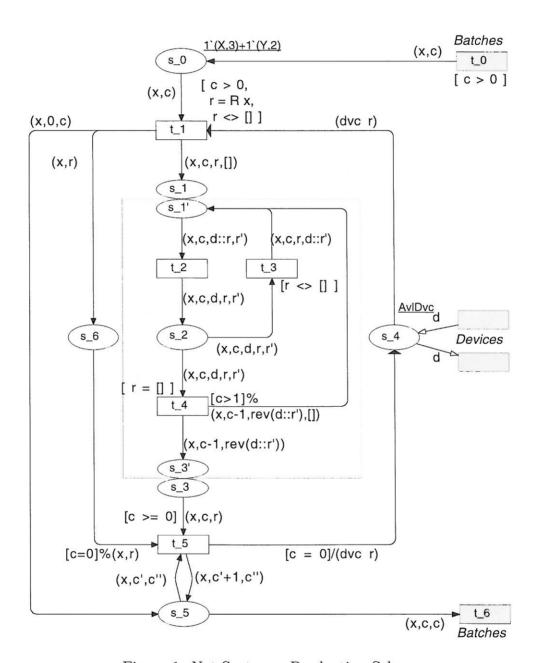

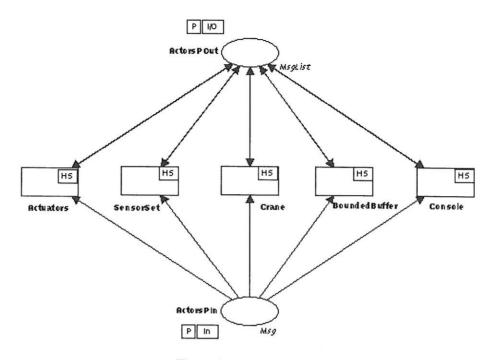

The model of IWS consists of five pages of CP-nets and a global declaration node. This is indicated in figure 4. A top level model of IWS shows the interfaces between the four simulation components (figure 6).

Figure 4: CP-net Hierarchy Page

Four transitions of the top level model are expanded into subpages to represent the simulation components ie. Target, Radar, Infrared, and Missile Control (figures 7 to 10).

#### 4.2 Global Declarations

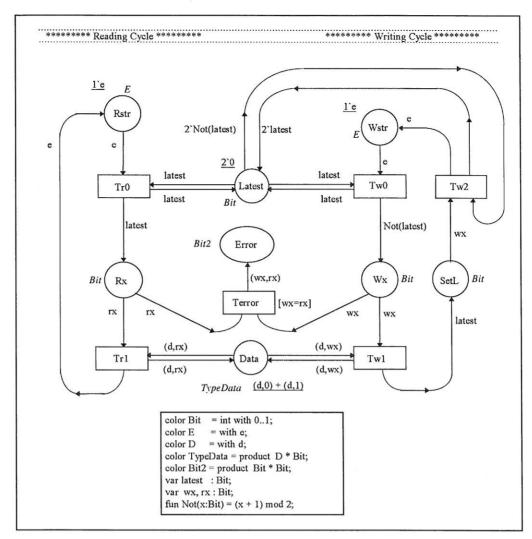

The global declaration page is shown in figure 5.

```

color Status = with Ready | Wait;

color Input = with Target_Delta | Pause | Stop;

color Motion = with Target_Trajectory | Missile_Trajectory;

color Range = with RF_Range | IR_Range;

var cmd:Input;

```

Figure 5: Global Declarations

The colour Status indicates the state of a thread when not processing data. For example, when the Radar thread (figure 8) is ready to receive new data from the target and missile, a Ready token is sent from place Thread Ready.

The colour Input represents a single input from the user. Target\_Delta represents the change to target trajectory the user wants.

The positions and velocities of the target and missile are modelled as a trajectory. These are represented by the colour Motion.

The colour Range represents the range of the target relative to the missile. The radar (RF) and infrared (IR) ranges are different.

The variable cmd is used to represent the next user input. It can be either Target\_Delta, Pause or Stop.

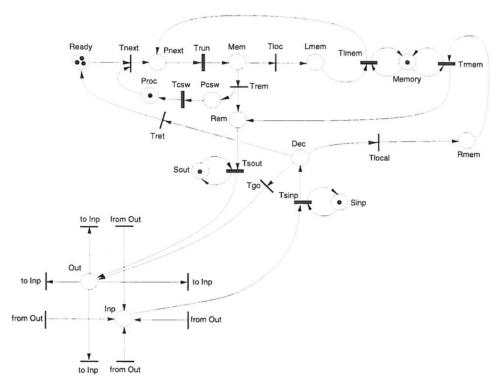

#### 4.3 IWS

#### 4.3.1 Top-level CP-net

The top level CP-net (figure 6) shows the functionality and flow of data in IWS. The user is not represented explicitly, instead the place GUI inputs stores the current command from the user (either a Pause, Stop or Target\_Delta) and it is processed by one of the three output transitions. If the user issues a pause command the Pause transition fires and a new user command is generated. If stop is issued by the user then transition Stop will fire leaving no more user commands. If Target\_Delta is the user command then it is sent to Target and the simulation continues.

Figure 6: Top-level CP-net

When the new target and missile trajectories have been calculated two conditions can occur: the positions of each are the same (within a given tolerance) meaning the missile had hit the target and the simulation should stop; or the positions are not the same and

the simulation should continue. This is modelled using the two transitions Hit and Miss. If Miss occurs a new user command is generated and the simulation can continue. If Hit occurs, no more transitions will be enabled causing the simulation to stop.

#### 4.3.2 Structure of CP-net Subpages

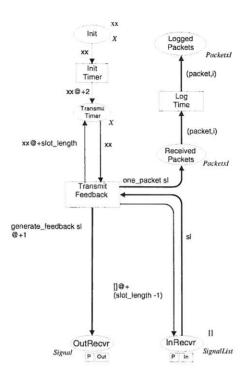

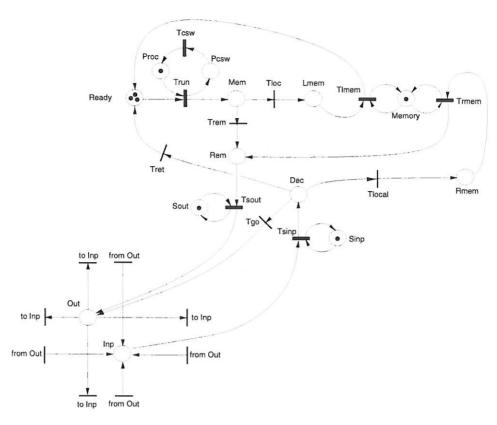

The four simulation component pages (figures 7 to 10) are structured into columns to visually separate the shared data, threads, processes, and communication mediums.

The first column represents the shared memory between each of the four threads. The data (or tokens) in this area can be accessed by any of the threads. When implemented, access to the memory will be guarded by the use of semaphores.

The second and fourth columns in the CP-net pages represent the procedures carried out by the threads and processes, respectively.

The third and fifth columns of the models represent the TCP/IP socket connections. The third column is for connections between the thread and its corresponding process, whereas the fifth column represents a connection between two processes. Although TCP/IP connections incorporate queueing mechanisms, they are modelled as simple buffers in the CP-nets. This is because the control of data flow does not allow overtaking of data, hence there are no need for queues.

For all the models, it is assumed that the socket connection has been setup and initial data for the processes has been received.

The functions performed by the simulation components in IWS are described in the following sections.

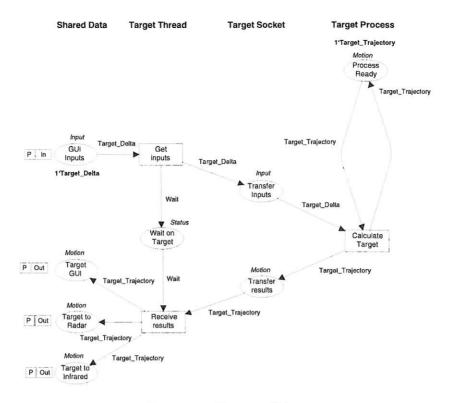

#### 4.3.3 Target

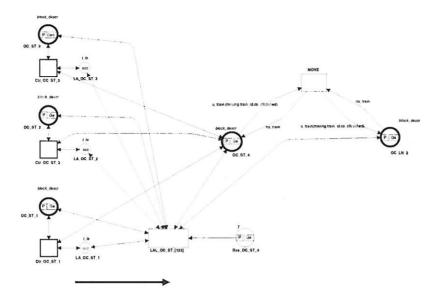

The Target CP-net is shown in figure 7. The Target process begins in the "ready" state. This is indicated by an initial marking of Target\_Trajectory for the place Process Ready. The first user command is also an initial marking for the place GUI Inputs.

When a user target change is received from the GUI, it is sent to the Target process. The transition Calculate Target represents the calculations made using the user target change and old target trajectory (from Process Ready) to produce a new target trajectory. This result is sent back to the Target thread and then to the GUI, Radar and Infrared.

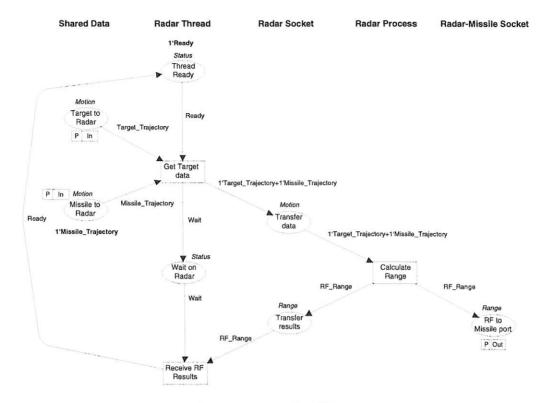

#### 4.3.4 Radar

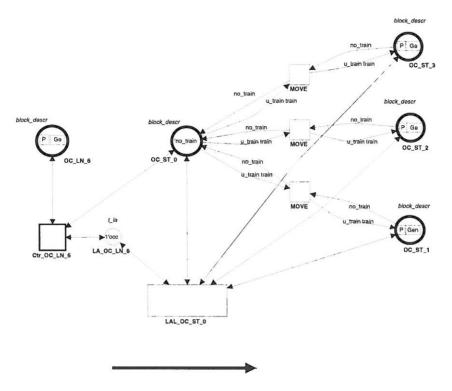

The Radar thread begins in the "ready" state (figure 8). There is also an initial marking Missile\_Trajectory in the Missile to Radar place. This marking represents the initial missile position and velocity so Radar (and Infrared) can calculate an initial range to be used by Missile Control.

When the target trajectory arrives at place Target to Radar (and the missile trajectory is in Missile to Radar), transition Get Target data is enabled. Upon firing, the target and missile trajectories are transferred together to the Radar process and with them a new range can be calculated. The range is sent back to Missile Control via the Radar-Missile socket, and also to the GUI via the Radar thread.

Figure 7: Target CP-net

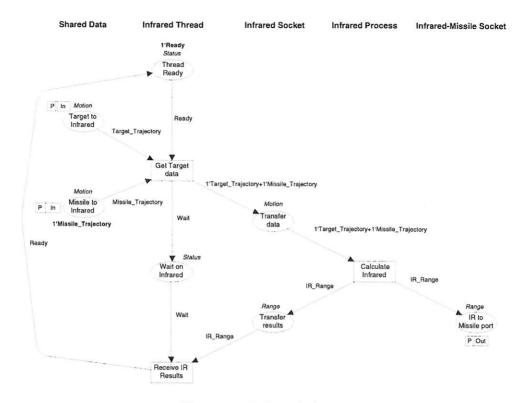

#### 4.3.5 Infrared

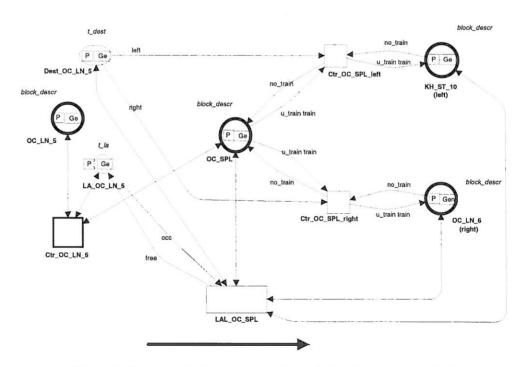

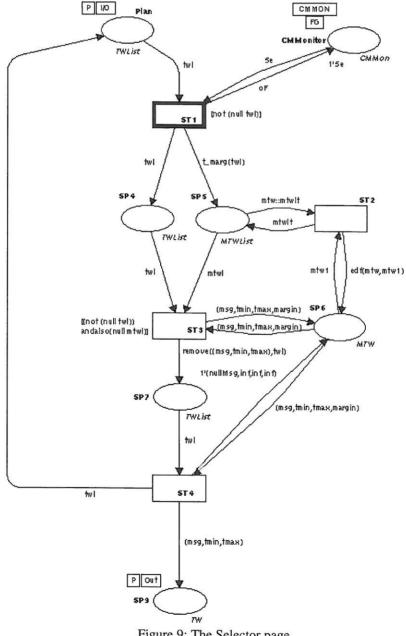

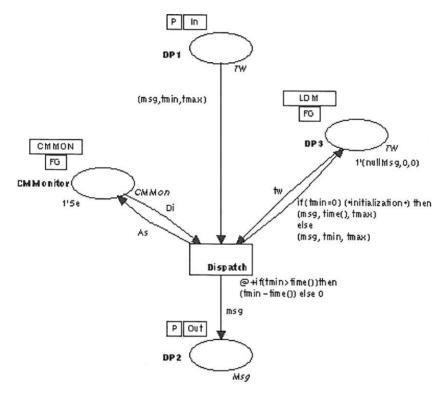

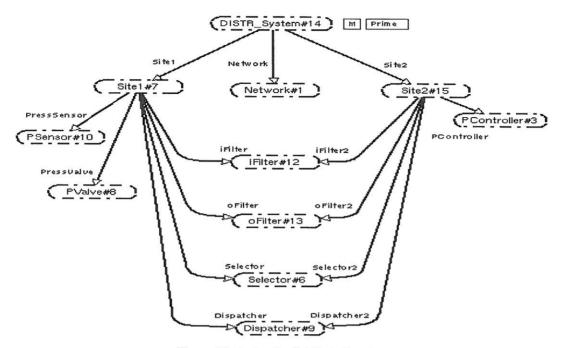

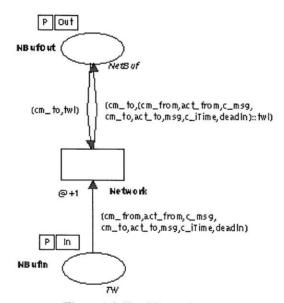

The CP-net model of the Infrared component (figure 9) operates in the same manner as the Radar model.

#### 4.3.6 Missile Control

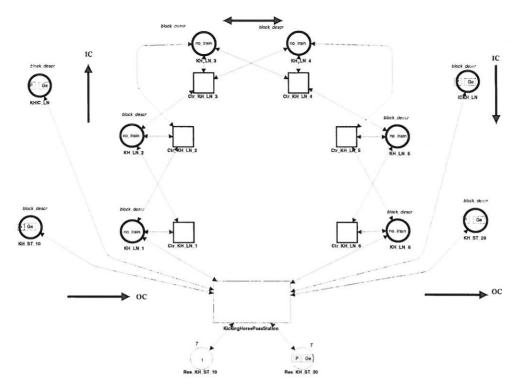

The Missile Control is straightforward (see figure 10). An initial missile trajectory is stored in Process Ready and when both the Radar and Infrared ranges arrive the new missile trajectory is calculated by the Missile Control process. The results are sent to the Missile Control thread which stores them as shared data to be accessed by the Radar and Infrared.

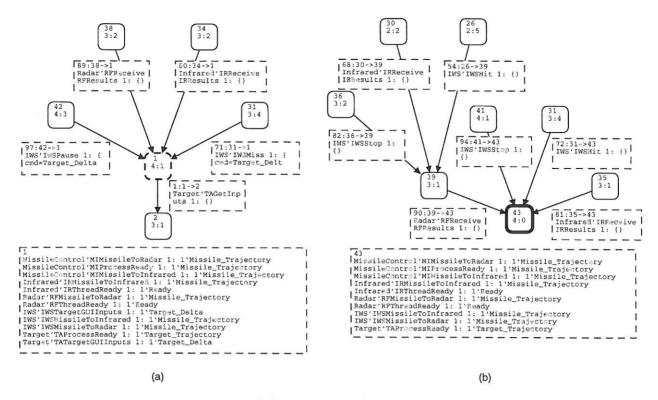

# 5 Analysis

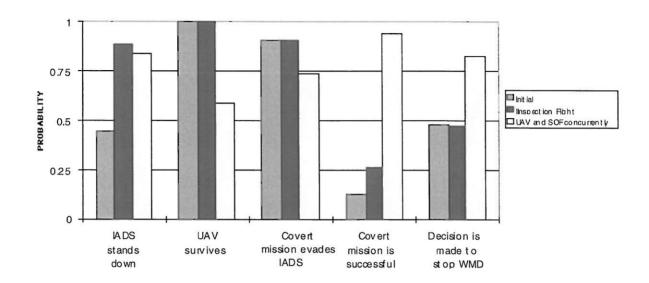

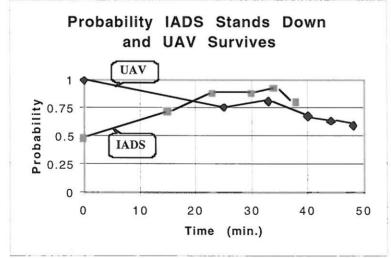

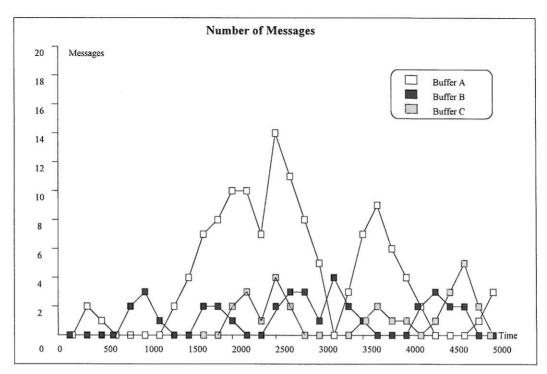

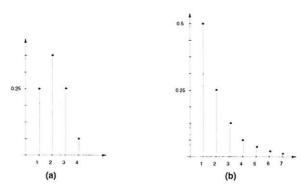

The missile engagement simulation model was analysed using Design/CPN. Using Design/CPN interactive graphical simulations and automatic simulation modes are available. Simulating was useful when developing the models, and to view the flow of data in IWS. However, it was not suitable for testing all possible states of the models. The formal analysis of the CP-net model involved the OG tool of Design/CPN. The OG tool calculates the occurrence graph for the CP-net model. Rather than visually inspecting all nodes, queries were made of the occurrence graph to examine its properties. Table 1 shows the results of the occurrence graph generation.

The OG was cyclic - each simulation iteration was represented by one cycle of the occurrence graph. Figure 11(a) shows the initial marking (node 1) and its immediate successor and predecessor nodes. Note that the place and transition names used are

Figure 8: Radar CP-net

| Nodes | Arcs | Time | Terminal States | Undesired |

|-------|------|------|-----------------|-----------|

| 57    | 124  | 1 s  | 1               | 0         |

Table 1: OG Results

extensions of the labels used in the models. Also, places with empty markings are not shown.

There was one terminal state and no deadlocks (undesired terminal states) for the model. Closer examination of the terminal state and the arcs leading to it confirmed that the simulation stopped by either a "hit" or by the user. Figure 11(b) shows the terminal state (node 43) of the OG. A selection of nodes leading to this node are also shown. The arc from node 31 indicates Hit has occurred causing the simulation to stop. The arc from node 41 indicates the user has input a Stop command again causing the simulation to stop. The other two input arcs of node 43 show the transitions that can occur after Hit or Stop occurs. These two transitions are Receive RF Results and Receive IR Results. When the Radar or Infrared threads receive results from their corresponding processes (ie. these two transitions fire), the data is made available to the GUI so the display can be updated. However, when Hit or Stop occur the display is frozen so the user can view and analyse the results. Therefore, if Hit or Stop occur before either Receive RF Results or Receive IR Results then the latest results will not be displayed. To be sure this does not occur, the GUI must force an update of the display when stopped before allowing the user to perform analysis on the results.

Figure 9: Infrared CP-net

# 6 Conclusions

Coloured Petri nets have been used to test the communication mechanisms for a distributed Air-to-Air missile engagement simulator.

The first step in achieving the goals was to create a top-level CP-net for IWS. This showed the data flow and basic functionality of the system. Using Design/CPN's hierarchy features, the relevant transitions were then expanded into subpages to model the interaction between threads and processes and the calculations performed by IWS. This allowed the concurrent execution of the IWS components to be analysed. This top-down approach to modelling IWS was advantageous because initially it was unclear how much detail was needed. Further functionality could be added when it is required.

Once the models were completed they were analysed using the OG tool of Design/CPN. This allowed occurrence graphs to be calculated and properties of it examined using queries. The analysis showed that the models behaved as required. There were no deadlocks and the individual threads and processes executed correctly. However, a new requirement of the GUI was identified, ie. a display update should be forced when the simulation is stopped.

From the analysis of the CP-nets, under the requirements from DSTO Australia, the communication mechanisms modelled are suitable for use in IWS. However, to take full advantage of the performance enhancement from concurrency and remote execution, it is necessary that the system performance is not restricted in other areas. In particular, a preliminary investigation into the effects of failures in the communication between processes and the methods for coping with such failures has been made. The models developed in this work served as a basis for this investigation.

There are also possibilities for improvements and further modelling and analysis to

Figure 10: Missile Control CP-net

test other features of the IWS simulation.

- A requirements-level CP-net which specifies: interactions between the user of IWS and the simulation, and interactions between components within the simulation. A comparison can then be made between the requirements- and design-level CP-nets.

- Detail modelling of the GUI (at the design-level) and the interactions with the simulation. This would introduce more levels of concurrency (eg. the GUI updating it's display while the simulation performs the next calculation) and require more detailed analysis.

- Further modelling and analysis if multiple targets are introduced into IWS [CGW97a].

# 7 Acknowledgements

We would like to thank Hatem Hmam and Len Sciacca from DSTO for the technical background on Air-to-Air missiles and IWS, and Chris Steketee for his comments on TCP/IP. Also, the financial support of the University of South Australia's Institute for Telecommunications Research is appreciated.

# References

[CCI89] CCITT. Recommendation Z.100 Functional Specification and Description Language. In *Blue Book*, Geneva, Switzerland, 1989. ITU.

Figure 11: (a) Initial and (b) Terminal States

- [CGW97a] B. Collas, S. Gordon, and H. Widjaja. *IWS Requirements Specification*. Number 1.2. University of South Australia, Adelaide, Australia, 1997.

- [CGW97b] B. Collas, S. Gordon, and H. Widjaja. *IWS System Manual*. Number 1.0. University of South Australia, Adelaide, Australia, 1997.

- [CJ95] S. Christensen and K. Jensen. Design/CPN Occurrence Graph Tool User's Manual. Computer Science Department, Aarhus University, Aarhus, Denmark, 1995.

- [Jen92] K. Jensen. Coloured Petri Nets Basic Concepts, Analysis Methods and Practical Use. Springer-Verlag, 2nd edition, 1992.

- [Jen94] K. Jensen. Coloured Petri Nets Basic Concepts, Analysis Methods and Practical Use, Volume 2. Springer-Verlag, 1994.

- [Jen97] K. Jensen. Coloured Petri Nets Basic Concepts, Analysis Methods and Practical Use, Volume 3. Springer-Verlag, 1997.

- [JM96] J.B. Jorgensen and K.H. Mortensen. Modelling and Analysis of Distributed Program Execution in BETA using Coloured Petri Nets. In *Application and Theory of Petri Nets*, number 1091 in Lecture Notes in Computer Science, pages 249–268. Springer-Verlag, 1996.

- [Los95] P. Loshin. TCP/IP for Everyone. Academic Press, Chestnut Hill, MA, USA, 1995.

- [SG94] A. Silberschatz and P. Galvin. *Operating System Concepts*. Addison-Wesley Publishing Company, Reading, MA, USA, 1994.

- [Sof93] Meta Software. Design/CPN Reference Manual for X-Windows. Meta Software Corporation, Cambridge, MA, USA, 1993.

- [Tan92] A. Tanenbaum. *Modern Operating Systems*. Prentice-Hall, Englewood Cliffs, NJ, USA, 1992.

# Modelling of Superscalar Processor Architectures with Design/CPN

Frank Burns, Albert Koelmans and Alexandre Yakovlev

Department of Computing Science

University of Newcastle upon Tyne, NE1 7RU, UK

#### Abstract

We describe aspects of modelling a generic superscalar processor architecture using Coloured Petri nets, for the purpose of analysis of its real-time properties, such as Worst Case Execution Time for a block of instructions. The model can be simulated within the Design/CPN environment. The results of the simulation are displayed using a custom graphics tool written in Tcl/Tk.

#### 1 Introduction

Design of real-time systems, which must respond to external events within strict time bounds, involves a mapping between the logical and physical levels of a system specification. This mapping determines the quality of the timing information available at each level of abstraction. A crucial issue, which introduces a significant element of temporal uncertainty, is the way in which the system design is tied together with the use of specific hardware components. Even though some of these components can be standard, off-the-shelf ones, their timing characteristics can be very imprecise for the purpose of acquiring reliable, yet not too pessimistic data to be used at higher levels (e.g., worst execution times of program code to be used for task scheduling). Moreover, some hardware is designed in a special way (e.g., interface circuits), which is increasingly the case for embedded applications. In such situations, realistic timing information about the hardware becomes available only during software development, which creates an additional adequacy problem.

This problem arises increasingly due to the following three major factors:

- New processor architectures are becoming ever more complex. They

include many stages of pipelining, out-of-order execution, parallel execution of several instructions, and multi-level caching mechanisms;

- System architectures often involve non-standard components whose temporal parameters are not known in advance;

- Future systems will tend to become more asynchronous. Even if their core elements are clocked, the overall system will either be multiclocked or almost entirely self-timed.

We are developing a methodology and an associated set of software tools for the modelling and analysis of timing specifications of hardware platforms, in particular asynchronous RISC processors, based on the use of Coloured Petri Nets (CPNs) [3]. Previous work in this area (e.g. [6]) has mainly focused on the use of P/T nets. The ability to model asynchronous interaction inherent in Petri Nets would enable us to take into account some fine behavioural issues like the effect of potential 'request-acknowledgement' handshakes in the interfaces between units, and dynamic allocation of instructions on different units. In this paper we present a detailed model of a generic superscalar RISC processor developed using the Design/CPN tool.

# 2 Why ordinary Petri nets are insufficient

Petri nets have traditionally been used for modelling and analysis of digital systems. Processor architectures are no exception [2]. In addition to classical "qualitative" properties for verification, like deadlocks and boundedness, the real-time aspect requires ways of obtaining more detailed, "quantitative", analysis, such as worst-case execution time for a block of instructions. The former type of modelling need only capture fairly general properties (possibilities) of the system behaviour (e.g., the processor execution pipe cannot overflow with instructions). The latter is certainly more specific with regards to the actual paths taken by the modelled system under a given set of data. Hence the "quantitative" analysis often lends itself to simulation, performed in addition to the exploration of possibilities.

Use of ordinary Place-Transition nets, which can describe the control flow quite comfortably and provide efficient ways of "qualitative" verification, cannot themselves (without additional annotation) represent the effect of data, associated with the model states, on the execution of actions in the

processor. Note that in modelling processor architectures, the role of data path is played by instruction flow. Each instruction is a complex (again, depending on the level of detail we want to represent) data object. This object consists of attributes reflecting not only its type and operands, but also important (in the superscalar case) information about dependencies, targets, branching etc. Since all these aspects affect the temporal profile of the instruction in the overall instruction flow, the model should be able to represent them as accurately as possible. Coloured Petri nets appear to be capable of providing the processor model with appropriate mechanisms for data typing. These mechanisms can concretise both the notion of a state (token marking) and the data-dependent conditions of action execution.

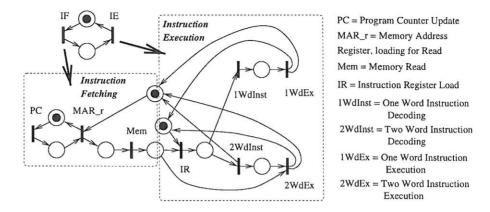

Before we proceed to a detailed model of a processor, let us consider a simplified control flow model of an asynchronous processor, described with a Place-Transition net as shown in Figure 1. We believe that this figure is self-explanatory. More details about the use of Place-Transition nets in the design of a processor can be found in [4].

At the highest abstraction level, the behaviour of a processor consists of two actions, Instruction Fetching (IF) and Instruction Execution (IE), which alternate and are therefore performed sequentially.

These actions can be refined into subactions according to our knowledge about the processor architecture. Thus, the IF action can be seen as a process, i.e. a Petri net fragment, consisting of the following subactions: incrementing a Program Counter (PC), loading a Memory Address Register with the new address for memory reading (MAR\_r), and reading the new instruction word from Memory (Mem). The IE action can be refined into a process (another Petri net fragment) involving other subactions: loading an Instruction Register (IR), decoding, activating and executing the fetched instruction for two possible instruction formats, a one word instruction (1WdInst and 1WdEx) and a two word instruction (2WdInst and 2WdEx). The part of the process concerned with two word instruction execution requires two memory cycles. As can be observed from the analysis of this Petri net, the initial sequential operation between IF and IE has been refined into a model which allows concurrency between actions with smaller granularity. For example, the PC action can be executed concurrently with instruction reading, decoding and execution. Another paradigm appearing at this level is that of choice between two types of instruction execution. The refined model can be subjected to verification (e.g. for absence of deadlocks or undesirable conflicts between actions) and/or performance analysis (e.g., estimation of the degree of concurrency between transitions, evaluating crit-

Figure 1: Place-Transition net model of an asynchronous processor.

ical paths, simulation). The process of refining the design can be continued until the designer realises that the abstract behavioural model satisfies the desired functional and quantitative requirements. The result of this design stage is a specification of the control flow in such a form that its actions, i.e. transitions in the labelled Petri net model, can be easily mapped onto the primitive operations of the datapath units. This part of the design process is described in detail in [4].

# 3 Basics of processor modelling

We model instruction types by first defining a set of predefined identifiers using an enumerated colorset as follows:

Color Instr = with INT | FPADD | MUL | DIV | BRA | NOOP; It is then possible to create a record colorset using appropriate fields to model an instruction completely:

```

color Value = record

no: Line *

instr: Instr *

d: Dep *

d': Dep *

t: Target timed;

```

assuming that the instruction has dependencies d, d' and a destination t, which links those instructions sharing the same target register. It must be

noted that the model we are trying to develop here is primarily of timing not hardware.

To model processor timing we need to define updates to Program Counter (PC) values at various points in our model. In Design/CPN variables, guards and arc inscriptions can be used in order to do this. CPN variables can be defined for any predefined type or colour. For example, we can define a variable fetch of type Value to represent a fetched instruction:

#### var fetch: Value;

Once variables are defined it is possible to model the occurrence of updates to processor values by referencing the values of tokens arriving at the input places of transitions. Guards provide predicates to check the values of tokens at input places to determine that the correct values are present for enablement. For example, at the **FETCH** stage we can determine the next instruction selection by defining a fetch transition guard which checks the instruction number against the pc count:  $[\#no\ fetch = pc]$  Here the selector  $\#no\ checks$  the number of the instruction fetched against the value of the program counter.

An arc inscription can then be defined to update the PC value to the next instruction number ready for the next selection. This is modelled in Design/CPN by using the following multiset arc expression which adds one to the program counter variable.

#### 1'(pc+1)

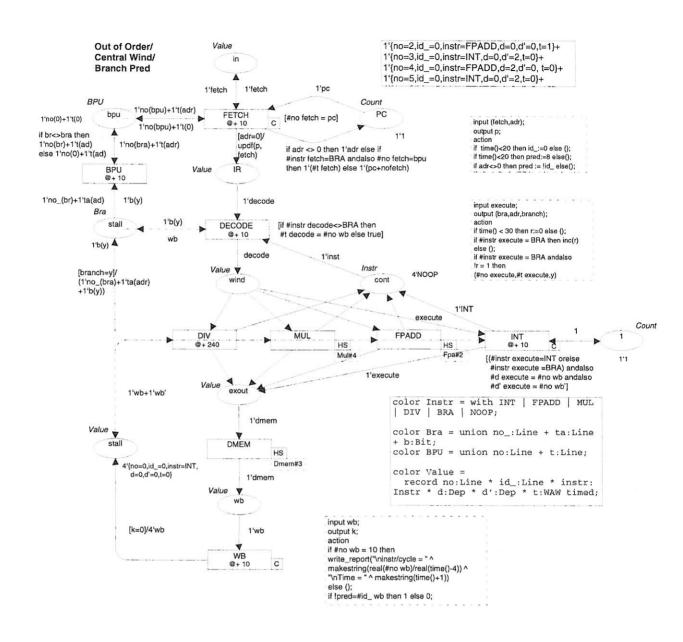

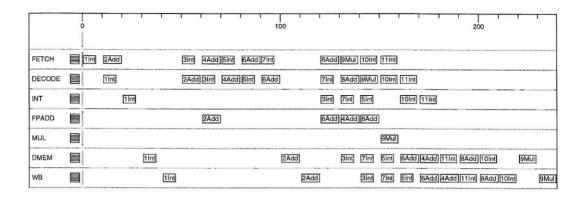

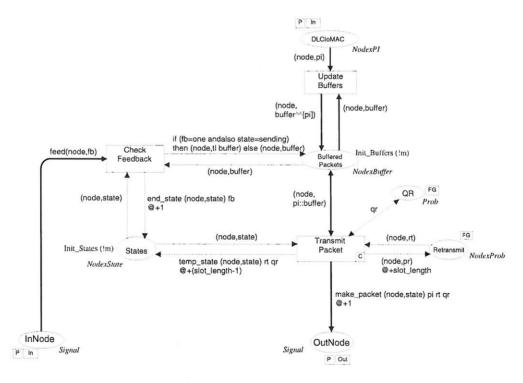

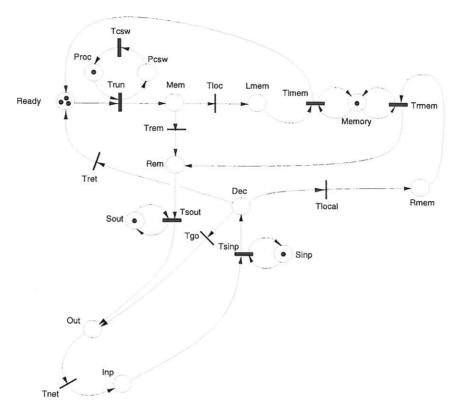

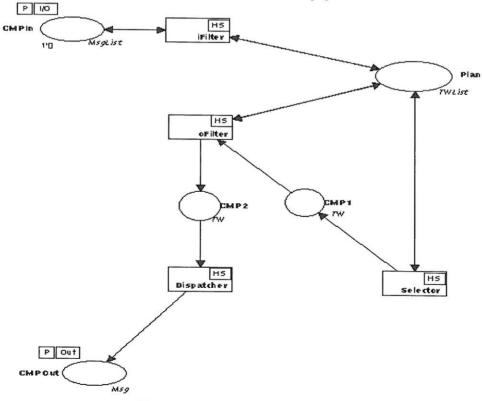

The main graphical part of the CPN model of a superscalar processor is shown in Figure 2. In the following sections we discuss individual aspects of this model.

# 4 Pipelining and In-Order Issues

The basic processor pipeline can be modelled in Design/CPN by using a set of transitions for each pipestage **FETCH**, **DECODE**, **EXECUTE** etc. The **EXECUTE** stage is further subdivided into transitions to represent execution units **INT**, **FPADD**, **MUL**, **DIV**. Individual execution units are further pipelined by using a hierarchy of pages over transitions. Places are used between transitions for storage, queues etc.

Instruction flow through functional units needs to be controlled and we need to cope with hazards in processors when they arise. In order to reference processor values at various pipestages in Design/CPN we define instruction variables for the inputs and outputs leading to and from each pipestage

Figure 2: Design/CPN model of a superscalar processor.

and execution unit transitions:

#### var fetch, decode, execute, wb, commit: Value;

Guards are used at execution unit transitions to select correct instructions for execution. For example, the following guard filters an instruction of type MUL at the multiplier unit transition:

#### $[\#instr\ execute = MUL]$

This models the correct instruction flow through execution units, but hazards also need to be modelled. Different types of hazards can be split into dependency and structural hazards. Dependency stalls are modelled by guards which check dependencies against instructions that have been written back. For example an RAW (read after write) or true dependency can be checked at a decode transition using the following guard:

#### $[\#d \ decode = \#no \ wb]$

This checks that the number of an instruction at writeback satisfies the dependency  $\mathbf{d}$  of a decoded instruction waiting to issue.

Similarly we can check for WAW (write after write) or output dependencies by using the following guard at the **DECODE** stage where **t** is defined as having the same target register as a previous instruction which has already or which is expected to be written back to the same register:

#### $[\#t \ decode = \#no \ wb]$

Note that we use t here as an instruction number and not as a register number.

Aditionally, we need to be able to cope with structural hazards. Structural hazards occur when some combination of instructions cannot be accomodated because of resource conflicts. These need to be detected and issuing instructions need to be stalled. Structural stalls can be modelled in Petrinets by using feedback from functional units to indicate that a functional unit is free.

# 5 Superscalar issues

#### 5.1 Multiple issue

Superscalar machines depend on the ability to execute multiple instructions in parallel. This is known as *Instruction Level Parallelism* [1]. Multiple issue exploits instruction level parallelism by fetching and decoding more than one instruction at a time.

The use of a fixed length instruction set enhances parallelism. For our multiple issue model we have decided to fetch four fixed length instructions

at a time. In order to do this the select Guard at **FETCH** needs to be changed to accommodate this. Now we have to fetch instructions as a block (see Subsection 8) To do this we fetch a block of four instructions defined as a record:

```

\begin{array}{l} 1'\{blockno=1,\\ b1=\{no=1,instr=INT,d=0,d'=0,t=0\},\\ b2=\{no=2,instr=INT,d=1,d'=0,t=0\},\\ b3=\{no=3,instr=FPADD,d=0,d'=2,t=0\},\\ b4=\{no=4,instr=FPADD,d=0,d'=0,t=0\} \\ \end{array}

```

The PC count must also be updated accordingly:

#### 1'(pc+nofetch)

Instructions are fetched into a queue (dispatch stack). We assume a queue of length eight split into upper and lower queues each being capable of holding a block of four instructions.

#### var bl : block;

Instructions from the lower queue are considered for decode and are replaced by the top half when all instructions from the lower queue have been decoded. In Petri nets two places separated by a transition can be used to model the two queue halves:

#### var upper, lower: block;

All instructions must be decoded and issued before another set of instructions is fetched. This is achieved by having a corresponding buffer size control node with four tokens representing the lower queue size. An up/down counter must be used to service incoming requests in order to determine the number of instructions that can be issued.

We can implement the instruction type checking and the dependencies and also the issue order provided the instructions are modelled at decode using an addition multiset:

```

1'I1 + 1'I2 + ...;

```

When the instructions are modelled like this we can relate the instructions to one another and compare them:

```

[#t I1 <> #t I2]

```

This is not simply modelled in Design/CPN because the number of instructions issued may vary. In Design/CPN it is difficult to recognise dynamically a variable number of buffer control size tokens and control a specific number of instructions waiting to be issued. Because of this an up/down counter must be used to determine how many instructions are left in the

issue window before a fixed number of requests can be serviced. This aspect is now being investigated.

#### 5.2 Out of order issue and execution

So far we have assumed a model of in order issue. This section covers out of order issue and out of order execution. To issue out of order implies using a buffer(s) or window(s) in which to store instructions waiting to execute. The buffer, called an instruction window, is placed between the instruction decoder and the functional units.

There are two ways to implement the instruction window. The first is to centralize the window. We can model this in Petri-nets by using a place after **DECODE** to mimic a central window where collected tokens in the central window represent unissued instructions. To control its size we create a corresponding buffer control size node of colour Instr and initialise it with size tokens or instructions.

# Color Instr = with INT | FPADD | MUL | DIV | NOOP; size 'NOOP;

The buffer control size node is connected to the decode transition by an arc. Each time an instruction token is issued from decode to the central window a corresponding token is removed from the buffer size control node. When size tokens are removed from the buffer size control node the central window reaches its full capacity and no more instructions can be decoded.

Another way of implementing the instruction window is to distribute individual buffers called reservation stations to each of the functional units, buffering instructions destined for a particular functional unit at the input of that functional unit. Multiple windows or reservation stations can be modelled in Petri nets by using a number of buffer places, one for each reservation station. In this case we need to control the numbers of each instruction type entering each buffer place.

To control the size of the reservation stations we make use of the corresponding size control node of colour **Instr** as for the central window but this time initialise it with a multiset which corresponds to the individual sizes of each reservation station:

#### (1) 2'INT + 2'FPADD + 2'MUL + 2'DIV

Every time an **INT** instruction is issued from the decode stage a Guard is used to remove the corresponding type of instruction from the buffer size control node.

An arc inscription selector is used from decode to each reservation station

place to control the instruction selected. For example, for the arc leading from the decode transition to the reservation station for the **INT** unit we have the following arc inscription:

```

[\#instr\ decode = INT]/1'decode

```

If the instruction of type INT is taken from 1) the corresponding multiset will result in the buffer size control node:

#### (2) 1'INT + 2'FPADD + 2'MUL + 2'DIV

When two **INT** tokens are removed from the buffer size control node this is equivalent to the reservation station at the **INT** execution unit being full.

# 6 Branch prediction

Branch prediction can reduce the average branch delay by predicting the outcomes of branches during instruction fetching. Branch prediction makes use of a Branch Prediction Unit (BPU) for building up a database of speculative branch information.

Branch instructions are represented in colour using the following format:

```

color Value = record

no: Line *

BRA: Instr *

d: Dep *

l: loop *

```

where  ${\bf d}$  represents a dependency,  ${\bf l}$  indicates whether the instruction will loop and the number of times for the loop is predetermined and  ${\bf t}$  represents

the correct target of the branch instruction which is also predetermined by the user.

t: Target timed;

For Branch Prediction we assume a branch prediction unit using a target buffer which dynamically collects information about the most recently executed branches. The data structure for the BPU is defined as follows: color BPU = union no:Line + t:Line;

**FETCH** checks the instruction against the target buffer to see if their is a predetermined branch for that branch **no:Line**. If the fetched instruction is a branch the branch target buffer indicates the predicted outcome using the target address **t:Line**.

In the case of a misprediction two values are sent back to the BPU, a branch instruction number defined as the first part of the union:  $no_{-}(bra)$ , and the correct target defined as the second part of the union: ta(adr). This is achieved with the following arc inscription flowing from the corresponding execution unit to the BPU:

```

[branch=y]/(1'no_(bra)+1'ta(adr)+1'b(y))

```

This transfers a number for the branch instruction **no\_(bra)** and a corresponding BPU update prediction target address **ta(adr)**. The target for a particular address is checked for by the **FETCH** with the following arc inscription:

# 7 Recovery

Recovery is a process which cancels the effects of instructions that were issued under false assumptions using speculative execution. In asynchronous circuits, recovery from an incorrect branch is accomplished by assigning a tag or colour to each instruction (see e.g., [5]). When a branch is encountered the tag or colour is changed and instructions which do not have the current tag are considered invalid and are terminated further down the pipeline. For speculation it is assumed that a tag needs to cover a range of values between branches and an integer tag is proposed so that each instruction between a branch is represented by a unique id. An additional record value is provided for this in the instruction definition:

```

color Value = record

no: Line *

id_: Count *

instr: Instr *

d: Dep *

d': Dep *

t: Target timed;

```

The value of the **id**\_is changed for each instruction by incrementing it modulo some limit over which the range of tags are defined. Each time a branch instruction is fetched the value of **id**\_ must be changed and a list created of all the invalid **id**\_ values built up from an incorrect speculation.

To make the recovery process more efficient instructions could be checked and eliminated earlier than the writeback stage to speed up recovery. This is done by using a selector at certain stages to determine if the instruction is valid or invalid:

[instructionvalid=0]/1'execute

#### 8 Caches

While modelling caches we assume that direct cache modelling is being used. In Design/CPN an instruction cache can be modelled by having an extra **CACHE** place between the instruction memory and the processor. An extra **READ** transition is also inserted after the cache place which models a read access made by the processor to the cache for an instruction. The original **FETCH** now becomes a fetch access to memory to load a block into the **CACHE** place.

When modelling caches we need to be able to reference values in the cache. In order to do this tags need to be added to the instructions to model their relative cache positions. We have done this by defining a new record which defines a block of instructions and adding extra fields called cachetag and cacheblock:

```

color Block = record ct:Line * cb:Line * b1:Value * b2:Value

b3:Value * b4:Value;

```

```

\begin{cases} ct=0, cb=0, \\ b1=\{no=0, id\_=0, instr=NOOP, d=0, d'=0, t=0\}, \\ b2=\{no=0, id\_=0, instr=NOOP, d=0, d'=0, t=0\}, \\ b3=\{no=0, id\_=0, instr=NOOP, d=0, d'=0, t=0\}, \\ b4=\{no=0, id\_=0, instr=NOOP, d=0, d'=0, t=0\} \end{cases}

```

The cachetag is used to specify the set of memory blocks which can be mapped to a specific cacheblock. The cachetag value is calculated as the upper part of the pc address. The PC address is formatted as follows: pcaddr = cachetagbits;cacheaddrbits;offsetbits

Here we assume instructions have a fixed length (32 bits). The cachetag for an instruction block is calculated by dividing its instruction address by 2<sup>cacheaddrbits+offsetbits</sup> where cacheaddrbits are used to specify the cacheblock address, and offsetbits are used to specify the offset of an instruction within a cacheblock.

Initially all the instructions in the cache are set to **NOOP** and their cachetags set to zero, **cachetag=0**.

To access a cache address at READ we select the cacheblock address by using a transition guard:

$[\#cacheblockread = ((pcaddrnoDIV2^{offsetbits})mod2^{cacheaddrbits+offsetbits})]$

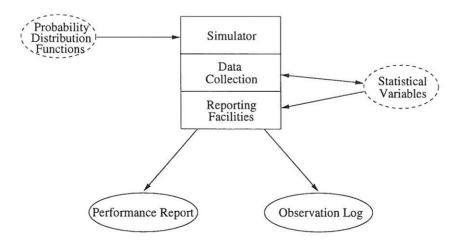

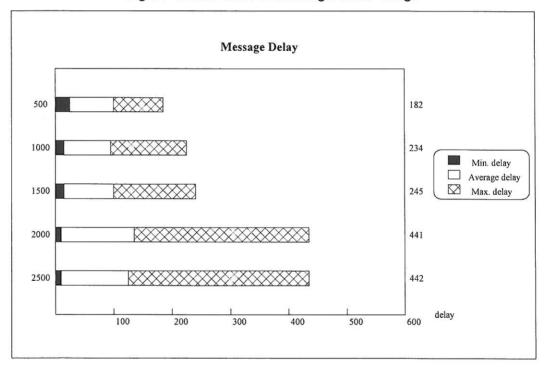

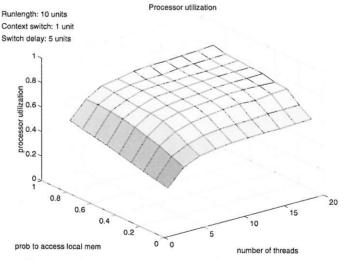

## 9 Preliminary simulation results

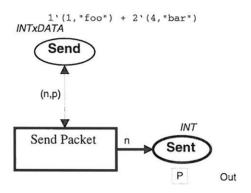

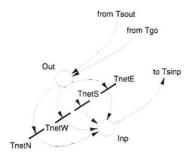

Design/CPN simulation output consists of a large text file. In order to display the timing results in a more suitable format, a graphical tool, written in Tcl/Tk, was written to display the timing results of the simulation in a more suitable format. A software filter processes the output from Design/CPN and drives the Tcl/Tk display.

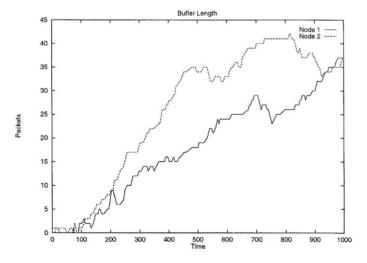

Figure 3 shows the schedule obtained for a set of instructions which have been simulated using the model shown in Figure 2. In the schedule, the second instruction has been delayed from executing by a Write-After-Write dependency on the first instruction. The second instruction then proceeds to execute, but the subsequent instructions which have a Read-After-Write dependency on the second instruction are delayed, and accumulate in the central window before the dependency on the second instruction has been resolved. Subsequently, instructions are shifted out of the central window and execute in parallel. This allows instructions 6,4 and 8 to enter the FPADD pipestage (4 stages) and execute in parallel. It can be seen from the schedule that instructions execute out of order and are written back out of order.

#### 10 Discussion

The use of Design/CPN on a complex processor model shows that the tool has many obvious strengths but also weaknesses.

The strength of Design/CPN modelling lies in its use of colours and datatypes which can be used for modelling basic processor instructions and also more complex memory types such as caches. Because of its typing,

Figure 3: Instruction timing diagram.

Design/CPN can be used to capture dataflow adequately using arc and guard expressions.

Pipelines are easily captured using a sequence of transitions and places. Hierarchy is expressed easily by using pages over transitions.

Dependency hazards can be easily modelled by placing guards at execution units. Structural hazards are easily modelled using feedback. Register locking can also be modelled.

In order and out of order issue modelling is easily captured. The natural flow in Design/CPN is out of order or arbitrary but this can be changed to in order by using Guards. Design/CPN is also good at modelling buffers, and therefore reservation stations can be easily modelled.

Multiple issue can be modelled but not without difficulty. This is because it is difficult to express dynamically the relationship between token flow expressions on different arcs. Compensatory techniques have to be found to overcome this such as counters to recognise how many tokens can be allowed to pass over arcs.

Branch prediction can be modelled. However, there is a possibility of arbitration occurring between the fetch unit and the branch prediction unit. Arbitration is not easily simulated, as it has no priority of choice and cannot make a decision about the correct flow of data. Although the simulator tends to correct this, it is not an adequate solution at the moment. This requires further investigation.

Recovery is difficult to model, but it is naturally difficult to model in

asynchronous designs. The techniques to overcome this are based on assigning tags to instructions, and terminating instructions when they become invalid. The problem with this is that more than one tag needs to be used for out of order issue.

#### 11 Conclusions

We have described the main aspects of our approach to the modelling of a superscalar processor with Coloured Petri nets, and some preliminary results. The model is successfully run using the Design/CPN software. Typical speed of simulation is about 3000 instructions per minute under Linux on a 166Mz PC. Design/CPN provides the designer of a real-time system with both qualitative analysis of reachable states and analysis of timing characteristics, such as worst case execution for a block of instructions. A number of modelling issues has been revealed that require further investigation of the descriptive power of Design/CPN. Further tool development should allow extraction of timing parameters from Design/CPN output files, and their display using graphical tools not available within the Design/CPN environment.

# 12 Acknowledgements

This work is supported by EPSRC grant GR/L28098 (project TIMBRE) and Esprit LTR Project 20072(DeVa). The authors also wish to thank the referees for helpful comments on the paper.

#### References

- [1] D.K. Arvind and V.E.F. Rebello. Instruction-level parallelism in asynchronous processor architectures. Proceedings of the Third Int. Workshop on Algorithms and Parallel VLSI Architectures, M. Moonen and F. Catthoor (Eds), Leuven, Belgium, August 1994, Elsevier Science Publishers, pp. 203–215.

- [2] J.B. Dennis. Modular, Asynchronous Control Structures for a High Performance Processor. Proceedings of Project MAC Conference on Concurrent Systems and Parallel Computation, June 1970, pp. 55-92.

- [3] K. Jensen. Coloured Petri Nets. Basic concepts, analysis methods and practical use. EATCS Monographs on Theoretical Computer Science, Springer-Verlag 1992.

- [4] A. Semenov, A.M. Koelmans, L. Lloyd, and A. Yakovlev. Designing an asynchronous processor using Petri nets. *IEEE Micro*, 17(2):54–64, March 1997.

- [5] N.C. Paver. The design and implementation of an asynchronous microprocessor. Ph.D. Thesis, University of Manchester, 1994.

- [6] R.R. Razouk. The Use of Petri Nets for Modeling Pipelined Processors. Technical Report 87–29, University of California, Department of Information and Computer Science, 1987.

# ALPiNe: A Hardware Computing Platform for High-Level Petri Nets

S. Bulach, H. Baur, H.-J. Pfleiderer, Z. Kucerovsky\*

Department of Microelectronics, University of Ulm, Ulm, D-89069, Germany

\*Department of Electrical & Computer Engineering, University of Western Ontario London, Ontario, N6A 5B9, Canada

May 5, 1998

Abstract: A motivation for the design of a novel hardware platform for processing algorithms based on High-Level Petri Nets is presented. ALPiNe (Asynchronous High-Level Petri Net) processor is aimed at embedded discrete-event control applications and is characterized by its natural incorporation of external stimuli into the computation flow. The processor consists of two layers of hardware: one for determining when and which computations will take place, and another for effectively performing the actual computations. A hybrid architecture and hardware organization are described in detail. The process of software development is presented, augmented with an illustrative example. In conclusion, comments on advantages and possible future implementations are made.

#### Introduction

The last thirty five years have demonstrated that Petri Nets (PN) have the inherent ability to survive, and not only to survive. The rate at which this concept was applied, modified and extended is perhaps analogous to the exponential PN state explosion phenomenon. One such extended version of a Petri Net is known as a Coloured Petri Net (CPN) [KJ96]. The CPNs could be classified as High-Level PNs, being more abstract than their predecessors. In addition to allowing abstract token types they may also incorporate hierarchical capabilities and time extensions [WA94]. Several commercially available software packages support efficient creation, simulation and analysis of algorithms based on CPNs [AW91]. This paper deals mainly with the Design/CPN [MS93] package and its application to modelling complex discrete-event control systems.

Due to their flexibility Petri Nets have been successfully applied to a wide range of problems [TM89], and were found to be best pertinent in performance evaluation and in the design of communication protocols. In general, PNs are well suited for modelling and analysis of systems that may possess concurrent, distributed, parallel, event-driven, asynchronous, reactive and non-deterministic qualities. In yet another dimension, Petri Nets can be used from gate-level hardware design, through register-transfer level (RTL) modelling, all the way to the design of complex software systems [JP81]. However, it should be noted that because Petri Nets have well defined static and dynamic properties they do well in

modelling processes, systems and algorithms that in some sense exhibit analogous characteristics. In other words, it is not very efficient to model spherical objects using triangles!

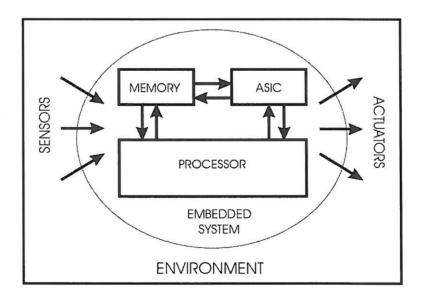

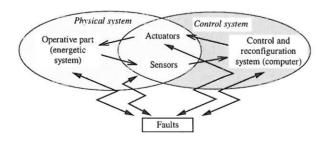

A very broad class of systems that Petri Nets handle well is known as *reactive systems* [BM91]. A reactive system, informally defined, is said to have an on-going interaction with its environment. It receives the input stimuli from sensors, processes them, communicates back to the environment through actuators, and keeps track of the state [HP85]. Furthermore, embedded systems could be viewed as reactive systems that must satisfy hardware constraints, whereas real-time systems are reactive systems which must also satisfy timing constraints [MP96]. Design, verification and efficient implementation of reactive (embedded and/or real-time) systems still remains an active research field.

At the gate-level, Petri Nets could be used for both combinational and sequential circuit design, especially when gate delays are taken into account. Asynchronous (operating without a clock) sequential circuits are particularly well suited for modelling with PNs, although attempts have been made to extend PNs to handle synchronous sequential circuits, or even mixed asynchronous-synchronous systems [TT97]. This is mainly due to the asynchronous event-driven nature of processes that PNs represent. Note that asynchronous sequential circuits represent simplest reactive processes. Recently, PN based methods were developed which allow automatic synthesis of asynchronous circuits based on Signal Transition Graphs (derivative of marked PN), or signal switching specifications [JC97]. However, this methodology is restricted to the relatively small controller circuits. There is also ongoing research at utilizing PNs at a register-transfer level for system verification and synthesis [SK97]. However, both gate-level and RTL represent so-called direct solution or implementation, where a given algorithm is hardwired and is intended for a specific application, as is the case, for example, in the ASIC (Application Specific Integrated Circuit) design. Another type of solution is known as indirect and involves use of programmable devices, such as microprocessors and processor-based systems.

Figure 1. A Simplified Structural View of an Embedded System.

An indirect solution is essentially a software design because the hardware computing resources are provided and are fixed, while the algorithm resides in memory. A complex reactive system would normally contain a processor which has I/O capabilities in order to

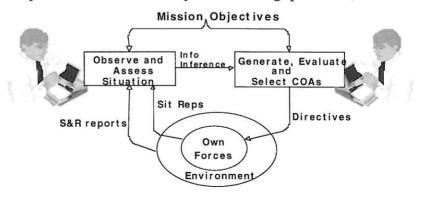

communicate with the environment through sensors and actuators. A simplified structural view of such a system is given in Figure 1 [GD94]. Much attention has been given to the design of complex software systems using High-Level Petri Net concepts (for examples, refer to [TH92], [RS96]). However, most of the efforts are directed at employing commercially available processors, thus shifting the focus to the efficient computing strategy given the computing resources and I/O capabilities. The weakness of this approach is that while reactive systems, or in other words, most of the embedded systems, are intended to be reactive or event-driven, commercially available processors are predominantly of the control flow architecture. They are excellent number crunchers but inefficient communicators. Thus, processing cores are normally surrounded by a plethora of peripherals to enable interaction with the environment. However, the overall architecture still remains control driven.

In system design it is often the case that the system description at the early stage of the design is done in dataflow, functional, or some other unconventional language. However, the final implementation is forced to be translated into the procedural language equivalent and then compiled into the target code. The point is that even if the desired programmed functionality of a software system is reactive, event or data driven, the final implementation is done on a hardware platform that is strongly control driven. Could these inefficiencies be addressed at an architectural level?

#### **ALPiNe Architecture**

The universality of Petri Nets could be attributed to their flexibility in ascribing a meaning to the concept of tokens, places and transitions. For different applications both places and transitions may mean different things. Some typical interpretations are given in Table 1 [TM89].

| Input Places      | Transitions        | Output Places      |  |

|-------------------|--------------------|--------------------|--|

| Preconditions     | Event              | Postconditions     |  |

| Input Data        | Computational Step | Output Data        |  |

| Input Signals     | Signal Processing  | Output Signals     |  |

| Resources Needed  | Task or Job        | Resources Released |  |

| Condition(s)      | Clause in logic    | Conclusion(s)      |  |

| Buffers Processor |                    | Buffers            |  |

Table 1. Possible Interpretations of Transitions and Places

Note that the second interpretation with input and output data, and a computational step could be well applied to reactive systems. That is to say that a computational step is invoked only when the required input data is present. This principle is reminiscent of the dataflow architecture with a data driven computing organization [TB82], where the computational step is executed once the necessary data becomes available. The computational step itself may represent the execution of one or more instructions, or in other words, a subroutine of arbitrary size, which is concerned with pure computations.

The above observation leads to the conception of a hybrid architecture comprising both data flow and control flow characteristics. Thus, data flow principle is employed to

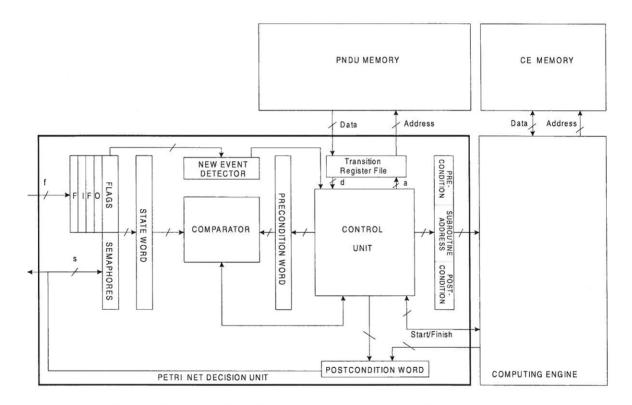

determine whether or not (and which) computational step is invoked, while control flow principle is used to efficiently perform number crunching once it has been determined which step to execute. These architectural principles are realized in the proposed ALPiNe (Asynchronous High-Level Petri Net) processor. ALPiNe processor has two primary modules: a Petri Net Decision Unit (PNDU) and a Computing Engine (CE). The PNDU module is responsible for making decisions regarding the PN structure, such as determining which transition fires based on the Precondition, or a special condition that must be satisfied for a transition execution to initiate. The PNDU processes its own code, and coding is described in the following section. The CE module is a conventional processor core, optimized for logic, arithmetic and bit manipulation instructions. The CE module also has its own code. Detailed software and hardware organization of the ALPiNe hybrid architecture is presented below.

#### **ALPiNe Software**

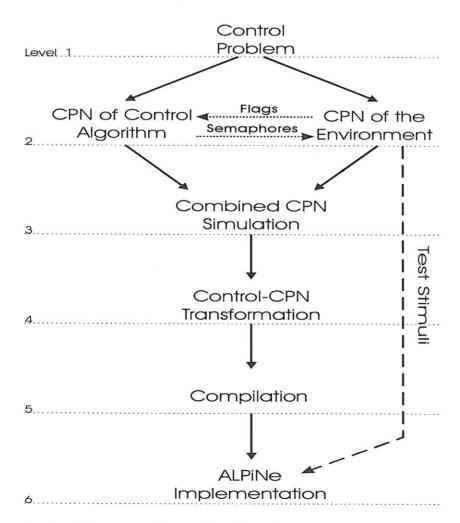

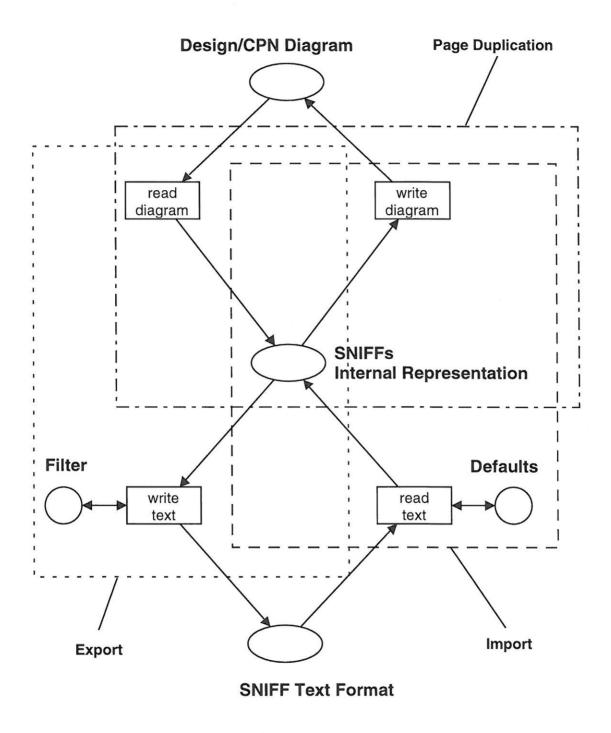

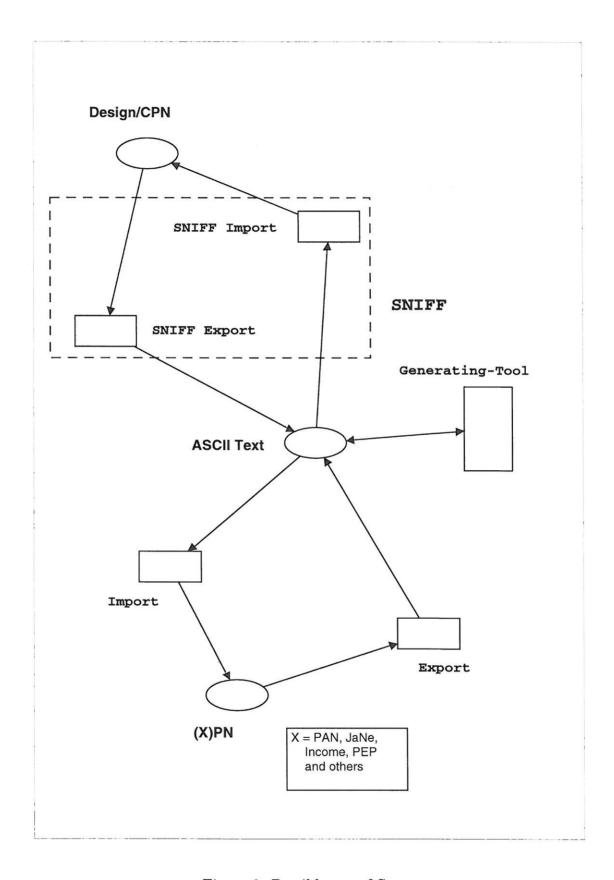

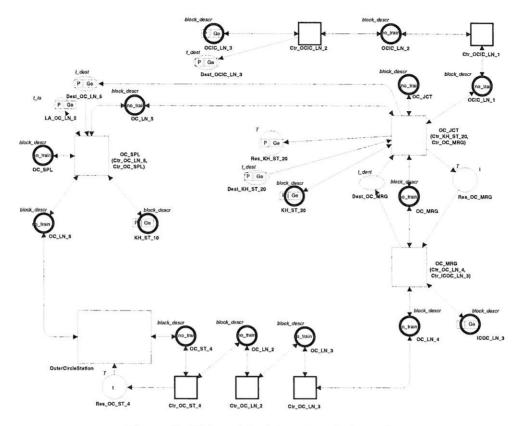

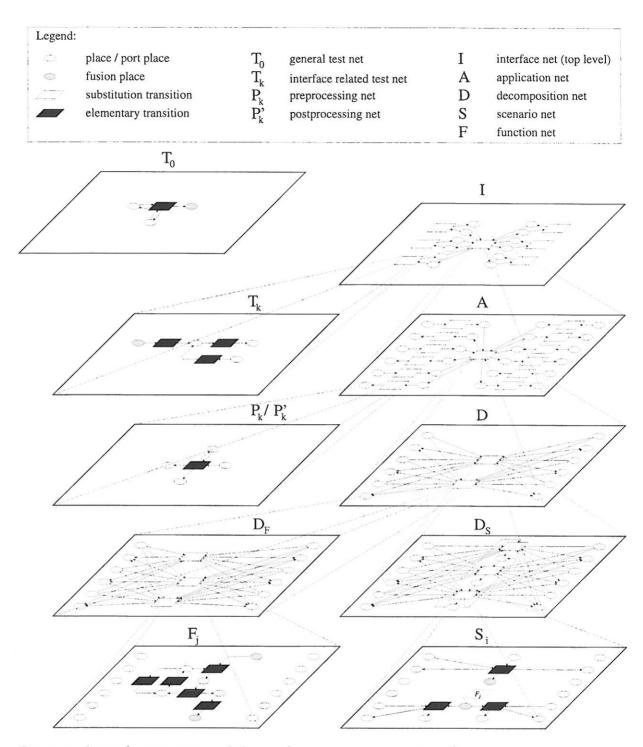

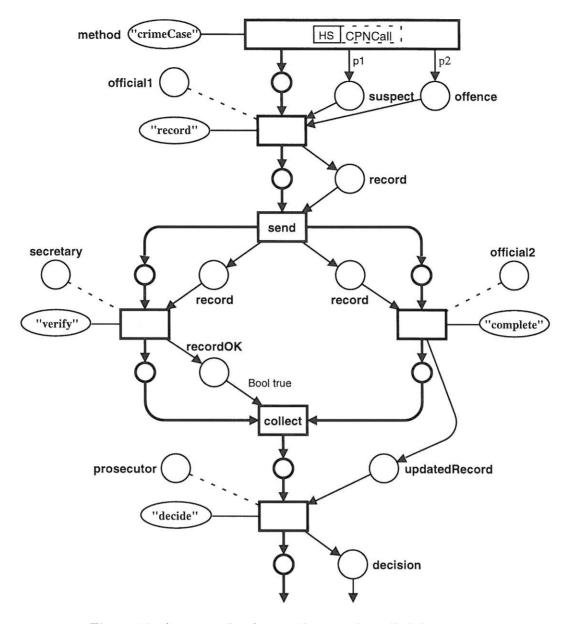

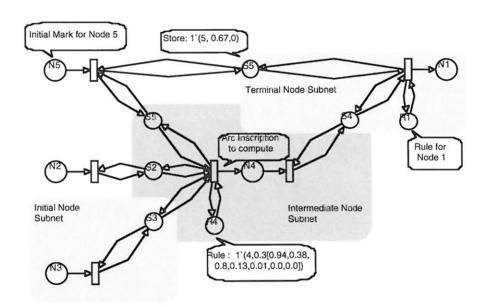

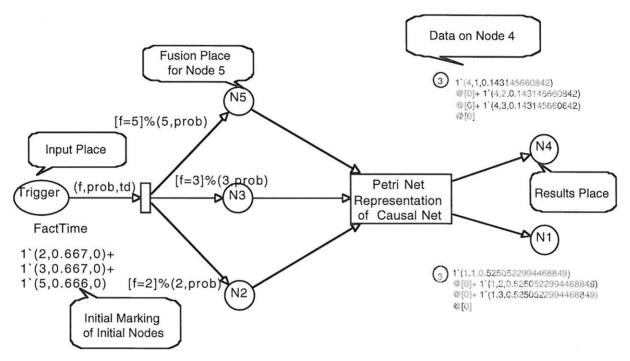

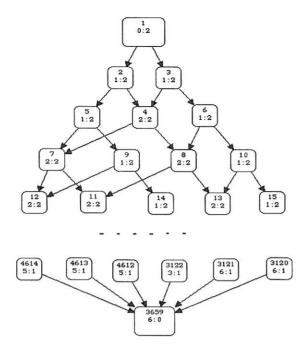

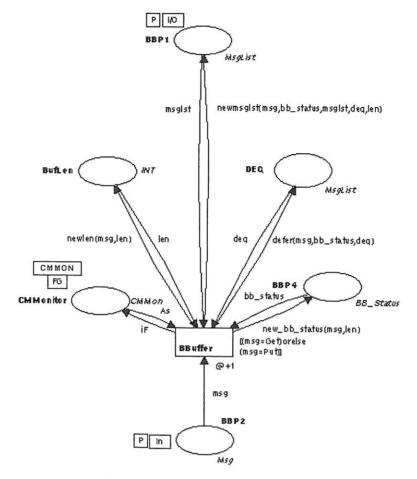

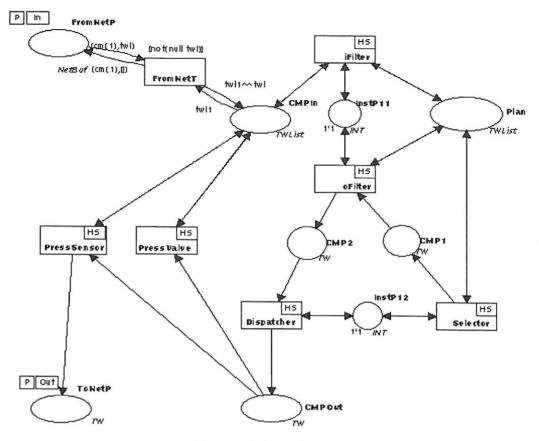

First of all, the design flow must be thoroughly examined in order to see how High-Level Coloured Petri Nets (in particular, developed with Design/CPN) could be processed by the ALPiNe processor. Clearly, the CPNs manipulated by the Design/CPN package could not be implemented directly on the ALPiNe processor. They are simply too complex, have abstract data types, and the code size is most likely too large. The design flow, shown in Figure 2, should help to see the role of the ALPiNe with respect to CPNs, as well as what type of CPNs could be processed by this processor.

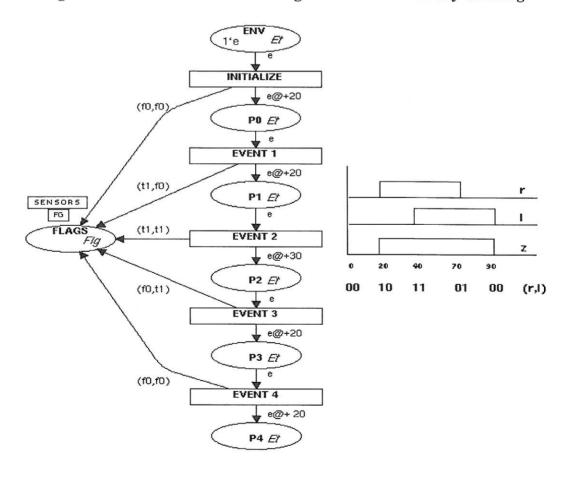

Figure 2. Design Flow for a Control Problem Solution Using the Coloured Petri Nets.

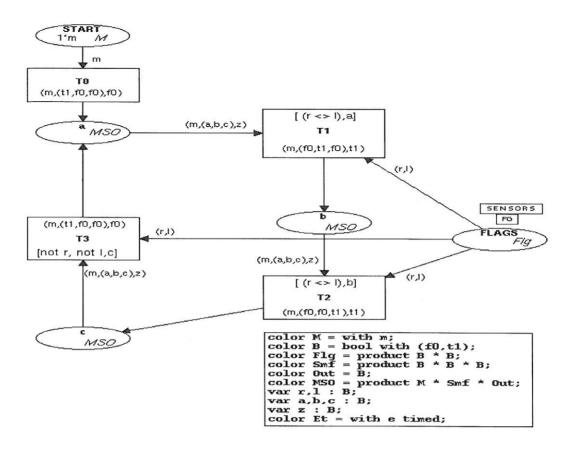

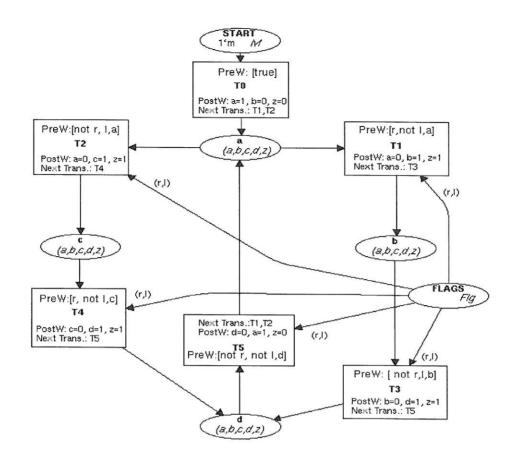

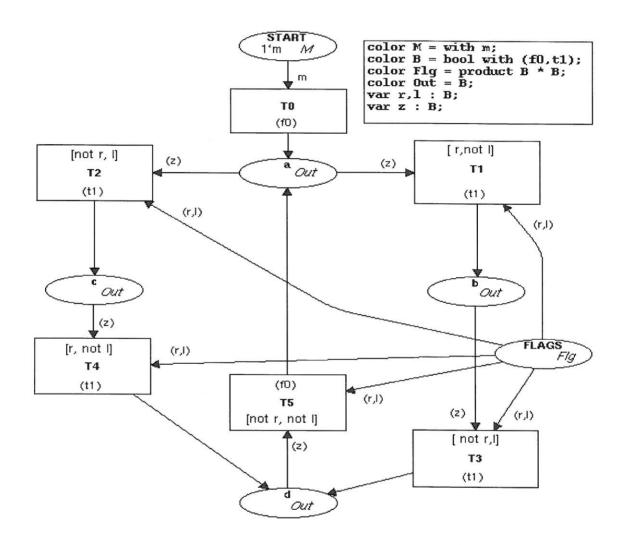

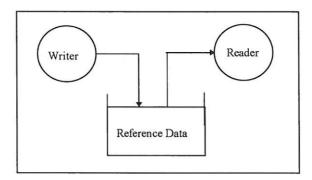

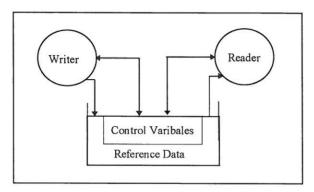

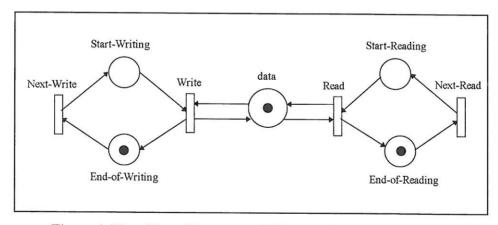

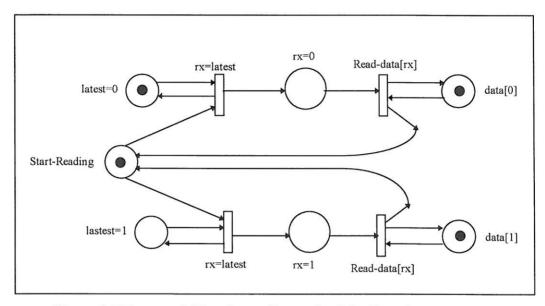

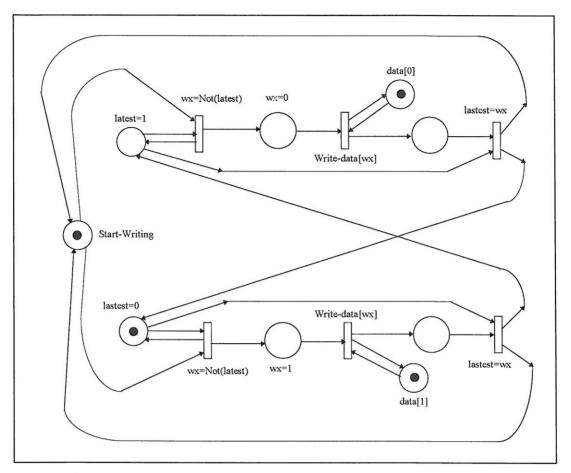

Given a control problem, a solution, which involves the CPN of the control algorithm and the CPN of the environment, is developed with the Design/CPN. In this approach, the environment CPN communicates to the control CPN through Flags, while the control CPN uses Semaphores to signal its state to the environment. This method allows to model the ongoing interactions between the two. The combined model can be simulated and formally analyzed to verify the correctness of the algorithm. If the control model is satisfactory, it must be transformed from its high-level CPN (level 2,3) to the intermediate-level CPN (level 4). The intermediate-level CPN must be of the form which would allow compilation into the ALPiNe machine code. Thus, the high-level CPN (level 2, 3) is in the format understood by the Design/CPN. The intermediate-level CPN must be in the format understood by the compiler. The rules of transformation and compilation must be clearly defined and are based, of course, on the intermediate-level CPN. The important issue is to optimally specify the intermediate-level CPN which will serve as a bridge between the two different worlds of high-level CPN software (Design/CPN) and the hardware (ALPiNe). Furthermore, the intermediate CPN must deal with real-world binary variables which are digital signals on the wires and processor input pins.

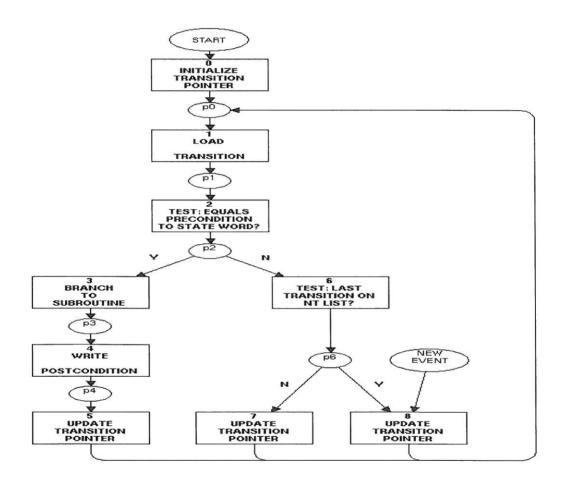

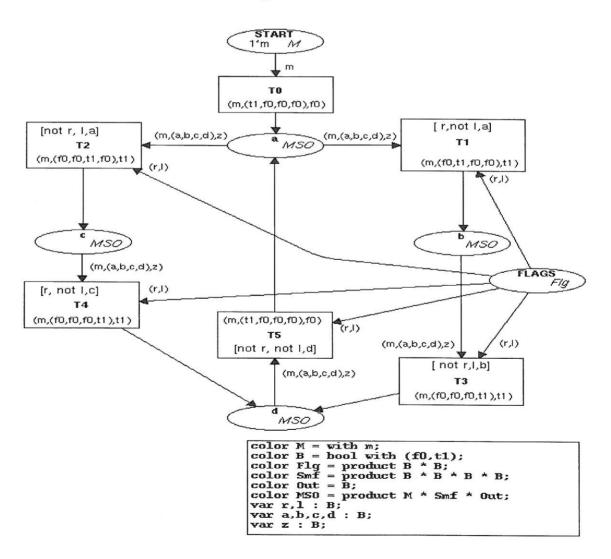

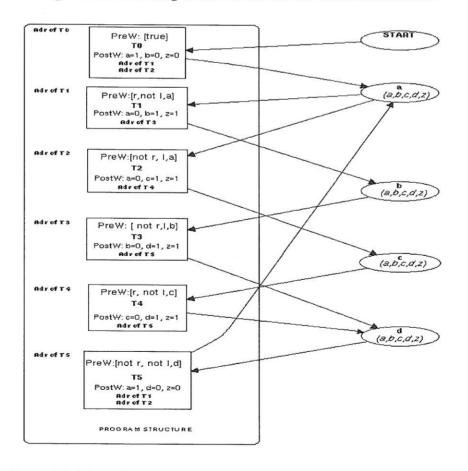

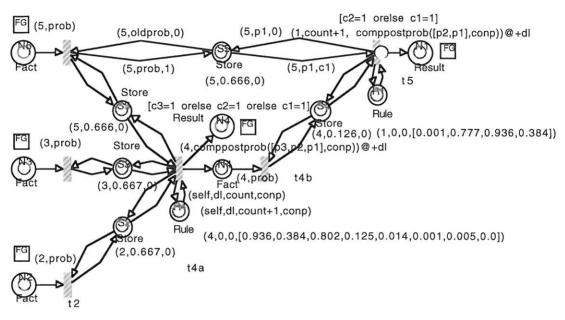

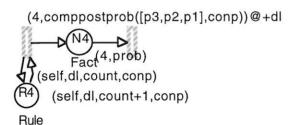

It was chosen that the current version of ALPiNe would handle problems modelled with the CPNs of the Finite State Machine (FSM) subclass. That is, at any given time the processor could only be found in one state (or place). This means that one or more transitions could be enabled at the same time. However, the execution algorithms and the CPN structure ensures that only one will fire, remove the enabling token from the input place and produce a token for a corresponding output place. The FSM restriction on CPNs is achieved by allowing at most one input and output place from any given transition. This restriction does not apply to special Flag and Semaphore places.

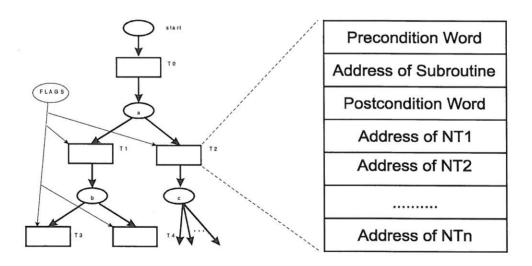

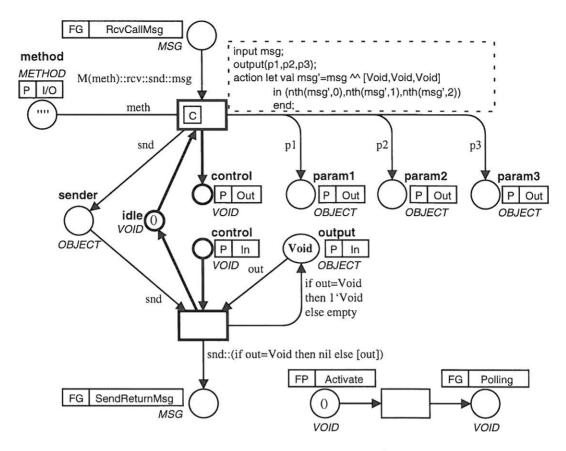

Figure 3. A General Transition Coding Format

The program to be executed on the ALPiNe processor (machine code) mimics the intermediate-level CPN and consists of a list of transitions. Each transition is coded according to the general pattern shown in Figure 3. It contains a Precondition Word, an Address of a Subroutine, a Postcondition Word and a list of addresses of Next Transitions (pointers). Note that places do not appear explicitly in the code. The concept of places is dissolved by the presence of preconditions, postconditions and pointers; these three combined precisely determine the unique state of the processor at any given time. General rules of converting a Design/CPN executable intermediate-level CPN into the ALPiNe code are given below.

The principal components of a CP net are: Data, Places, Transitions, Arcs, Input Arc Inscriptions, Guards, and Output Arc Inscriptions [MS93]. A full translation of the CP Net into the ALPiNe machine code requires the specification of conversion for each of these components.

CPN Data: Data objects are known as tokens, while datatypes are called colorsets. The high-level CPN has fairly complex tokens and colorsets. The intermediate CPN, on the other hand, must reflect hardware dependence in that all (or most of the) tokens are binary variables. These binary objects could be combined into different binary multisets such as Flags (reflect the current state of the environment) and Semaphores (reflect the current state of the system). The size of Flags and Semaphore multisets is determined by the width of their respective registers (Figure 4). This sets the upper boundary on the number of encoded states. Refer to the Railroad Crossing example presented below to see how these multisets could be arranged.

**Places**: According to the Design/CPN definition, places are locations for holding data. For high-level CPNs places are important components of the algorithm. They represent the state of the modelled system. At the machine code level, places have no real interpretation, as only transitions are encoded as a program. Note, this does not mean that the modelled system becomes stateless! The state may be encoded with Semaphore tokens as required.

**Transitions**: In high-level CPNs these are defined as activities that transform data. At the machine code level these are primary elements of the program. They specify what computational step (i.e. subroutine) is to be executed once the transition is enabled. In addition, at the intermediate-level transitions also encode Preconditions and Postconditions. This procedure could be observed again from the Railroad Example.

Input Arc Inscriptions (IAI): These specify the data that must exist for an activity to occur.

Guards: Define conditions that must be true for an activity to occur. In terms of the present ALPiNe encoding for the intermediate-level CPN, both IAI and Guards form a Precondition Word. Ideally, the IAI should indicate which tokens (or binary elements) are important to test in the Precondition. Guard specifies the binary AND operation performed on these variables. If the outcome is TRUE, the transition will fire.

Output Arc Inscriptions: Specify data that will be produced if an activity occurs. This CPN component is encoded into the Postcondition Word, in which binary variables of the Semaphore multiset (current state indicators) are set or cleared upon requirements.

Again, refer to the Railroad Crossing Example to observe the relationship between the Design/CPN components and the corresponding elements of the ALPiNe encoding, i.e. Preconditions, Postconditions and Transitions, as shown in Figures 9, 10 and 11. The overall PNDU code structure has the following components: Precondition Word, Address of Subroutine, Postcondition Word, Number of Next Transitions (NNT) indicator, and the actual addresses of Next Transitions, NTA1, NTA2,..., NTAn. Thus, the PNDU has a variable length instruction format. This means that the information about the transition length must be explicitly encoded. The NNT field contains the explicit number of next transitions

The execution of a subroutine is the task of the CE module. The encoding of its logic and arithmetic instructions is done according to the principles described in [HP90].

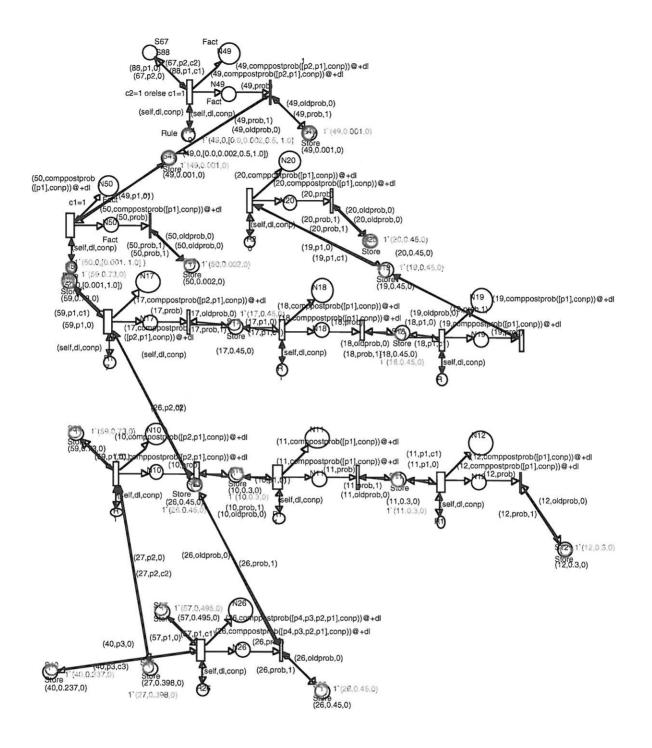

#### **ALPiNe Hardware**

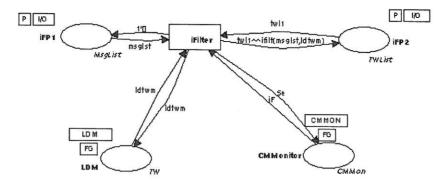

As mentioned above, ALPiNe consists of two modules, each optimized for its own unique function. The block diagram of the ALPiNe processor is shown in Figure 4. Both PNDU and CE have their dedicated memory, with their own data and address buses. This ensures optimum concurrency of the operation.

The PNDU is responsible for processing PN structure related information. It receives new information from the environment through the FLAGS pins. Every new event or change on FLAGS is registered and queued in the FIFO block. At the same time New Event Detector produces a signal to indicate that the new event has been detected. The PNDU communicates to the outside world through Semaphores. The Semaphores are combined with "oldest" Flags to form a State Word. The Comparator checks for equivalence between the State Word and the Precondition Word. A Transition Register File is where Transition information is temporarily stored while a comparison is performed. The Precondition Word, Subroutine Address and the Postcondition Word of the currently executed transition become available to the Computing Engine. The CE also receives a prompting signal to start processing a subroutine and upon execution indicates that it is finished. It has an option of altering the Postcondition Word based on the results of computation.

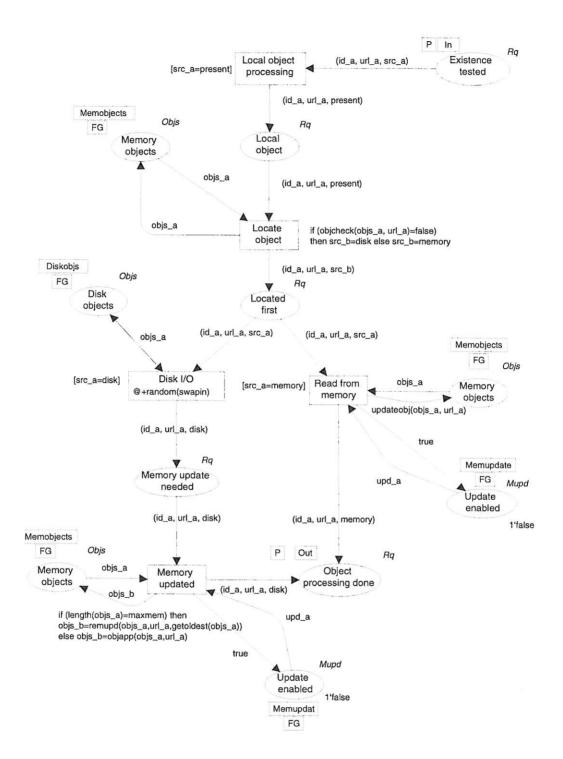

Figure 4. Simplified Block Diagram of the ALPiNe Processor.