# SYSTEM MODELLING

A methodology for describing the structure of complex Software, Firmware, and Hardware systems consisting of independent process components.

by Ib Holm Sørensen

DAIMI PB-87 March 1978

Institute of Mathematics University of Aarhus

DEPARTMENT OF COMPUTER SCIENCE

Ny Munkegade - 8000 Aarhus C - Denmark

Phone 06-128355

# Table of Contents

| 1. | Introduction                                 | 1  |

|----|----------------------------------------------|----|

|    | 1.1 The Outline of the Thesis                | 2  |

| 2. | The System Modelling Language                | 5  |

|    | 2.1 The Process Declaration                  | 6  |

|    | 2.2 The Mailbox Declaration                  | 6  |

|    | 2.3 Indivisibility                           | 7  |

| 3, | The Pictorial Representation                 | 11 |

|    | 3.1 The Properties of the Representation     | 11 |

|    | 3.2 The Elements of the Representation       | 13 |

|    | 3.3 Elementary Behaviour Statements          | 15 |

|    | 3.4 Sharing and Communication                | 23 |

|    | 3.5 Parallelism and Concurrency              | 28 |

|    | 3.6 Combined Constructs                      | 29 |

|    | 3.7 Remarks on Design Tools                  | 38 |

| 4. | An Analysis of a Disk Controller             | 41 |

|    | 4.1. The Configuration.                      | 41 |

|    | 4.2. Disk Characteristics.                   | 45 |

|    | 4.3. The Levels of the Disc-Controller.      | 45 |

|    | 4.4. Relevance                               | 49 |

| 5. | The Hardware Level                           | 51 |

|    | 5.1 The Elements of the Supporting Hardware. | 51 |

|    | 5.2 The Memory Bus Control Process           | 60 |

## Preface

This is the author's master's degree dissertation.

It is felt that a short outline of its history will prove useful to the reader.

Initially, the author chose to conduct a research project consisting of the design of a disk channel prosessor for the RIKKE experimental computer system. The actual implementation of the device was to be the subject of a different project. He subsequently realised that -short of implementing his design- there was no obvious way for him to document his design in sufficient comprehensible detail. He studied various known techniques, but found them unsatisfactory.

Additional research on his part resulted in the development of the Pictorial Representation presented hereby. Because of the newness of his notation, it itself needed extensive description. Thus the report turned out to be dominated by the notation which initially was considered as only peripheral to the documentation of the autor's disk channel prosessor design.

As sometimes happens in scientific research, what was first seen as a peripheral aspect was later recognised to be of dominating importance. Therefore the author chose to shift this dissertation's point of emphasis to the description tool, presenting the disk channel processor as a mere example in the use of the notation, where any other example could have done just as well. Thus his technical contribution in developing an original disk channel prosessor could have gone unnoticed, and needs to be pointed out in this preface.

Peter Kornerup Mike Spier

# Acknowledgements

I would like to thank my thesis supervisers Peter Kornerup and Michael J. Spier for their guidance in research, their editing, proofreading and general assistance during the preparation of this thesis.

It should also be mentioned, that this work is a consequence of Peter Kornerup's, Kurt Andersen's and Bruce Shriver's pioneering research leading to the RIKKE/MATHILDA system.

Thanks are due to Nigel Derrett for his constructive criticisms, to Svend-Erik Clausen for typing part of this paper, and to the members of the Technical Staff, who have introduced me to the world of Hardware.

Ib Holm Sørensen

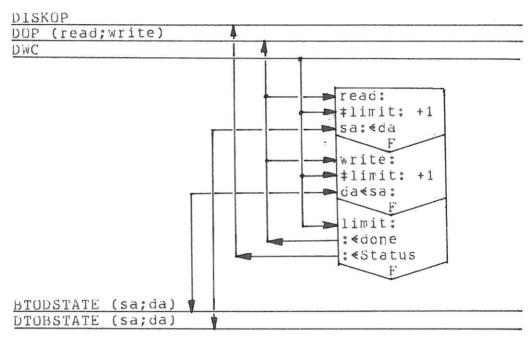

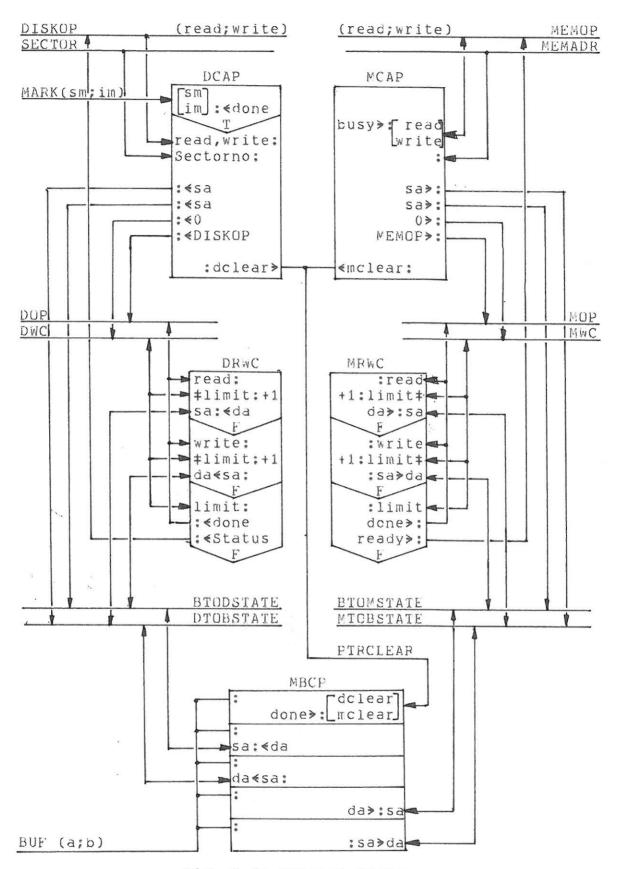

|            | 5.3  | The Disk Read/Write Control Process     | 63  |

|------------|------|-----------------------------------------|-----|

|            | 5.4  | The Memory Read/Write Control Process   | 65  |

|            | 5,5  | Disk and Memory Channel Administrators. | 66  |

|            | 5.6  | The Disk and Memory Transfer Processes  | 69  |

|            | 5.7  | Arm Positioning Process.                | 69  |

|            | 5.8  | Disk Status Monitor Process.            | 70  |

| 6.         | The  | Firmware Level                          | 73  |

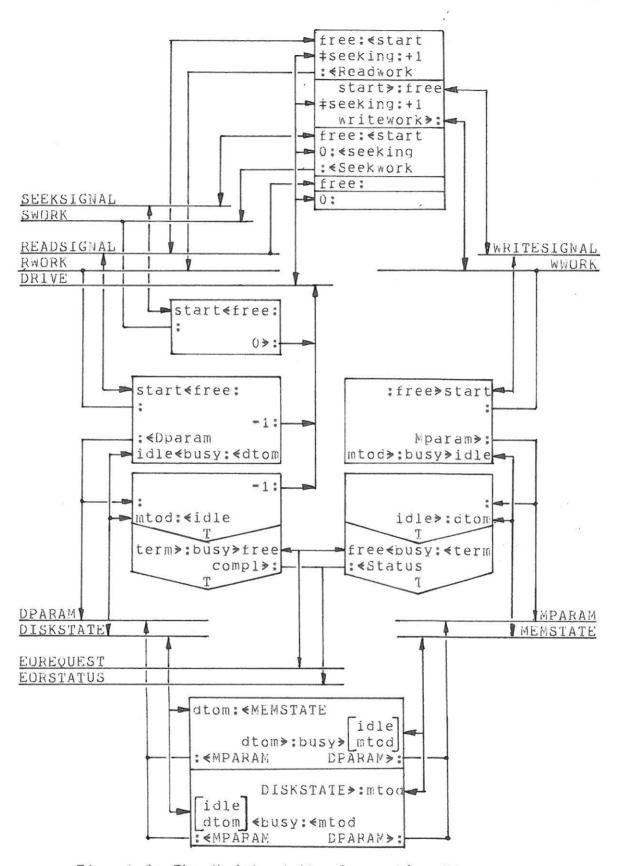

|            | 6.1  | The Channel Traffic Coordinator         | 75  |

|            | 6.2  | The Drive Arm-positioning Handler       | 82  |

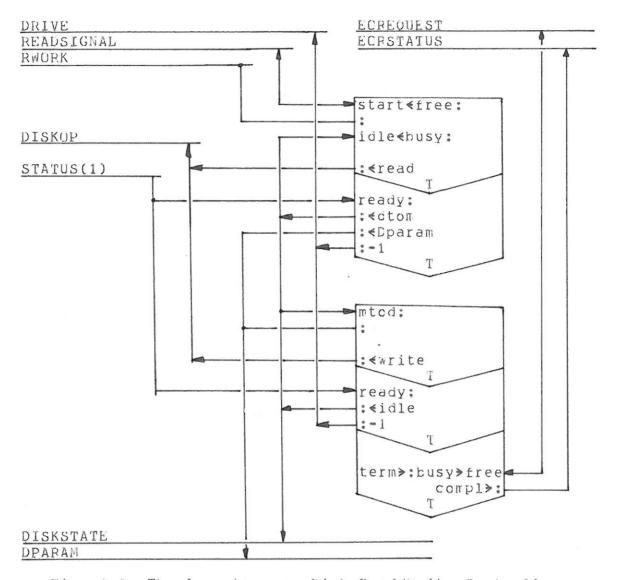

|            | 6.3  | The Disk Read/Write Controller          | 83  |

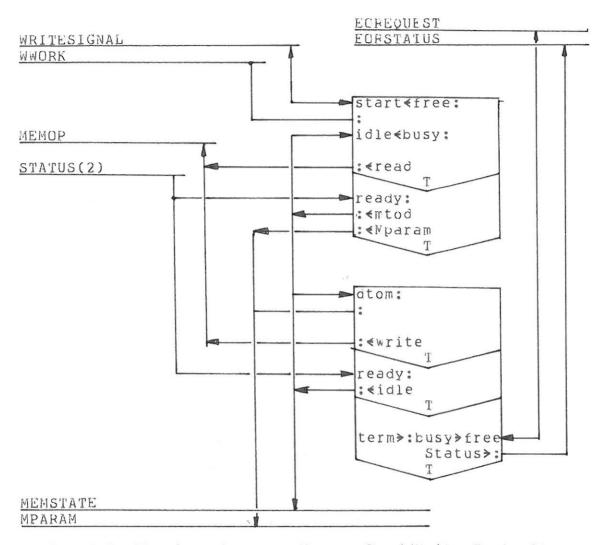

|            | 6.4  | The Memory Read/write Controller        | 86  |

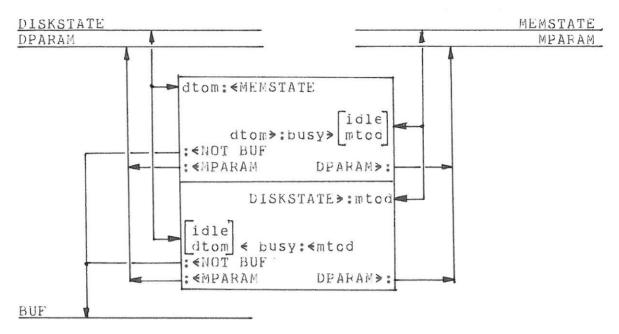

|            | 6.5  | The Channel Traffic Governor            | 87  |

|            | 6.6  | The Model of The Supporting Firmware    | 89  |

|            | 6.7  | Implementation in Firmware              | 92  |

| 7.         | Con  | clusion                                 | 97  |

|            | 7.1  | Future work                             | 98  |

| References |      | 101                                     |     |

| Glossary   |      |                                         | 103 |

| App        | endi | x A                                     |     |

| Appendix B |      |                                         |     |

## 1.INTRODUCTION

This dissertation presents a methodology for describing a complex system composed of processes with independent execution capabilities. The system to which the methodology is applied is a Disk Channel Processor for Aarhus University's experimental computer system, RIKKE/MATHILDA.

The present design is expected to be implemented in the future, and to be used as part of future research projects. It is impossible, indeed undesirable, at present to fix too strongly many implementation details which might have adverse effects upon future projects.

For example, a future project may be a design of a data base machine where the disk channel processor must know of data base details; or future research may consist of the measurement, evaluation and analysis of this disk channel processor, and of the optimisation of its performance, for example by moving certain services to hardware level or micro-processors.

In any case, there are elements of this design which will always be needed (e.g., the hardware double buffering device functions as the physical connection between disk drives and memory, or the coordination of read, write and seek), and others which may or may not be changed. The problem the author came up against while attempting to document the present design was how to present it with sufficient clarity so that the key concepts are specified with the greatest possible precision, while not overspecifying it in areas where technicalities would best be left to the actual implementors.

The solution chosen was to develop a System Modelling Language, and the Pictorial Representation. The former is used to describe important algorithmic components of the processor, the latter is used to describe how the various components interact with one another.

One of the first problems encountered when looking for a description tool was that by describing certain hardware-oriented pieces in terms of wiring diagrams, one practically excluded the possibility of implementing those pieces in microcode or software, because it was not clear whether the software structure presently in the author's mind would be recreatable in the future from such wiring diagrams. Similiarly, to use only a software notation would have made it unclear how to implement some parts in hardware.

Out of these considerations resulted the development of the Pictorial Representation, which lies somewhere on the borderline between wiring diagram and algorithm. Experience has shown it to be reasonably comprehensible to both programmer and hardware engineer, and experiments in translating it in either the hardware or the firm- software directions have until now proven to be relatively straightforward.

The description methodology that is being demonstrated makes use of the two notations, and has the effect that decisions concerning the implementation technology can be deferred without any essential loss of functional specificity.

## 1.1. Outline of Thesis.

Chapter 2 presents the language used for the description of various software, firmware and hardware mechanisms. The language - named the System Modelling Language - is a slightly extended version of the high level language BCPL ([6],[7]). Only three new concepts are added to the language definition; these provide facilities for the description of processes, mailboxes and indivisible operations.

The language is used for a detailed description of mechanisms in a system (mechanisms local to processes as well as mechanisms for process interaction). The Pictorial Representation, presented in chapter 3, is used to describe inter-process relations in a system consisting of several independent process components.

With regard to interactions among component processes the two description tools are compatible; a description in the Pictorial Representation can be mapped into a description of the same system in the System Modelling Language and the same description can be mapped back. This will be demonstrated through the example used to illustrate the properties and feasibility of the modelling tools. This example is a design for a Disk Channel Processor. The relevance of the Disk Channel Processor as an example is discussed in section 4.4.

Chapter 4 provides a introduction to the design of the Disk Channel Processor, which eventually will be a part of the Experimental Computer System (RIKKE/MATHILDA [2]) at the Computer Science Department of Aarhus University. The Disk Channel Processor is organised as a set of interacting processes each implementable in hardware, firmware or software.

The Disk Channel Processor design is divided into levels - Hardware, Firmware, Software.

The Hardware level - i.e. the part of the Disk Channel Processor to be implemented in hardware, is described in chapter 5, using the Pictorial Representation and the System Modelling language (the System Modelling Language algorithms are given in Appendix A).

Chapter 6 provides a description of the microcoded part of the Disk Channel Processor. Additionally, this chapter gives a detailed programming scheme for an implementation (the algorithms for this part of the Disk Processor are given in appendix B).

Chapter 7 presents some conclusions and proposes topics for further study.

#### 2. THE SYSTEM MODELLING LANGUAGE.

This paper uses BCPL ([6],[7]) algorithms for the description of various software, firmware and hardware functions. The System Modelling Language is an extented version of BCPL. The extensions make it possible to describe synchronisation mechanisms for independent processes. The language is used for descriptive purposes only, and the extensions were made informally. No claims are made concerning the formal properties of these additional constructs. BCPL is chosen as the foundation for the System Modelling Language for the following reasons:

- a) It is used as the system programming language for the experimental computer system at Aarhus University, with which the author is quite familiar.

- b) It provides a wide set of control constructs.

- c) It achieves simplicity and generality by providing a single data type - the word.

- d) The language does not employ facilities such as 'events','wait', 'cause' (B6700 algol [8]) or 'on condition' (PL/1). Thus defining such facilities within the present text, presents no risk of confusion.

- e) It has been used for description purposes in [9] and [12].

The extensions to the definition of BCPL, necessary to describe interprocess communication, are very limited. For description of static properties of a system consisting of independent, interacting processes, the declarations process and mailbox are introduced to describe processes and shared variables, respectively. For description of interprocess communication an indivisibility concept is introduced.

The three extensions, which are described in the following, are based on ideas in [9] and [12].

# 2.1. The Process Declaration.

The description in the System Modelling Language of the non-sequential properties in a system which consists of independent or concurrent activities, is provided through the process declaration.

A process declaration binds a name to an algorithm. The algorithm is a BCPL command ([7]).

Within P it is possible to reference the static, manifest and mailbox variable declared in the block where the declaration of P itself appears. (the mailbox declaration is described in the following section).

An independent process is by nature not a callable routine or function, i.e. it is not sequentially related to any statements in other algorithms. Mentioning the name of a process in other algorithms is therefore meaningless.

## 2.2. The Mailbox Declaration.

In order that two processes be capable of interacting, at least one shared memory component must exist and be accessible from both processes.

A named memory component which participates in the execution of more than one independent process, is called a mailhox .

In the system Modelling Language a mailbox is declared in a declaration list preceding the declaration of those processes which access the mailbox (2.1.).

It is obvious that the processes which share a mailbox must perform their operations upon the mailbox according to some prearranged conventions.

These (the conventions) are only described in the algorithms for the set of processes 'knowing' (through declaration) the mailbox and using it.

The minimum requirement for such conventions is, that simultaneous attempts to either read the value from, or write a value into a mailbox will cause the actual accesses to take place sequentially, one after another. All read- or write operations upon mailboxes are defined to satisfy this property ([9]).

Mailboxes are normally implemented as memory locations or communication wires used in process communication, or as state variables for the control of sharable resources.

# 2.3. Indivisibility.

Communication or sharing arrangements are set up either for a single named mailbox or for a set of logically connected mailboxes. For example signal, control information and data normaly go together when used in inter-process communication.

The description of the agreements according to which the processes in a computer system communicate, is independent of the implementation level (hardware, microprogram, software). Two emulated activities could share a memory location, or a hardware function could share a button on a printer device with the operator.

In order to describe these agreements the indivisibility concept is introduced.

A description of an operation or a set of operations either is enclosed within indivisibility brackets ('<<' , '>>'), or is not.

Execution of operations within indivisibility brackets, behaves as if it is instantaneous, or uninterruptable.

For a single processor system the use of indivisibility brackets reflects the 'mode' of execution, which may be interruptable or uninterruptable. In such a system the bracketing can be implemented by using interrupt-disable and

interrupt-enable functions.

## Example 1:

The following piece of code illustrates the behaviour of a 'wait' function using a mailbox EV as an 'event' variable.

```

until valof

{w

<< if EV = nothappened resultis false

EV := nothappened >>

resultis true

}w loop

//continuation here means that event EV happened.

```

The value of the 'valof block' (an expression) is determined by executing the 'block' until a resultis command is executed, which causes the execution of the block to cease. The value of the expression is the value of the expression part of the resultis command. In the exemplified case, one of the resultis commands branches from an instruction enclosed within indivisibility brackets to an instruction not enclosed in indivisibility brackets.

A translation of this program into RIKKE 'machine-code' (hand compiled and optimized), illustrates the use of interrupt disable and interrupt enable instructions as a possible practical implementation of indivisibility. It is still assumed to be a single processor system.

The 'machine-code' program is given in the following:

```

//t1 names an instruction not enclosed

t1: INTON

//in indivisibility brackets; therefore

//interruptability is restored.

INTOFF

//interrupt disable

LM EV

//load mailbox EV onto stack

//top of stack gets true if EV=nothap

EO nothap

//else false

JUMPt t1

//if top of stack is true, control is

//transferred to t1.

//load the constant 'nothap'

LN nothap

SM EV

//store top of stack in EV

INTON

//restore interruptabilitity

```

# Example 2:

With the System Modelling Language any complex communication can be described.

Let CON, LINE1, LINE2 be mailboxes.

Consider a conditional wait function, where a process P either waits for 'LINE1=free' or 'LINE2=free' depending on the contents of CON, whose value is changable, independently of P's execution, by another process. In other words P will wait for one of the conditions 'CON=read /\ LINE1=free' and 'CON=write /\ LINE2=free' to be satisfied. P is designed to act on which ever of the two compound conditions happens first.

Con is a local variable, which is used to remember the state of  $\ensuremath{\text{CON}}$  .

In the System Modelling Language the description would be:

```

mailbox { CON; LINE1; LINE2 }

manifest { free=1; read=1; write=2; busy=3 }

process P is

let Con = 0

until valof

{cond

<<switchon CON into

case read: if LINE1=free do

{ Con := read

CON := busy

resultis true }

endcase

case write: if LINE2=free do

{ Con := write

CON := busy

resultis true }

endcase

}>>

resultis false

}cond loop

```

# 3. THE PICTORIAL REPRESENTATION.

During the design of a system constructed from a set of independent cooperating processes it is convenient to have a pictorial tool with which these component processes and their interactions can be described.

The pictorial representation serves as a model of the system; each element of the real system which controls synchronization, sharing etc., has a pictorial counterpart in the model. If such a representation is to be of use in modelling or analyzing systems, it should be as simple as possible: it should represent only those components and connections which are essential to the understanding of the system. It should be complete. And, importantly, the notation must not add complexity or confusion to the system that is modelled.

# 3.1. The Properties of The Representation.

The pictorial representation should have the following properties:

3.1.1 Local mechanics should be left out.

Local variables - variables that are referenced only by a single process - do not influence the interaction between the processes, and have no effect upon the internal behaviour of any process other than the one to which they belong. Such variables, and all local mechanics related to them, should be eliminated from a description which only pictures inter-process relations.

3.1.2 All relevant mechanics should be described.

In a description of large, complex systems it is often tempting to simplify the description by eliminating some of the components or combining groups of components into single components in the

diagram. Some components are so integral to the whole systems behaviour that they cannot be removed from the description, as too many assumptions would have to be made about the abstracted pieces if the description were still to reflect the system's true behaviour. Such components have to remain in the description.

3.1.3 Independent groups of components should be isolated.

It is often impossible to model even a small system so compactly that the model clearly illustrates the total control-flow. A pictorial representation tends to grow in size. If a part of the system (e.g. a set of processes) is influenced by, or influences the remainder of the system according to simple communication arrangements, that part of the system can be isolated and temporarily removed, without elimination of relevant information. For example, in the case where a set of processes acts as a single subroutine or function, and only references resources shared with other processes during initialization and termination this technique is advantageous.

3.1.4 Strongly dependent components should be combined.

To further minimize the pictorial schema, a group of components in which the interaction between the components follows well-defined and comprehensible rules should be represented by a single construct, which contains the same information as the original separate components.

3.1.5 No redundancy should be introduced.

Single components in the real system should be represented by single components in the model. If this requirement is not met ( for example, single real components are represented by a number of model components, each of which having no obvious counterpart in reality) the model will contain unnecessary information, and may become functionally misleading.

# 3.1.6 The Representation should be balanced.

To give a true overview of the real system, the relative complexity (or importance) of a component should be reflected by its pictorial representation. For example, if a very simple part misleadingly dominates the schema, then the representation is unbalanced.

## 3.2 The Elements of the Representation.

The schematic representation is a <u>network</u> describing <u>processes</u>, shared <u>variables</u> and the <u>connections</u> between the processes and the shared variables.

In a real system a shared variable can be a memory location, a communication wire, or any resource which can be accessed by more than one process. A process is an activity which may be realized by functions implemented in hardware, microprogram, software, or by direct operator action.

In the model neither the shared variables por the processes.

In the model neither the shared variables nor the processes are bound to a specific realization ( i.e memory or processor ).

## 3.2.1 Shared Variables.

A shared variable is represented by a line or a set of connected lines. As a memory location can have a specific content, a line or a set of lines can have a single value. The value of a line is determined by the processes which reference the shared variable which the line represents.

## 3.2.2 Processes and Connections.

A box represents a process. The process references shared variables only during activation and termination. Such processes are referred to as component processes or just as processes.

A component process - which reads a value from, or writes a value into a shared variable - is represented by a box connected to a line, which represents the shared variable.

# Example:

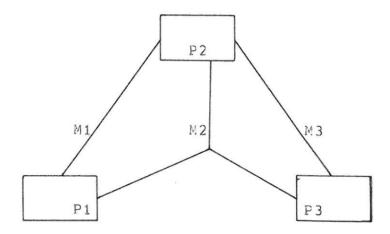

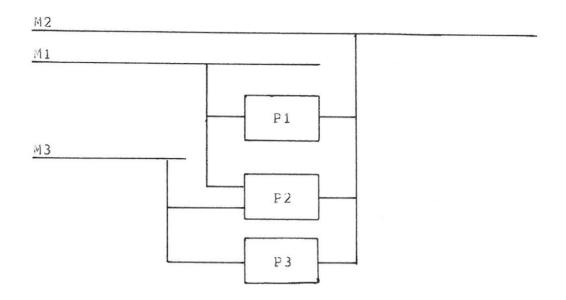

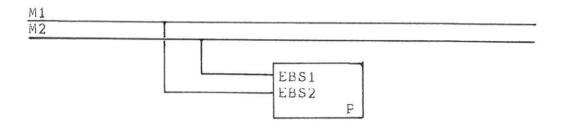

let P1, P2, P3 be 3 independent processes; and let M1, M2, M3 be 3 shared variables.

M1 is a shared component for P1 and P2.

M2 is shared by all processes.

M3 is shared by processes P2 and P3.

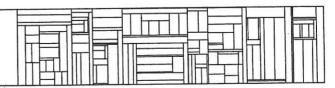

Schematic representations for this system are given in Fig. 3.1 and 3.2. The way of arranging lines and boxes, which is illustrated in Fig. 3.2 is to be preferred in more complex situations; it is used in all subsequent chapters.

Fig. 3.1: A Schematic Representation.

Fig. 3.2: An improved Representation.

So far the pictorial representation only contains a limited amount of information about the behaviour of the real system.

Essential properties, such as how sharing is controlled, how protection is guaranteed, and how communication protocols are arranged, have yet to be added to the description.

# 3.3 Elementary Behaviour Statements.

An important aspect of the behaviour of a system is how and when a process will inspect or influence other processes. A process inspects another process by reading the value of a variable shared by the two processes.

A process influences another process by assigning a value to a variable shared by the two processes ([9]).

A connection point between a line and a process represents a potential for an inspection or an influence. The exact ef-

fect of such an inspection or influence is described by an Elementary Behaviour Statement (EBS). an EBS is an expression adjacent to the point where the line is connected to the box, specifying the action undertaken by the module (box), based on the value of the variable (line).

## Example:

let M1 and M2 be shared variables and P be a process.

The statements (EBS1 and EBS2) specify upon which conditions process P will be enabled to execute and what changes it will make to the values of the shared variables during execution.

## 3.3.1 The Syntax of an EBS.

<arop> ::= + | -

<unop> ::= NOT | -

Alternative representations of the operators may be used.

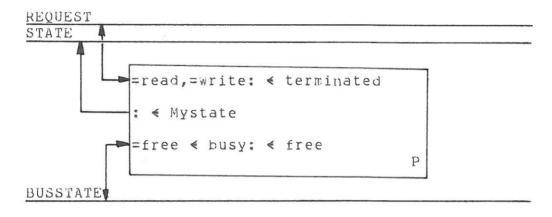

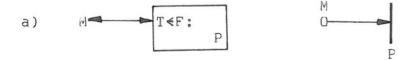

An example of the syntax of EBS's is given in Fig. 3.3.

Fig 3.3: Elementary Behaviour Statements.

The following spelling conventions for names are used:

Names of shared variables are in upper case.

Names of constants are in lower case, and

names of local variables have an initial upper case

letter, followed by lower case letters.

To further add information to the model the lines representing shared variables have been equipped with arrows to indicate where the contents of the shared variables may be changed.

# 3.3.2 The Semantics of an EBS.

Consider the following example of an EBS:

relop1 E1, relop2 E2 :

€ E3

which is associated with a connection point between a process P and a shared variable M. It is assumed

that it is process P's only connection point.

If the condition

(M relop1 E1) ∨ (M relop2 E2)

is satisfied then process P is enabled, and P will 'execute'.

(If several EBS's are associated with a process, the process will be enabled only if the conditions described within all of these EBS's are satisfied, simultaneously.)

At the point in time when a process is activated, local copies are taken of shared variables accessed by the process.

The evaluation of all logical expressions appearing in a single box, and copying of shared variables into local copies is a single indivisible operation.

The ':' represents the execution of P's local statements, using its local variables and local copies of the shared variables (see 3.1.1).

At the termination of P the assignment

M := E3

will take place.

All assignments appearing after a ":" inside a box are assumed to take place as a single indivisible operation.

If expression E3 contains the name of a shared variable, then the value of the shared variable is the value of a copy taken when the process was initiated.

If an EBS has the format,

<C-list>

∢ E:

the entire part to the left of the colon, is executed

as an indivisible operation (test-and-modify-if-true).

If the condition is satisfied the process will execute. The value of the local copy of the associated shared variable is the (only extant) value of the shared variable before modification.

If the condition list is empty the condition is always satisfied.

If no assignment is present in an EBS no change of the snared variable will take place. But a local copy will still be taken when the process is activated.

An EBS does not specify how a process may use the value of a shared variable once execution has begun.

## 3.3.3 Notation rules for EBS's.

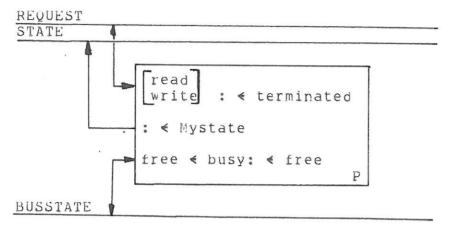

Elementary Behaviour Statements are usualy very simple expressions. Some notation conventions can be used to further simplify them.

- a) If the relational operator in the condition list (C-list) is omitted the equality operator will be assumed.

- b) In the schematic representation a condition list may be pictured as a column rather than a list.

These notation rules for condition lists are shown in Fig. 3.4, which illustrates a system which is seman-

tically equivalent to that shown in Fig. 3.3.

Fig 3.4: Notation Rules.

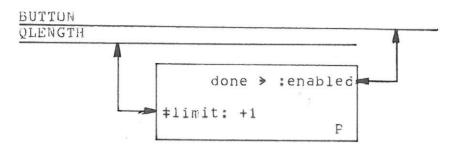

c) If the assignment part of an EBS, associated with line M, has the form,

< M binop E

binop E.

may be used.

d) A connection point between a box and a line may, for pictorial reasons, be on the right hand side of the box. A mirror notation

E1 > : E2 > C

for the associated EBS is more informative, and may be used. The interpretation of a mirrored EBS is obvious.

The notation rules for the assignment part of an EBS, and an example of a mirrored EBS, are illustrated in

Fig. 3.5 .

Fig 3.5: Notation Pules (continued).

3.3.4 Comparison of The Schematic Representation and the System Modelling Language.

The pictorial description of a process or a system can be directly mapped into the System Modelling Language of chapter 2.

Consider the example given in Fig. 3.4.

```

The Symbolic equivalent would be

mailbox { REQUEST ; STATE ; BUSSTATE }

manifest { read=1 ; write=2 ; terminated=3

free=0; busy=1 }

process P is

let Request = 0

and Busstate = 0

until valof

{Pcond

<< if ( REQUEST=read \/ REQUEST=write ) /\

BUSSTATE=free ) do

{ Busstate := BUSSTATE

Request := REQUEST

BUSSTATE := busy

resultis true } >>

or resultis false

}Pcond loop

{Paction

let Mystate = 0

S1

if Request=read do . . // statements only

// involving local

switchon Busstate into // control flow

Sn

<< STATE := Mystate

REQUEST := terminated

BUSSTATE := free >>

}Paction

} repeat

```

# 3.4 Sharing and Communication

In the previous section the emphasis was placed on the description of system behaviour seen from the point of view of a single independent process.

The set of EBS's inside a single box specifies how a process influences and inspects its environment.

The set of EBS's attached to a single line specifies the interaction between processes, sharing the line. These EBS's illustrate how independent processes influence each other, how sharing is controlled, how communication protocols are arranged and how the protection in a system is maintained.

Six kinds of basic interactions can be described by means of an Elementary Behaviour Statement:

1) Conditional Influence (EBS  $\equiv \langle C-list \rangle : \langle \langle E \rangle$ )

2) Influence (EBS ≡ :<<E>)

3) Inspection (EBS ≡ :)

4) Conditional Inspection (EBS = <C-list>:)

5) Singular Conditional Inspection (EBS = <C-list> €<E>:)

6) Singular Conditional Influence (EBS = <C-list> €<E>: €<E>)

These are described in the following.

# 3.4.1 Conditional Influence.

If the EBS has the form,

C1 : < C2

and the relation between a process P and a shared variable M is expressed by this EBS, then, if the condition M=C1 is satisfied P is capable of assigning a value to M. All other processes which share M with P may be influenced. As the influence is con-

ditional, communication protocols may be arranged.

# Example:

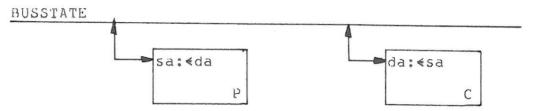

The following is assumed:

a producer process P,

a comsumer process C, and

a control-line BUSSTATE, shared by P and C.

BUSSTATE is a state variable for a bus along which

data transfer can proceed.

BUSSTATE has the values:

da = data available on the bus.

sa = space available on the bus - i.e previous data

comsumed.

A model for this system is given in Fig. 3.6.

Fig. 3.6: A Producer-Consumer Model.

## 3.4.2 Influence.

If the connection between process P and variable M is defined by an EBS of the form,

# : < C

then all processes, which are capable of reading M, are potential objects of process P's interference. As the influence is unconditional the sharing of M has to be controlled using other variables shared by the set of processes.

# 3.4.3 Inspection.

If an EBS (for a connection point between P and M) has the form,

then P is free to inspect all processes connected to M, unhindered. In addition the inspection is untraceable.

## Example: (continued)

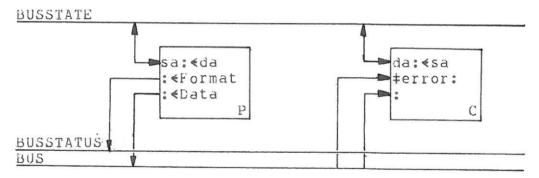

Consider the system illustrated in Fig. 3.7. Let BUSSTATUS, BUSSTATE and BUS be lines shared by P and C.

BUSSTATE is the same as in Fig 3.6.

BUSSTATUS values:

byte = data available or

byte = data available on the bus has format byte.

word = data available on the bus has format word.

error = hard-error occurred, which forces the system

to a halt.

The model of this system - given in Fig.3.7 illustrates influence and inspection.

Fig. 3.7: A Producer-Consumer Model (continued).

# 3.4.4 Conditional Inspection.

Consider the consumer process in the previous example. The EBS '\( \pm \) error' indicates that process C is able to execute only if BUS contains valid information - i.e C is able to inspect P only if the condition BUSSTATUS\( \pm \) error holds - conditional inspection.

# 3.4.5 Singular Conditional Inspection.

If the same condition-list appears in more than one EBS associated with a single shared variable, then several processes are potentially able to execute upon the same single event.

If the event is the release of a rescurce shared by the processes, then the activation of a single process should prevent the remaining processes from executing. In the pictorial model this is described by means of an EBS (inside all processes) of the form,

#### C1 € C2 :

which indicates that the value of the associated variable is destroyed upon activation of the process.

This form provides an arbitration function to exclude all but one of a set of potentially mutually conflicting processes.

# 3.4.6 Singular Conditional Influence.

If the EBS has the format,

## C1 < C2 : < C3

then the process can assign a value to  $\mbox{M}$  under condition of mutual exclution.

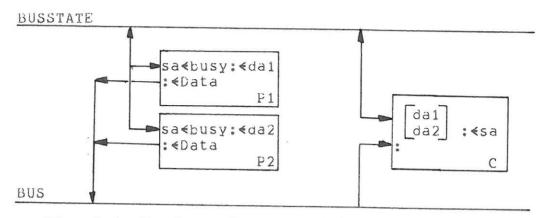

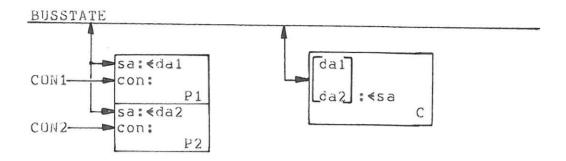

## Example:

Consider a system with two producer processes P1 and P2,

a comsumer process C, and

a control line BUSSTATE, which may have the values:

sa = space available on the bus.

da1 = data produced by P1 available on the bus.

da2 = data produced by P2 available on the bus.

busy = the bus is temporarly unavailable.

The model for the system is given in Fig. 3.8.

Fig. 3.8: Producer-Consumer Model (continued).

The previous examples have illustrated how special arrangements a set of EBS's associated with a single line guarantee proper sharing of resources (bussystems, communication wires, sharable memory, buffers etc.).

A more complex example is as follows.

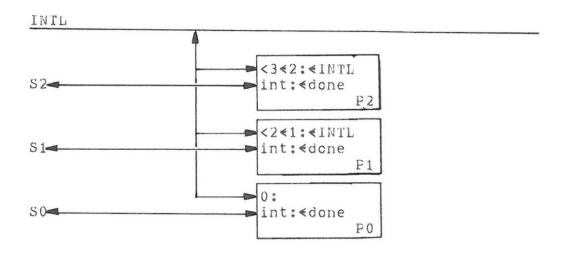

Consider an interrupt mechanism for a single processor system.

An interrupt, together with the interrupt handling routine, can be regarded as a process 'stealing' a resource - the processor - from a running program. The independent interrupt-system should support interrupt inhibition, according to a priority scheme.

For this the following is assumed:

INTL is a shared variable, which contains the value of the current interrupt level.

P < n > is a process which takes care of interrupts on level < n >.

P<n> monitors the signal line S<n>, which has the values:

int = interrupt.

done = previous interrupt handled.

Fig. 3.9 gives a model of such a system (three interrupt levels).

The inhibition of interrupts according to the priority rules is guaranteed by setting and restoring

the interrupt level, on process activation and process termination, respectively. The ':' represents the utilization of the processor, which executes the interrupt handler routine.

How the processor stores and restores the state of interrupted programs is not specified.

Fig. 3.9: Interrupt Mechanisme.

## 3.5. Parallelism and Concurency.

A potential for parallelism in a system exists if the model contains:

- 1) boxes which are not connected at all, or

- 2) boxes, one or more of which are related by means of influence or inspection only, or

- 3) connected boxes, where the EBS's associated with a single common line have the same condition list, or

- 4) two connected boxes, where the activation conditions for a process, represented by one of the boxes, will be satisfied upon activation of the process, represented by the other box.

- 1) and 4) will be illustrated in the following example:

Assume the following:

a) A Serial to Parallel Conversion Unit (StoP) which

receives serial formatted data, converts the data into its parallel equivalent and gates the converted data along a bus. Such a process may be time-critical, when it receives information from a synchronous device.

- b) A transmitter process, which receives input from StoP and gates data along a bus to,

- c) A comsumer process C.

- d) Two state variables (STATE1, STATE2), one describing the state of the bus between StoP and T, the other the bus between T and C.

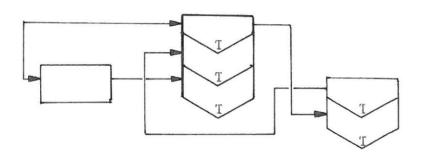

Fig. 3.10 gives a model of such a system. The communication arrangements illustrated in the model enable StoP to execute in parallel with C according to 1), and in parallel with T according to 4).

Fig. 3.10: Concurrent Processes.

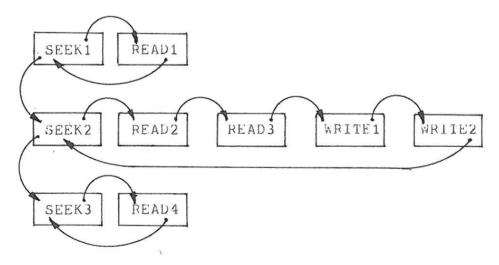

## 3.6 Combined Constructs.

As mentioned in 3.1.4, strongly dependent components in a model should be combined into a single construct. In a system, an example of a set of strongly dependent components is a set of interacting processes which are unable to execute in parallel, and where the mechanism which administers the flow of control between these processes is self-contained and provides a predictable flow of control (i.e. the set of processes may be influenced by its environment, but this does not disturb the logic of the internal control mechanism).

It is obvious that a single component may participate in several independent sequences of program execution (system behaviour). It is the responsibility of the designer to select the component processes to be mapped into a single construct in such a way that the model is aesthetically pleasing and comprehensible.

Unce it is decided which components should be combined, the construct can be regarded as, and referred to as a single process.

The four combined constructs described in the following, form a sufficient set to describe the interaction between strongly dependent processes.

# 3.6.1. Sequence.

If the statements of a set of processes execute as a sequential program the combined construct (SEQ) will be used to describe the interaction between the processes.

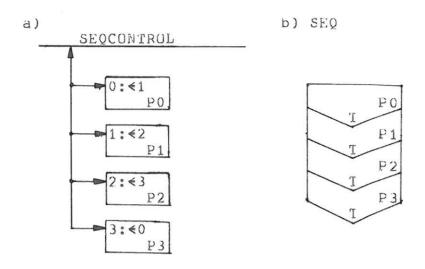

Fig. 3.11. illustrates,

- a) An example of a sequential control mechanism for 4 processes, PO,P1,P2 and P3.

- b) The combined construct.

The construct clarifies the behavior of the system. The notation 'T' indicates that the enabling condition for the process to which 'T' is associated (in-the-same-box) has to be satisfied and the process terminated, before control is transfered to the subsequent process. 'Control' flows top to bottom.

The component processes cannot be combined into a single box, as each process still is an independent component (see Fig. 3.12).

Fig 3.11: Sequence Control.

Fig. 3.12: Model utilising SEQ-constructs.

# 3.6.2 Priority.

Consider the system consisting of 2 producer processes (P1,P2), and 1 consumer process (C) illustrated in Fig. 3.8.

Both of the producer processes use the same resource during execution. The control mechanism described (i.e. exclusion) for interaction between the 2 producers does not provide a deterministic description of the behaviour of the system. From a given state of the system (e.g. BUSSTATE=iole) it is unpredictable which process (P1 or P2) may be activated next.

In a realization of such a system, a control mechanism which provide determinism may be used. In other words a control mechanism can be added to the producer-consumer system such that if both P1 and P2 have decided to execute and BUSSTATE=idle, then P1 will start; if P1 is not ready to excute and BUSSTATE=idle then P2 will execute (P1 has priority). If a set of strongly dependent processes are controlled by a priority mechanism the combined construct (PRI) will be used to describe the interaction between the processes.

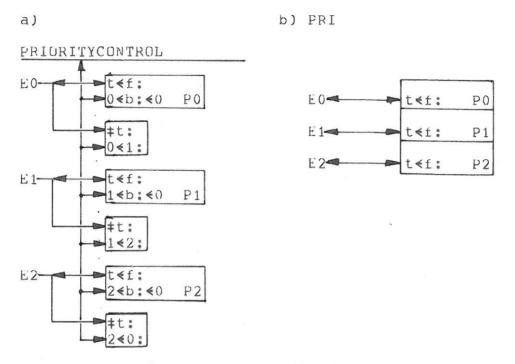

Fig. 3.13 illustrates,

a) model of a priority control mechanism for 3 processes: P0,P1 and P2. E < n > (n=0,1,2) is an enable inlet - for P < n > - with the values:

$t \equiv P < n > enabled;$

f = P<n> terminated.

The priority mechanisms are controlled through the use of the line PRICRITYCONTROL, which can have the values:

<n>  $\equiv$  P<n> is allowed to start executing; b  $\equiv$  no processes are allowed to start executing.

In this and the following examples P<n> is assumed to make its activation known to its environment using an EBS of the format 't<f:'. P<n> could also be totally controlled by other processes (using 't:') or could make its termination known by means of an EBS in the format 't:<f'.

In general the enabling condition for P<n> (i.e. the 't') could be a combination of conditions associated with several inlets.

To model such systems does not involve mechanisms of types other than those explained here.

b) The combined construct (PRI) is used to illustrate the priority-control mechanism. Component processes PO, P1 and P2 are illustrated separated by horizontal lines. Processes are ordered top to bottom with decreasing priority. At any time only one process can be active. If there is conflict between two or more processes concurrently able to activate, the higest priority

process is chosen.

Fig. 3.13: Priority Control.

If a priority control mechanism is used in a two-producer, one-consumer system (analogous to the one illustrated in Fig. 3.8) then the model can utilize a combined construct. (see Fig. 3.14).

Note, in comparing Fig 3.8 and Fig. 3.14 that the same interference problem was solved, in the former through a Singular Conditional Influence, and in the latter by use of priority.

Fig. 3.14: Producer-Consumer Model.

Both processes make its termination known to process C.

Variables CON1 and CON2 have been added, in order to give the system a meaningful behaviour. Only in the case where the values of both CON1 and CON2 are simultaneously equal to "con" will the priority scheme be used.

An example of a PRI construct described in terms of the system modelling language is given in Appendix A.1.

#### 3.6.3 Rotation.

Due to properties of processes it may not be appropriate to use a priority scheduling mechanism, where a process may suppress the execution of other processes with lower priorities.

A control mechanism called Rotation Control may to be a better alternative for the control of a specific system. (i.e. round robin mechanism).

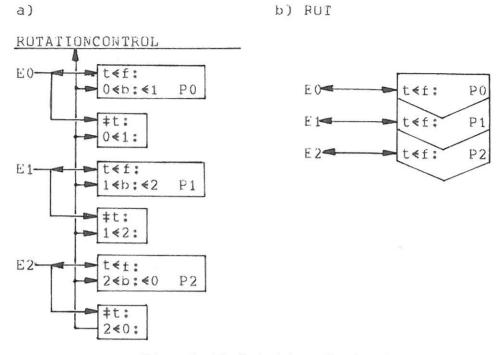

Fig. 3.15 illustrates,

- a) A model of a system consisting of 3 processes, where none of the processes are capable of suppressing other processes.

- b) The combined construct (FOT), used to describe such a behaviour.

Fig. 3.15 Rotation Control.

The rotation control mechanism contains a priority scheme - the involved processes take turn in having priority. Futhermore it contains a rotation scheme.

# 3.6.4 Suppression.

If any process in a system consisting of a set of strongly dependent processes is capable of suppressing all other processes, the control mechanism is named suppression (SUP).

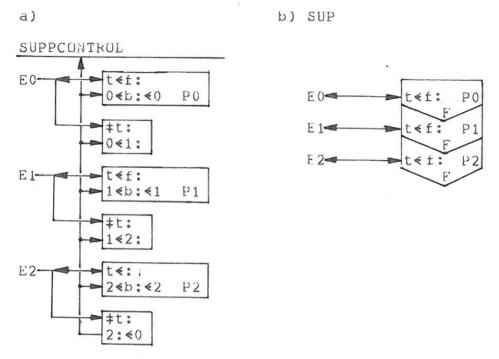

Fig 3.16 illustrates.

- a) a model of a system of 3 proceses, where any process P<n> suppresses other processes, as long its enabling condition 'E<n>=t' remains satisfied.

- b) the combined construct for a suppression control mechanism. The 'F' inside a box - which represents P<n> - indicates that transfer of control to P<n+1> is delayed as long as the enabling condition for P<n> remains satisfied.

Fig. 3.16: Suppression Control.

The suppression control contains a priority scheme - any executing process will upon termination still have priority.

An example of a SUP construct described in terms of the system modelling language is given in Appendix A.2.

# Example:

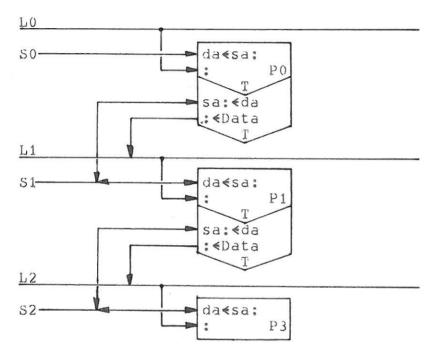

To illustrate the use of combined constructs in a concurent system consider an asynchronous pipeline process.

Such a process can be regarded as a set of minor processes, each performing the operations required on a specific stage on the pipeline.

All these processes should be able to proceed indepently and should only require access to sharable resources upon activation and termination. Upon activation, a process performing operations on stage n gets input from a line whose value is produced by the process performing operations on stage n=1.

Assume that the pipeline consists of,

- a) 3 independent processes: PO,P1 and P2.

- b) 3 lines: L0,L1 and L2 (these may be registers, memory locations or communication wires), where L<n> contains output produced by P<n-1>. P<n> takes input from L<n>.

- c) 3 state variables: S0,S1 and S2, where S<n> specifies the current state of line L<n>, being

da ≡ data available.

sa = space available.

Fig. 3.17 gives a model for such a system.

Fig. 3.17: A Pipeline System.

Each process in the pipeline consists of two component processes, organized in a SEQ construct. The first component starts processing data as soon as input is available. The second component process gates the result to a communication line as soon as the line is free.

According to the rules mentioned in section 3.5 all processes represented in this model by single constructs, are able to execute in parallel.

# 3.7 Remarks on Description Tools.

Other pictorial tools for describing and analysing system behaviour, such as flowcharts or Petri Nets [10], are available. Therefore the question could be raised why it should be necessary to develop yet another representation. The justification is that flowcharts are not adequate for modelling non sequential systems, and that Petri Nets are syntactically unacceptable in that they violate the requirements described in section 3.1. Given that Petri Nets have been used for modelling of systems, the following remarks may be of interest:

1) In terms of the semantics defined in this chapter, the only primitive operation allowed by Petri Nets is of The Singular Conditional Inspection EBS form.

The examples in this chapter have justified the existence of other EBS forms. Their lack in Petri Nets forces a deformation of the description: the designer is forced to add components to his model which have no counterpart in the system being modelled.

#### Example:

#### Assume

- a) a shared variable M, which is represented by a 'place' in a Petri Net, and by a line in the Pictorial Representation,

- b) a process P, which is represented by a 'bar' in Petri Nets, and by a box in the Pictorial Representation. M has the values:

```

T = true (in Petri Nets M is 'marked')

F = false (in Petri Nets M is 'unmarked')

```

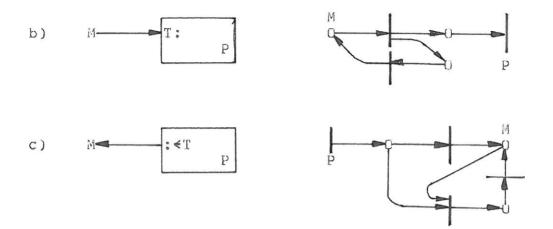

The following examples give 3 simple constructs, modelled using both the Pictorial Representation and Petri Nets.

The examples illustrate how additional components (places,bars) have to be invented for the Petri Net model, leading to unnecessary syntactic 'noise'. In other words Petri Net models violate 3.1.5. It is interesting to notice that the simplest EBS form is mapped into the most complex Petri Net construct, and vice versa.

2) The need for additional 'primitive components' is more than just for reasons of eliminating syntactic 'noise'.

Consider a process which resets the state of a subsystem. In the Pictorial Representation this can be expressed as a pure influence. In Petri Nets it is certainly unclear how such a concept can be modelled, as a knowledge of the state of the subsystem has to be built into the model.

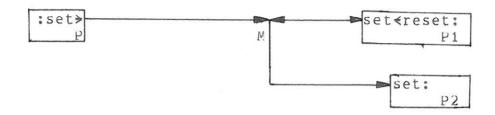

A simple example: Consider a process P, which upon a certain event (e.g. a clock) arbitrarily attemps to influence (EBS = ' $\leq$  set') two other processes P1 and P2 by writing to a line M. The influenced processes independently decide whether or not to actually accept the signal and act on it.

The model in The Pictorial Representation might look like:

and the model in Petri Net might be

which certainly is unclear. The concatenation of two simple and well defined subsystems, forces the designer to invent a complex 'interface', just to describe a clean communication.

As a consequence of this, Petri Net modelling does not always to comply with 3.1.3: it is not possible to isolate and temporarily remove components from the model.

3) The Petri Nets model does not provide any meaningful combined constructs such as those described in section 3.6. This forces Petri Nets Models for all but the most trivial systems to become of unmanageable size and utterly confusing.

# 4. AN ANALYSIS OF A DISK-CONTROLLER.

The usefulness of the new Pictorial Representation, presented in the previous chapter, is justified on the one hand by the inadequacy of existing tools for modelling concurrent systems and on the other by its demonstrated application to the description of a particular system. This system (chapter 4.-5.) is rather extensive consisting of many interconnected independent processes. Obviously other systems have to be considered - and presumably further development of the Pictorial Representation is necessary. This is discussed in chapter 7.

The reason for developing the new pictorial representation for concurrent systems, was the need for a modelling tool, which could be used to describe, analyse and design a Disk Channel Processor for the Experimental Computer System ([2]) at Aarhus University.

#### 4.1. The Configuration.

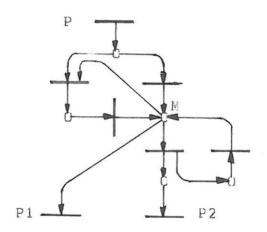

The Disk Channel Processor (referred to as the Disk-Controller) is realized as a set of interacting processes, each implemented by functions in hardware, microprogram or software.

To fully understand the analysis and the design of the disk controller a short introduction to the Experimental Computer System (RIKKE/MATHILDA) may be necessary.

The relevant system components are presented in the following sections.

# 4.1.1. The Physical Processor.

RIKKE - is a microprogrammable processor, with 4K of (64 bit) Control store.

The bus width is 16 bits.

The main data path architecture is a 16 bit 'version'

of that of the MATHILDA processor ([1],[2]). Instruction sequencing and control facilities for microprograms are equivalent to those of MATHILDA. RIKKE is equipped with an internal I/O Data Bus, by means of which devices can be multiplexed under micoprogram control.

The microcoded part of the Computer System is referred to as the firmware level. The part of the Disk Controller, implemented on firmware level, is referred to as The Supporting Eirmware, and is discussed in detail in chapter 6.

# 4.1.2. The Memory.

WIDESTORE - is a sharable memory, which can be accessed either as a 32K 64 bit wide memory, or as a 128K 16 bit wide memory.

WIDESTORE is equipped with a memory address- and data port multiplexer allowing for up to four physical processors to access the memory independently. In addition, WIDESTORE provides Automatic Address In-

crementing, which makes it possible for unintelligent devices to utilize direct memory access ([11],[13]). WIDESTURE is considered to be the Main Memory of the Computer System ([5]), and will be referred to as such.

#### 4.1.3. Virtual Processors.

The OCODE stack-machine (described in [3]) and, The I/O Nucleus ([4]) are virtual processors realized by means of microcoded functions (i.e. firmware level).

The set of operations in the Computer System, which is executed by means of interpretation performed by virtual processors is referred to as The Software Level.

At the software level, lives the operating system.

# 4.1.4. The Operating System.

The RIKKE BCPL System ([5]) is an interactive single-user operating system, which runs on the OCODE

machine and uses the I/O-Nucleus to perform I/O.

The comminucation between the software level and the firmware level is administered by a microcoded Communication Module, which:

- monitors a software level register, which contains eventual calls for firmware level functions;

- 2) transfers control to firmware level;

- 3) forwards results and completion status of firmware level functions to the calling software level routine, using micro-coded interrupt facilities.

# 4.1.5. The Supporting Hardware.

A hardwired logical unit (in the following referred to as The Supporting Hardware), the automatic address incrementing facilities of WIDESTORE and the disk-hardware, together form an unintelligent data channel between disk system and WIDESTORE.

The functions implemented in hardware will in the following be referred to as The Hardware Level. The communication between the firmware level and the Supporting Hardware is established by means of 2 output data bus ports (32 bit), used by micro-coded functions for controlling the Supporting Hardware logic, and 1 input data bus port (16 bit) for status feed-back.

The Supporting Hardware is discussed in detail in chapter 5.

# 4.1.6. The Disk Hardware.

The disk system consist of 2 movable head disk units, which are made up of 2 recording disks each ([14]). Each disk has two surfaces divided into twelve sectors.

Each surface has 407 tracks (of which 400 are used). Each track-sector contains one single recording block.

The Disk Hardware signals the supporting hardware when a sector mark or index mark is encountered. The Disk Hardware acts on signals sent from The Supporting Hardware to,

1) record serially formatted data, sent from the sup-

porting hardware, on a specific disk-surface;

- 2) transmit serially formatted data, or

- 3) move the access arms to a specific cylinder.

In the model of the disk controller presented in this paper (Chapter 5. and 6.) it is assumed that only 1 disk unit is connected to the system.

The configuration of the Computer System is illustrated in Fig. 4:1..

Fig. 4.1: The Computer System.

The components TTY,PTR,PTP,LPT, local store and the MATHILDA microprogrammable processor are irrelevant to the modelling of the Disk Controller, and will be ignored in the following.

## 4.2. Disk Characteristics.

As mentioned in section 4.1.6 each track-sector contains only one recording block.

This track-sector organisation is actually established through combined functions in disk hardware and supporting hardware.

The recording block is not further divided into subblocks. Information normally recorded in a header subblock such as physical track/sector identification, logical identification (fileid, pageid) is in this system stored in connexion with data. The processing of header information, which is performed by functions implemented in soft - and firmware, does not influence process synchronization mechanisms, and will therefore not be discussed in detail in this paper.

The logical sector numbering (i.e. the numbering used by software loved programs) is again about to the physical socre

The logical sector numbering (i.e. the numbering used by software level programs) is equivalent to the physical sector numbering. This organisation enables the disk controller if it is designed properly - to transfer physically consecutive track-sector blocks between disks and Main Memory, and such requests can actually be specified from software level programs.

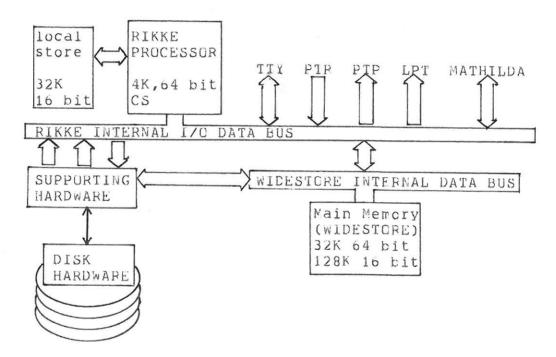

# 4.3. The Levels of the Disk Controller.

As mentioned in section 4.1 the disk controller is realized by functions implemented in soft- firm- or hardware.

The description in the following will fix the border-lines between the three levels. However these fixed lines are only assumed for description purposes. They can gradually move upwards or downwards during development and implementation of the disk controller. This flexibility exists because of the architecture and configuration of the experimental Computer System (Fig. 4.1.).

As an example it can be mentioned that all memory-side transfers (i.e. between Supporting Hardware and Main Memory), which in the following are modelled as if implemented as hardware functions, will actually, in the first 'version' of the disk controller, be 'simulated' in firmware. This simulation is done by using the connexions between the Supporting Hardware and the internal data bus of WIDESTORE on one hand, and the internal I/O data bus of RIKKE on the other.

# 4.3.1. The Software Level of the Disk Controller.

Five types of requests concerning data transfers can be submitted by application programs ( OS filemanager, DB manager, user programs etc. ) to the software part of the Disk Controller.

a) READ RANDOM.

Transfer a single sector, which constitutes a

quest vector.

- single block of a randomly structured file, from Disk to Main Memory.

All necessary control information (sectorno., memmory address, cylinder, etc.) is stored in a re-

- b) WRITE RANDOM. Transfer a single block (sector) of a randomly organized file, from Main Memory to Disk.

- c) READ CONSEC.

Transfer several contiguous sectors belonging to the same file from Disk to Main Memory. This re-

quest is used for multi-files, where each subfile is a consecutively structured file (i.e. data blocks occupy contiguous sectors on secondary storage). This allow for logical page sizes, which is a multiple of physical sector size.

d) WRITE CONSEC.

Transfer several blocks, which occupy contiguous memory positions, to contiguous sectors on disk surface.

e) FORMAT TRACK.

A complete track will be overwritten and each sector initialized to be considered as 'not-oc-cupied'.

This request is not discussed in the succeding chapters describing firmware level and hardware level functions. The main logic of the request will be implemented as firmware level functions, which obviously occupy the disk resources in the disk controller for a complete revolution of the disks.

Disk Controller support for access methods for file structures, other than those supported by operations a)-d) (i.e. random file and consecutive multi-files), should be considered, and integrated in the disk controller. For example chained and indexed structured files. The present design does not provide for these more sophisticated services, but was made in anticipation of the need; adding these at this level should be a straightforward operation.

The software level part of the disk controller will 'unblock' CONSEC requests into simple requests, each for a single sector and store these new requests in a queue together with the RANDOM requests.

The organization of the Queue (Request Queue) is discussed in section 6.1.1.

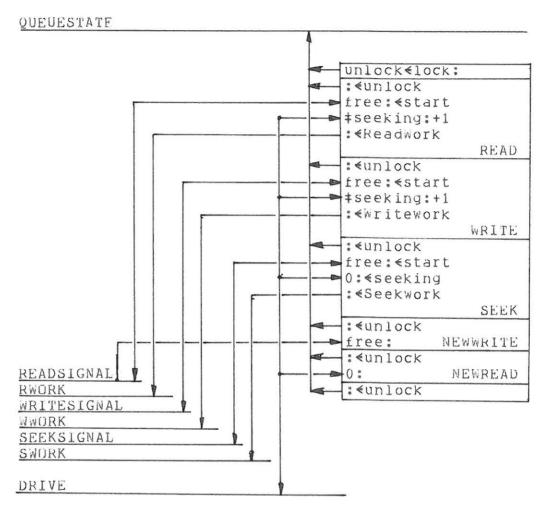

#### 4.3.2. The Firmware level.

This level will be described in detail in Chapter 6. The firmware level functions process the Request Queue.

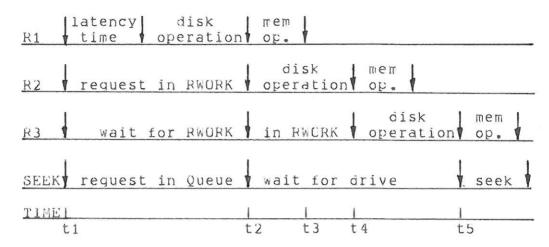

If the next request is for the current track, then a firmware readsector— or writesector function will be called; if not, a seek function will be called first.

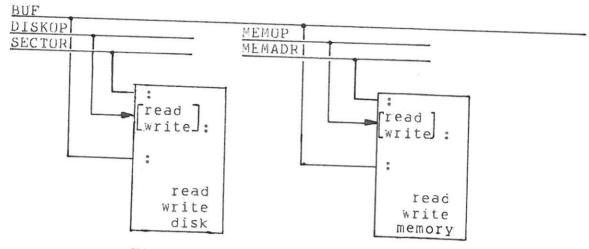

The firmware level Read Sector function signals 2 supporting hardware functions: one to transfer disk-information to a local channel memory buffer; another to transfer data in a local channel memory buffer to Main Memory.

The firmware level Write sector function signals two hardware level functions: one to transfer a Main Memory buffer to a local channel buffer; another to transfer data in a local channel buffer to the disks.

#### 4.3.3. The Hardware Level.

The Hardware Level functions of the disk controller are discussed in detail in Chapter 5.

As mentioned in the previous section, four transfer functions are implemented in supporting hardware. Two

of these control the disk-hardware and two others control the functions of WIDESTORE.

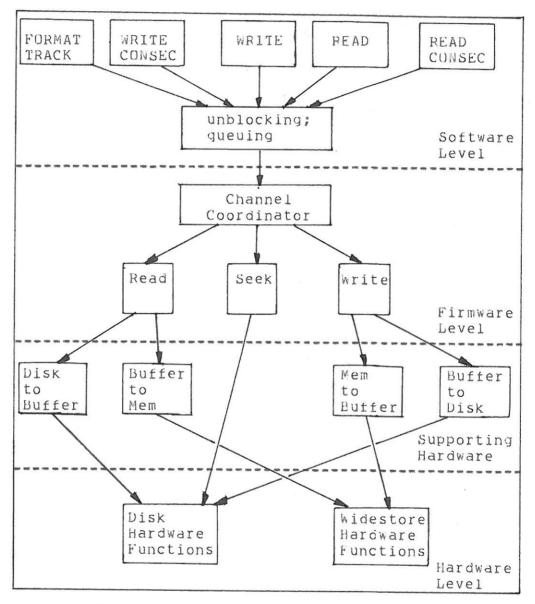

A complete picture of the levels in the Disk-Controller is given in Fig. 4.2..

Fig. 4.2: Disk-Controller (overview).

The model is incomplete. Its virtue lies in that it "slices" the Disk Controller design into levels, making smaller and more managable parts, thus providing a good functional overview.

In the next two chapters the Supporting Hardware and the Supporting Firmware are shown in the true detail.

#### 4.4. Relevance.

The idea of implementing device controllers or channel processors as a mix of software, firmware and hardware functions is certainly not new. The strategy has been used extensively both for experimental device controllers and for production machines - among others IBM System 370 ([15],[16]).

The design shown is original, although perhaps not entirely novel. It represent an acceptable solution to a set of peculiar problems:

- a) RIKKE's need for a direct access mass storage device.

- b) Aarhus University's need for a flexible storage system (attached to RIKKE) that is conducive to future development, research and experimentation (this is a reason for precluding an all-hardware device).

The author chose to 'kill two birds with one stone', and to develop the design needed for illustrative purposes (rather than use an existing one), in order to help further the RIKKE development process.

# 5. THE HARDWARE LEVEL.

The Disk Controller is designed to provide various degrees of service sophistication (i.e. it is not a fixed-purpose device) as well as to allow for future funtional evolution (being an experimental device). The main logic of the device is implemented in a combination of firmware and software, to gain this flexibility.

However, there are some specialized tasks which are more economically performed by supporting hardware.

In addition, other tasks have to be performed by hardware functions, because of timing requirements.

# 5.1. The Elements of the supporting Hardware.

The supporting hardware can logically be divided into the following groups.

# 5.1.1 Two buffers of 256 16-bit words each.

The buffers are connected to the main data bus system of the supporting hardware. The addressing latches for selecting a specific word in these local memory buffers will be incremented automatically during a block-read or block-write process. The two buffers will be refered to as Buf A and Buf B.

# 5.1.2 Input Data Bus System.

The input data bus system has 2 possible input sources, and two possible output destinations. The latter are local buffers, accesible through use of direct memory access (DMA). A 16-bit data word can be gated from any one source to one of the destinations.

# 5.1.3 Output Data Bus System.

Data words from one of the two local buffers can be gated onto the output data bus. Depending on the state of the control signals the information on the bus will be transfered to one of the destinations.

# 5.1.4. Memory Bus Control Logic.

A unit, realized as a hardwired program, which controls the flow of data from a local buffer to an output destination, and from an input source to any of the two local buffers.

#### NOTE 1:

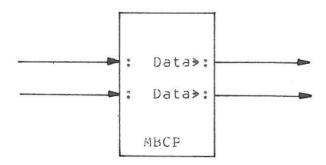

So far the following objects for modelling have been identified inside the supporting hardware:

- a) A Memory Bus Control Process (MBCP), which administers the usage of two local memory buffers, and two local bus systems.

- b) Two input sources shared between the Memory Bus Control Process and two unspecified producer processes.

- c) Two output destinations, which are shared between the Memory Bus Control Process and two consumer processes.

The Pictorial Representation for this system is shown in Fig.5.1. (it is intentionally incomplete, lacking control logic).

Fig. 5.1 The Memory Bus control process.

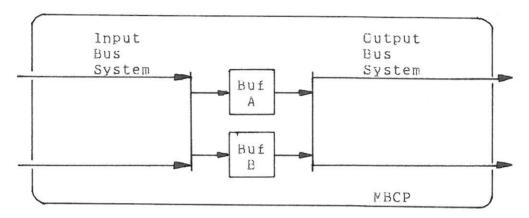

The local units administered by the Memory Bus Control Process are illustrated in Fig. 5.2., which shows how data may flow through the MBCP.

Fig. 5.2: Internal bus structures for MBCP.

5.1.5 Parallel to Serial Conversion, and Cyclic Redundancy Code Generation units.

During a disk-write operation the information in one of the local buffers is transfered using the output data bus system and DMA cycles to a parallel to serial conversion unit. Serial data is sent from the unit to a specific disk and as data words are being transfered a cyclic redundancy code (CRC) is generated and appended to the data stream to be recorded on the disk.

5.1.6 Serial to Parallel conversion and CRC Check Units.

During a disk to buffer transfer the bit stream from the disk is packed into 16 bit words and gated onto the input bus. A cyclic redundancy code is compiled and compared against the CFC check-word that was read in after the data-block. A status flag indicates the result of the comparison.

#### 5.1.7. Input Port.

A 16-bit-wide input port connects the supporting hardware with the Main Memory of the computer system.

### 5.1.8 Output Port.

Similar to the input port a 16-bit-wide parallel output port connects the supporting hardware to Main Memory.

# 5.1.9 Parallel Input and Output Port Logic.

The supporting hardware is directly connected to the Main Memory of the computer system by means of an input, output and address port. The Main Memory is equipped with a data- and address port multiplexer ([11],[13]), which enables the supporting hardware to be in charge of block transfers between one of its own memory buffers and a buffer in the Main Memory of the computer system.

The Parallel Input Logic and the Parallel Output Logic control block transfers, and communicate with the multiplexer of the Main Memory.

# NOTE 2:

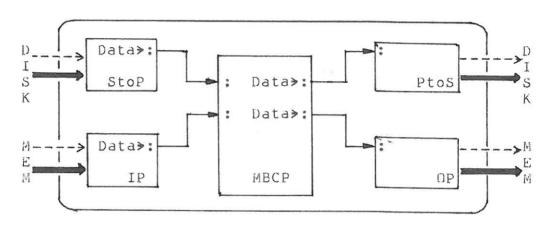

The system modelled in Fig.5.1 can now be extended with the following independent processes:

- a) Serial to Parallel Conversion Process (StoP), sending data to the Memory Bus Control Process, and receiving serial data from the disk hardware.

- b) Parallel to Serial Conversion Process (PtoS), receiving data from the Memory Bus Control Process, and producing serial formatted data to the disk hardware.

- c) Parallel Input Port Process (IP), sending data to the Memory Bus Control Process, and receiving data from Main Memory.

- d) Parallel Output Port Process (OP), receiving data from the Memory Bus Control Process, and sending data to Main Memory.

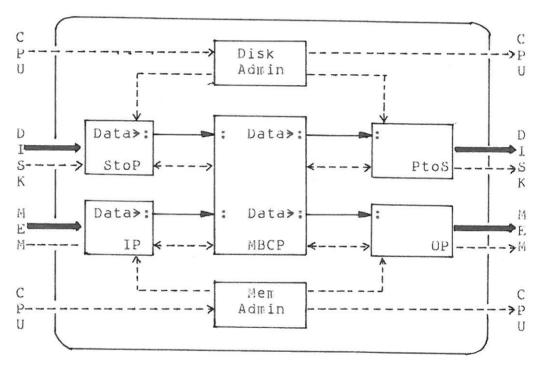

The Pictorial Representation of these independent processes and the Main Memory Bus Control Process is given in Fig.5.3. (it is still incomplete). The figure also indicates how the supporting hardware communicates with its environment. Data flow and control flow not analysed on this level of description are pictured through use of dotted lines and heavy lines, respectively.

Fig. 5.3: The Memory Control and The 1/0 Units.

# 5.1.10 Sector Counter and Sector Match Units.

For each independent disk-unit administered by the supporting hardware there exists a sector address counter which is set appropriately when index or sector pulses, sent by the physical disk-hardware, are captured by the system. When requests for disk transfer are initiated, the actual disk-to-buffer channel process will be delayed until a match between the requested sector address and the internal sector counter for the specified disk-unit exists. Upon the match all resources required for transfer of data between a local buffer and disk are reset by this unit. The disk I/O logic is signalled to start.

# 5.1.11. Parallel Port Control Unit.

When requests for memory to buffer or for buffer to memory transfers are initiated, all resources required to transfer data between Main Memory and local buffer are reset by this unit, which signals the I/O processing units to start.

# 5.1.12 Direct Memory Access (DMA) Facilities.

A DMA facility is provided to effect whole block-transfers between the local buffers on one hand and either disk or Main Memory on the other. The decision was made to equip the supporting hardware logic with DMA facilities to relieve the disk-channel-controller of the time-consuming and monotonous job of incrementing address-pointers and monitoring 1/0 flags.

When a block transfer has been initiated, a status flag reflects the busy situation; It prevents the disk-channel-controller (if it is designed properly) from interfering with the 'uncompleted' channel-process. The data transfer process will terminate when an internal word-counter reaches its limit (256), i.e. when the local buffer is full. Also, the transfer will be forced to a completion if any new process that conflicts with the current process is initiated.

#### NOTE 3:

The system modelled in Fig.5.3 can now be extended with:

- a) Disk I/O Request Process (Disk Admin), which receives control information from the Main Computer and from the disk hardware. This process signals on one hand either PtoS or StoP, and on the other hand the disk hardware, to start processing

- b) Memory I/O Request Process (Mem Admin), which also receives control information from the computer system. It signals the parallel I/O processes as well as the Main Memory multiplexer to start a communication.

In these pictorial representations there is no box representing the DMA. It (i.e. the DMA) is an effect achieved through the cooperative behaviour of MBCP and the I/O processes, thus the logic needed to im-

plement it is distributed among these components; to show it in detail would destroy the modularity at the present level of description.

Fig. 5.4 gives an overview of the channel-control system, incrementally developed through the previous sections. The model does not illustrate all communication signals necessary to control the system, but gives an overview of how the processes, realized in the supporting hardware, are connected and how they independently communicate with the environment.

Fig. 5.4: Channel System.

#### 5.1.13 Arm Positioning Control Units.

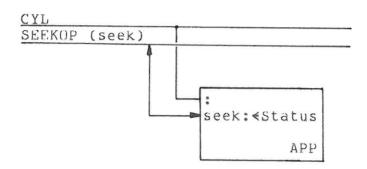

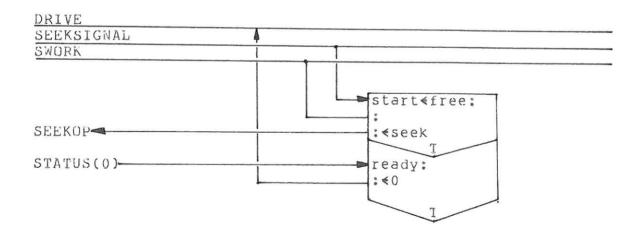

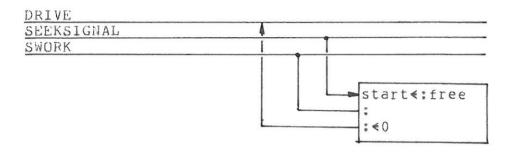

The task of positioning the read/write heads is simple compared to the task of administering data-transfers. Built-in logic inside the disk-hardware is capable of moving arms to a specific cylinder on request and of signalling to the outside world that the process has terminated. Therefore, further hardware

support is not needed because firm—and software mechanisms can easily take care of the arm positioning. However, because the supporting hardware has the additional purpose of providing a single uniform interface to all of the disk functions, requests to position arms as well as status information for termination, are both gated through the supporting hardware.

At the supporting hardware level the Arm Positioning Process is an independent process.

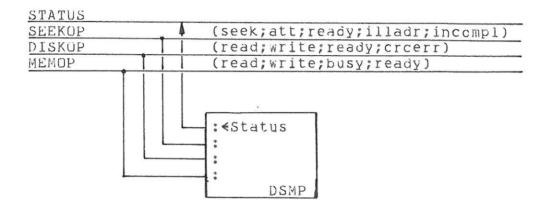

#### 5.1.14 Disk-hardware Status Monitor Unit.

It is the responsibility of the higher-level firmand software logic to drive the supporting hardware. To do so meaningfully (e.g., to avoide interference problems, and disable data transfers during seek operations), the higher level logic coordinates requests with disk status information.

The Disk Hardware Status Monitor is the interface unit, through which all feedback signals from the disk unit are routed to the higher level logic.

# 5.1.15 Suppporting hardware services.

In the previous sections, an overview of the collection of functions provided by the supporting hardware was given. With those, the following services can be performed:

- Read a block of data from disk to a local buffer, involving the component processes:

- a) Disk I/O Request Process (Disk Admin),

- b) Serial to parallel conversion process (StoP).

- c) Memory Bus Control process (MBCF).

- 2. Write a block of data from a local buffer to disk, involving the component processes:

- a) Disk Admin.

- b) Parallel to serial conversion process (PtoS)

- c) MBCP.

- 3. Read a block of data from Main Memory to a local buffer, involving the component processes:

- a) Memory I/O Request process (Mem Admin).

- b) Parallel input port process (IP).

- c) MBCP.

- 4. Write a block of data from a local buffer to Main Memory, involving the component processes:

- a) Mem Admin.

- b) Parallel output port process (OP).

- c) MBCP

- 5. Arm Positioning. Controlled entirely by the arm positioning process (APP).

- 6. Status Feed-back.

Provided by the disk status monitor process DSMP.

In the next sections a complete model of the supporting hardware is given.

For each component process the following are specified:

- a) The actions performed.

- b) The enabling conditions.

- c) The global resources required.

At this level of description the functions of Diskhardware and Main Memory Multiplexer are irrelevant, since the mechanisms to control these functions are local to each process.

In The Pictorial Representation these mechanisms are eliminated (3.1.1), and in The System Language Description they are illustrated as function or routine calls (3.1.1, 3.1.3).

The model of the disc controller presented in the next chapters is for the special case where a single physical disk drive is connected to the system.

The model can easily be upgraded to a more general case - by duplicating all relevant disk-side variables and adjusting logic trivially.

# 5.2 The Memory Bus Control Process.

The data path architecture of the MBCP (Fig. 5.2.) is intended to support a double buffering strategy in transfering a sequence of physical consecutive sectors from the disk surface to Main Memory or vice versa. The strategy will minimize the transfer time for multi-sector block transfers.

## To illustrate this consider:

- A sector read operation, which involve the following steps:

- a) transfer a sector to one of the two local buffers, and check header information.

- b) depending on the result of the previous operation, then transfer the data in the buffer to Main Memory.

With a suitable design of the MBCP, which is the only process participating in both disk-side and memory-side operations, step b) can proceed independently with a new disk-side transfer, now involving the remaining buffer.

This strategy can be used for a series of requests, assuming that transission rates are higher for memory transfers than for disk transfers.

This use of the supporting hardware is reflected in the design of the bus gate and memory gate control of MBCP. As the system is only equipped with 2 local buffers, and as any transfer along a bus involves a buffer, only two data paths can be active at any point in time.

Therefore, without losing flexibility, the following can be assumed:

- a) at any point in time one buffer (Bufa or Bufb) is dedicated for disk transfers.

- b) and the remaining buffer is dedicated for memory transfers.

These restrictions simplify the information needed to control the MBCP.

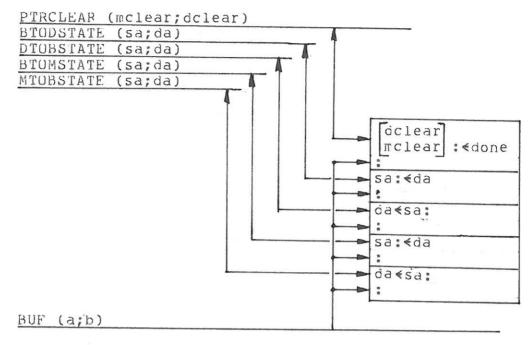

#### 5.2.1. The component processes of MBCP.

the following activities provided by the MBCP can be identified:

a) Clear a buffer pointer for Bufa or Bufb. Upon initialization of a new disk-side transfer the

- BMCP is signaled to clear a pointer (Bufaptr or Bufbptr).

- b) Transfer a single word from any of the two sources to a buffer location. Whenever one of the two 'source' processes signals 'data available', the MBCP will act.

- c) Transfer the contents of a buffer location to any of the two destinations. Whenever one of the two 'destination' processes signals 'space available' the MBCP will act.

To be able to model the MBCP the following definitions are necessary:

# DEFINITIONS 1:

- BUF := Control information, sent to the supporting hardware, specifying buffer allocation for disk- and memory-side data transfers. The information is,

- a ≡ Bufa allocated for disk-side transfers, and (5.2.) Bufb allocated for memory-side transfers;

- b = Bufb allocated for disk-side transfers.

- BTODPORT ::= Repository for a single word produced by MBCP, to be comsumed by the Parallel to Serial Conversion Process.

- BTODSTATE::= State variable for BTODPORT, being sa = space available, i.e. signal to MBCP to produce a new word;

- da = data available, i.e. previous word not consumed.

- DTOBPORT ::= Repository for a single word produced by the Serial to Parallel Conversion Process (i.e. from the disk).

- DTOBSTATE::= State variable for DICBSTATE, being

da = data available;

sa = previous word consumed.

- BTOMPORT ::= Repository for a single word produced by MBCP, to be consumed by the Parallel Output Process.

BTOMSTATE::= State variable for BTOMPCRT, being

sa = space available.

da = data available.

MTOBPORT ::= Repository for a single word produced by the Parallel Input Process.

MTOBSTATE::= State variable for MTCBPCRT, being

da ≡ data available; sa ≡ space available.

PTRCLEAR ::= Signal to clear local buffer pointer, being

dclear ≡ clear bufferpointer for the buffer allocated for disk-side transfers.

mclear  $\Xi$  clear buffer pointer for the buffer allocated for memory-side transfers.

The internal logic of the Memory Bus Control Unit can only handle a single activity at a time, i.e. it is realized as a sequential program containing a central condition polling and control dispatching facilities. A priority is enforced by the system, which gives the synchronous disk-side operations priority.

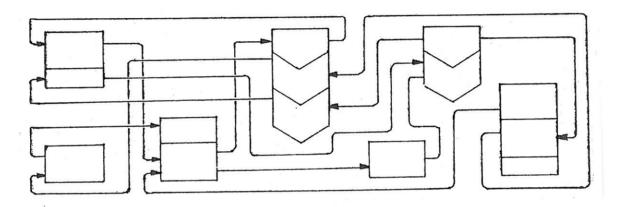

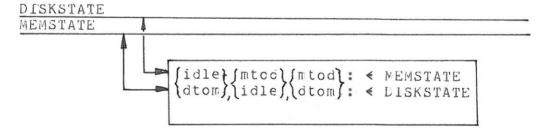

As a consequence of this, the PRI combined construct of section 3.6.2 is used to model the MBCP (see Fig. 5.5).

The only relevant information to be illustrated in the pictorial representation is the control information (BUF) and the control signals (BTODSTATE etc.).