## Exponentiation, Modular Multiplication and VLSI Implementation of High-Speed RSA Cryptography

Ph.D Thesis

by

Holger Orup

Department of Computer Science, University of Aarhus, DK-8000 Aarhus C, Denmark

August 1995

# Danish Summary (Dansk Resumé)

Denne afhandling er resultatet af et Ph.D. studium udført i perioden fra 1990 til 1995. Studiet foregik ved Datalogisk Afdeling, Aarhus Universitet under vejledning af Lektor Peter Møller-Nielsen. I perioden fra september 1990 til januar 1993 blev en del af arbejdet udført ved Udviklingsafdelingen, Tele Danmark/Jydsk Telefon.

## Problemstilling

Afhandlingen er motiveret af en problemstilling, der især er kendt fra anvendelsen af RSA kryptosystemet: Den praktiske anvendelighed af systemet er afhængig af hastigheden, hvormed man er i stand til at udføre de tilhørende transformationer af data. For at undgå at anvendelsen af kryptografi bliver en flaskehals i de elektroniske kommunikationssystemer, er det vigtigt at opnå en tilstrækkelig høj transformationshastighed.

Transformationerne, der benyttes i RSA kryptosystemet, er baseret på en aritmetisk operation på formen  $M^e \mod m$  kaldet modulo eksponentiering. Da operandernes størrelse typisk er på 500 bit eller mere, er modulo eksponentiering en forholdsvis tidskrævende operation. I 1990, da projektet startede, var den hurtigste implementering af modulo eksponentiering i stand til at foretage beregningerne med en hastighed på 29 Kbit/sek ved en operandstørrelse på 512 bit.

## Formål

Hovedformålet med arbejdet præsenteret i afhandlingen er at undersøge mulighederne for at forøge hastigheden af modulo eksponentiering ved hjælp af specialdesignede VLSI (Very Large Scale Integrated) kredsløb. Den konkrete målsætning for projektet udført ved Tele Danmark/Jydsk Telefon var at konstruere et VLSI kredsløb, som kunne foretage module eksponentiering af operander på 561 bit med en hastighed på minimum 64 Kbit/sek. Endvidere skulle kredsløbet implementeres på en enkelt chip.

Formålet med selve afhandlingen er at beskrive resultaterne opnået under studiet og at sætte disse i perspektiv ved en diskussion og sammenligning med resultater kendt fra litteraturen. Desuden er det hensigten at give læseren indsigt i de teknikker, der kan anvendes til at effektivisere modulo exponentiering.

## Tilgangsvinkel

Den valgte tilgangsvinkel er baseret på en simpel analyse af VLSI implementeringer, der var kendt i 1990: Alle de hurtigste implementeringer bruger det samme antal klokke perioder til at foretage en modulo eksponentiering, og forskellen i hastighed kan tilsyneladende alene tilskrives forskellen i den anvendte klokkefrekvens. Dette kunne tyde på, at fremskridt i hastighed alene er nået på baggrund af hurtigere kredslebsteknologier, og ikke på grund af forbedrede beregningsmetoder. Derfor blev det besluttet at undersøge mulighederne for at udvikle nye og mere effektive beregningsmetoder, som er velegnede til VLSI implementering.

## Afhandlingens struktur

Afhandlingen er opdelt i to separate dele. Den sidste del består af fire artikler, gengivet i appendices A-D, samt en rapport med beskrivelser af RSA kredsen i appendix E. Alle dokumenterne er skrevet i perioden fra 1990 til 1995. Artiklerne præsenterer nogle af de opnåede resultater. Den første del af afhandlingen indeholder en relativt udtømmende oversigt over relevante resultater fra litteraturen. Disse resultater diskuteres og sammenholdes med

ii

resultaterne opnået under studiet. Desuden er projektet med konstruktion af RSA kredsen beskrevet.

### Oversigtsdelen

De første fire kapitler udgør en hierakisk struktureret fremstilling, hvor problemstillingerne identificeret på ét niveau løses ved et sæt teknikker, der introducerer et nyt sæt lavere liggende problemstillinger. Det nederste niveau i hierakiet er kredsløbsniveauet, hvor løsningerne realiseres ved en kredsløbsarkitektur, der er i stand til at udføre en specifik beregningsmetode. Det femte kapitel beskriver den senest udviklede beregningsmetode. Metoden repræsenterer en markant fremgang i de opnåelige beregningshastigheder og må ses som et produkt af at samle erfaringerne fra de første fire kapitler. Endelig afsluttes oversigtsdelen med en kortfattet konklusion, der præciserer de gennemgående løsningsstrategier og -teknikker.

I det følgende er de væsntligste opnåede resultater kort skitseret. Resultaterne er opdelt efter emne:

- **Eksponentierings metoder.** Da eksponentiering foretages ved gentagen multiplikation, er litteraturen præget af metoder, der forsøger at minimere antallet of multiplikationsoperationer. Imidlertid er det muligt at parallellisere beregningen og herved opnå en kortere beregningstid end det er muligt med sekventielle metoder. Dette er på trods af, at det samlede antal multiplikationer ikke er minimalt. Det væsentligste bidrag til dette emneområde er en metode, der anvender den parallelle beregningsstrategi uden en samtidig signifikant forøgelse af VLSI kredsløbets størrelse. Dette opnåes ved at anvende en samlebåndsteknik (eng: pipelining). Det synes vanskeligt at opnå yderligere fremgang i metoderne til modulo eksponentiering.

- Modulo multiplikations metoder. Der er til gengæld store muligheder for at forøge hastigheden af modulo multiplikation. I denne afhandling er den gennemgående strategi at opnå mere effektive beregninger af modulo multiplikation ved at benytte såkaldte høj-radix metoder. Den basale idé bag høj-radix metoder er at reduce antallet af additioner. Dette kan udtrykke sig ved, at antallet af klokkeperioder per multiplikation reduceres. Et af de største problemer ved høj-radix metoderne

er, at det reducerede antal klokkeperioder ledsages af en forøgelse af klokkeperiodens længde. Et af de væsentligste resultater i afhandlingen er en særdeles effektiv høj-radix metode, hvor klokkeperiodens længde ikke forøges ved stigende radices.

**VLSI implementering.** En RSA processor er blevet konstrueret, fabrikeret og afprøvet. Den er fuld funktionsdygtig og lever op til kravene, der blev specificeret ved projektets begyndelse. Det viser sig at være den hidtil hurtigste kendte implementation af modulo exponentiering.

## Artikeldelen

I de fem appendices A-E er gengivet fire artikler samt en kortfattet rapport. Den første artikel, publiceret i [OSA90a], danner grundlag for beregningsmetoderne, der benyttes af RSA processoren. Den anden artikel, publiceret i [OK91], præsenterer en module multiplikations metode, der i udstrakt grad udnytter egenskaberne ved såkaldte redundante repræsentationer. Endvidere beskrives en velegnet kredsløbsarkitektur, som udnytter samlebåndsteknikken til at formindske størrelsen af kredsløbet. Den tredie artikel beskriver strategien bag arbejdet med at reducere arealet af RSA processoren. Artiklen indeholder en oversigt over effekten af de anvendte teknikker. Den fjerde artikel, publiceret i [Oru95], præsenterer en særdeles effektiv høj-radix modulo multiplikationsmetode. Metoden baserer sig på en kombination af tidligere kendte teknikker. Endelig er en rapport inkluderet. Rapporten indeholder nogle af de væsentligste data vedrørende RSA processorens funktionalitet.

## Preface

This thesis is the result of a Ph.D. study carried out in the period from 1990 to 1995. The study was done at the Department of Computer Science, University of Aarhus, Denmark, and supervised by Associate Professor Peter Møller-Nielsen. As an integral part of the study I was at the Research and Development Department, Tele Danmark/Jydsk Telefon, Denmark, in the period from September 1990 to January 1993.

The study was driven by a specific problem known from the field of public key cryptography: In order to avoid the application of cryptography to be a bottle-neck in a communication system, it is necessary to perform the cryptographic transformations at a rate corresponding to the transmission rate of the communication channel. In the RSA public key crypto system, and in other public key systems as well, the transformation rate is limited by the speed of which modular exponentiation can be performed. The aim of the study was, primarily, to implement a special-purpose processor by means of the VLSI circuit technology and, hereby, to demonstrate that the transformations used in RSA cryptography can be performed at 64 Kbit/sec, corresponding to the transmission rate of an ISDN channel.

The thesis is organised as two major parts. The first part constitutes a relatively exhaustive description of the relevant research results on methods for fast computation of modular exponentials. The description provides an insight into the properties of the arithmetical operations used. It is discussed how these properties, through various optimisation techniques, can be utilised to obtain efficient computation methods. Finally, the hardware implementation project carried out at Tele Danmark/Jydsk Telefon is described. The second part of the thesis is structured as five separate papers. The papers presents the results obtained during the study.

My interest for the problem treated in this thesis was born in 1989 during a conversation with two fellow students. One of the fellows was taking a course in Cryptology and had been faced with the problem of RSA cryptography. Hence, he asked

"Is it possible to construct a VLSI processor that performs fast computations of expressions of the form  $M^e \mod m$ ?"

We got the opportunity to study the problem in further detail and in January 1990 we completed our Master's thesis [OSA90b] on the subject. The results

were described in an article [OSA90a] and presented at the Eurocrypt '90 Conference in Aarhus, Denmark, May 1990. Furthermore, a report [OS90] on improvements of the results of the Master's thesis was completed in June 1990.

After receiving my Master's degree I applied for, and got, a Ph.D. scholarship in the summer 1990. During the Eurocrypt '90 Conference a contact to Tele Danmark/Jydsk Telefon was established. A cooperation was initiated in September 1990 with the purpose of implementing a VLSI processor. A computation method and an associated architecture, mainly based on the article from Eurocrypt '90, was chosen for the implementation. The processor was sent for fabrication in January 1993. It was presented at the Hot Chip VI Symposium, Standford, California, August 1994 [Oru94]. In the first stage of the project, for a period of approximately a year, the work was done in cooperation with Erik Svendsen.

In the fall 1990 Professor Peter Kornerup, Odense University, Denmark, gave me an introduction to the field of Computer Arithmetic and explained that some of the ideas we had presented at Eurocrypt '90 were well-known techniques from that field. This resulted in the article [OK91], presented at the 10th Symposium on Computer Arithmetic, Grenoble, France, June 1991. Finally, at the 12th Symposium on Computer Arithmetic, Bath, England, July 1995, the results of my latest work were presented [Oru95].

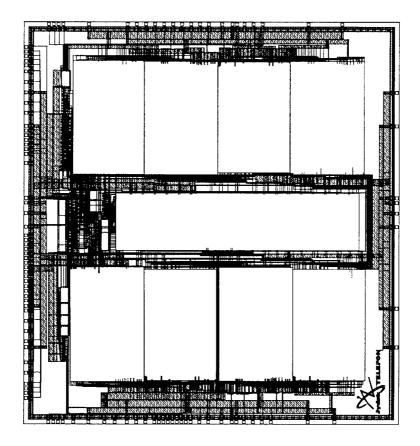

The photography on the front cover of the thesis shows the processor that was implemented through the cooperation with Tele Danmark/Jydsk Telefon.

Aarhus, Denmark August, 1995 Holger Orup

## Acknowledgements

I am truly grateful for the inspiration, advice and support I have received from many people during my work on this thesis. It is not possible to mention everyone whose interaction contributed to this work, but I would like to thank some of the people that have helped me the most.

First of all I would like to express my deepest gratitude to my wife Hanne for her all-out support.

At University of Aarhus I would like to thank my supervisor Peter Møller-

Nielsen for his help, advice and support during my studies. I would also like to thank Ole Caprani and Henrik Esbensen for many fruitful discussions and suggestions.

At Tele Danmark/Jydsk Telefon I would like to thank my former colleagues at the Research and Development Department. A special thank to Poul Gødsvang and Finn Barrett for many inspiring discussions. I would also like to thank Erik Svendsen, who was directly involved in the design of the RSA processor, as well as John Thorup, who designed and constructed the boards for testing the processor. Finally, I owe thanks to Palle Brandt for taking the initiative to establish the project of implementing the RSA processor.

Thanks to Peter Kornerup, Odense University, for introducing me to the field of Computer Arithmetic and for constructive discussions, advice and support.

I am also very grateful for the financial support provided by the Department of Computer Science, University of Aarhus and by the AIDA research project<sup>1</sup>.

Aarhus, Denmark August, 1995 Holger Orup

<sup>&</sup>lt;sup>1</sup>Danish Natural Science Research Council, grant no, 5.21.08.02

viii

# Contents

| 1        | $\operatorname{Intr}$ | coduction 1                                                                                                                           |  |

|----------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|

|          | 1.1                   | The Need for Crypyography                                                                                                             |  |

|          |                       | 1.1.1 Information Integrity Functions                                                                                                 |  |

|          |                       | 1.1.2 Cryptography $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 4$                                                 |  |

|          |                       | 1.1.3 The RSA Public Key Crypto System                                                                                                |  |

|          |                       | 1.1.4 Other Public Key Crypto Systems                                                                                                 |  |

|          |                       | 1.1.5 Hardware Support                                                                                                                |  |

|          | 1.2                   | Purpose of the Thesis                                                                                                                 |  |

|          | 1.3                   | Chosen Approach                                                                                                                       |  |

|          | 1.4                   | Organisation of the Thesis                                                                                                            |  |

|          | 1.5                   | Description of Papers                                                                                                                 |  |

| <b>2</b> | Exp                   | ponentiation 21                                                                                                                       |  |

|          | 2.1                   | Fewer Multiplications                                                                                                                 |  |

|          |                       | 2.1.1 The <i>m</i> -ary Method $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 24$                             |  |

|          |                       | 2.1.1 The <i>m</i> -ary Method $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 24$                                           |  |

|          |                       | 2.1.1The <i>m</i> -ary Method                                                                                                         |  |

|          |                       |                                                                                                                                       |  |

|          | 2.2                   | 2.1.2 Thurber's Modification                                                                                                          |  |

|          | 2.2<br>2.3            | 2.1.2Thurber's Modification302.1.3Methods Based on Heuristics33                                                                       |  |

|          |                       | 2.1.2Thurber's Modification302.1.3Methods Based on Heuristics33Theoretical Limits36                                                   |  |

|          |                       | 2.1.2Thurber's Modification302.1.3Methods Based on Heuristics33Theoretical Limits36Parallel Computation38                             |  |

|          |                       | 2.1.2Thurber's Modification302.1.3Methods Based on Heuristics33Theoretical Limits36Parallel Computation382.3.1Pipelined Computation42 |  |

| 3 | Moo                                       | dular N                                 | Aultiplication                                                    | 57  |  |  |  |  |

|---|-------------------------------------------|-----------------------------------------|-------------------------------------------------------------------|-----|--|--|--|--|

|   | 3.1                                       | A Sim                                   | ple Modular Addition Method                                       | 60  |  |  |  |  |

|   | 3.2                                       | Integer                                 | Representation and Arithmetic                                     | 61  |  |  |  |  |

|   |                                           | 3.2.1                                   | Non-Redundant Representation $\ldots \ldots \ldots \ldots \ldots$ | 62  |  |  |  |  |

|   |                                           | 3.2.2                                   | Redundant Representation                                          | 65  |  |  |  |  |

|   |                                           | 3.2.3                                   | Comparison of Non-Redundant and Redundant Representations         | 73  |  |  |  |  |

|   | 3.3                                       | Residu                                  | e Representation and Arithmetic                                   | 74  |  |  |  |  |

|   | 3.4                                       | Left-to                                 | -Right Modular Multiplication                                     |     |  |  |  |  |

|   |                                           | Metho                                   | d                                                                 | 77  |  |  |  |  |

|   | 3.5                                       | Utilisa                                 | tion of Parallel Computations                                     | 79  |  |  |  |  |

|   | 3.6                                       | Repres                                  | entation of Intermediate Operands                                 | 83  |  |  |  |  |

|   | 3.7                                       | Compu                                   | itation of Multiples                                              | 86  |  |  |  |  |

|   |                                           | 3.7.1                                   | Multiplier Digit Set and Quotient Digit Set                       | 86  |  |  |  |  |

|   |                                           | 3.7.2                                   | Representation of Multiplic<br>and and Modulus                    | 88  |  |  |  |  |

|   |                                           | 3.7.3                                   | Representation and Range of Resulting Multiple                    | 94  |  |  |  |  |

|   | 3.8                                       | .8 Residue Range and Quotient Digit Set |                                                                   |     |  |  |  |  |

|   | 3.9 Scaling of Modulus                    |                                         |                                                                   |     |  |  |  |  |

|   | 3.10 Quotient Determination Methods       |                                         |                                                                   |     |  |  |  |  |

|   |                                           | 3.10.1                                  | Table Look-Up Methods                                             | 105 |  |  |  |  |

|   |                                           | 3.10.2                                  | Analysis of Selection Intervals                                   | 108 |  |  |  |  |

|   |                                           | 3.10.3                                  | Borrow Save and Carry Save Representation                         | 110 |  |  |  |  |

|   |                                           | 3.10.4                                  | Adjusting the Range of Modulus $\ldots \ldots \ldots \ldots$      | 117 |  |  |  |  |

|   | 3.11                                      | Summa                                   | ary and Discussion                                                | 122 |  |  |  |  |

| 4 | Mod                                       | dular E                                 | Exponentiation Processor                                          | 129 |  |  |  |  |

|   | 4.1 Background and History of the Project |                                         |                                                                   |     |  |  |  |  |

|   | 4.2                                       | Proces                                  | sor Description                                                   | 135 |  |  |  |  |

|   |                                           | 4.2.1                                   | Modular Exponentiation Unit                                       | 136 |  |  |  |  |

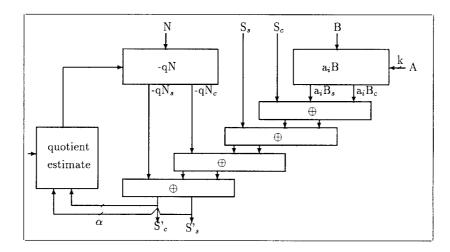

|   |                                           | 4.2.2                                   | Modular Multiplication Unit                                       | 138 |  |  |  |  |

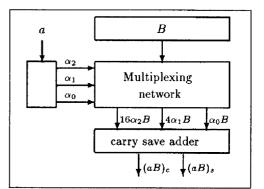

|   |                                           | 4.2.3                                   | Multiple Units                                                    | 143 |  |  |  |  |

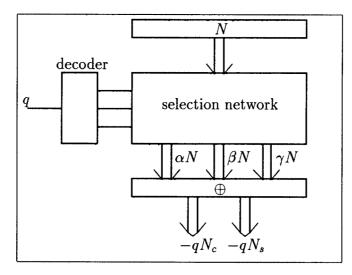

|   |                                           | 4.2.4                                   | Quotient Determination Unit                                       | 146 |  |  |  |  |

|   |                                           | 4.2.5                                   | Control Unit                                                      | 150 |  |  |  |  |

х

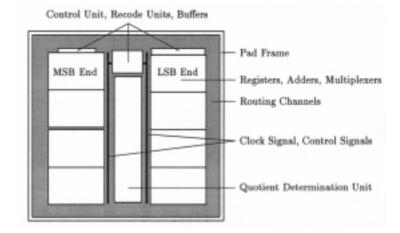

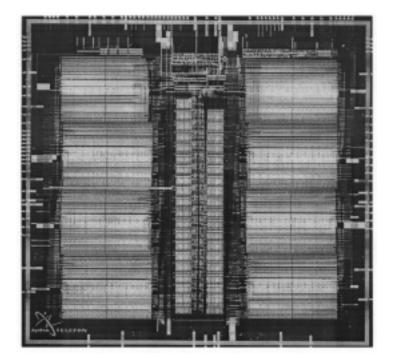

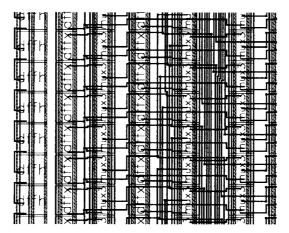

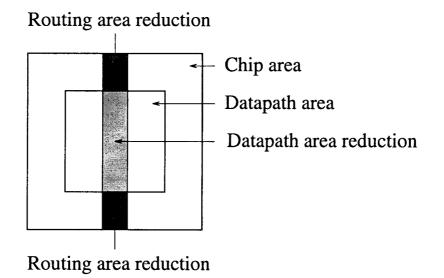

|              | 4.3                                                                                  | Layout                                                                                                                        | 51  |  |  |  |

|--------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|

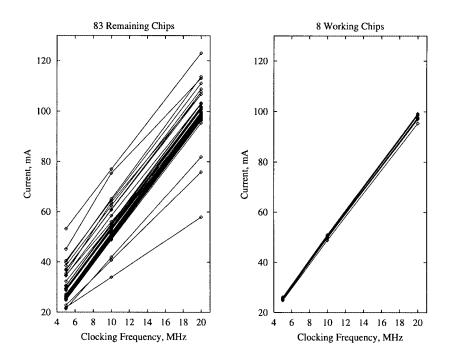

|              | 4.4 Test and Performance                                                             |                                                                                                                               |     |  |  |  |

|              |                                                                                      | 4.4.1 Check of Pin Connections                                                                                                | 54  |  |  |  |

|              |                                                                                      | 4.4.2 Current Measurements on Reset                                                                                           | 54  |  |  |  |

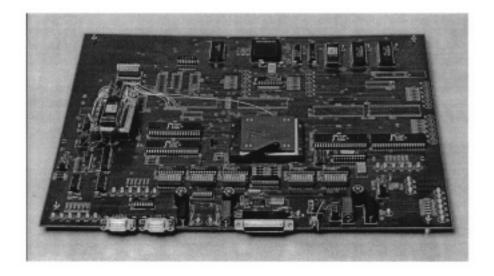

|              |                                                                                      | 4.4.3 Test Board $\ldots \ldots 1$ | 59  |  |  |  |

|              |                                                                                      | 4.4.4 Test of Functionality                                                                                                   | 60  |  |  |  |

|              |                                                                                      | 4.4.5 Performance Mesurements                                                                                                 | .63 |  |  |  |

|              | 4.5                                                                                  | Summary and Discussion                                                                                                        | 66  |  |  |  |

| 5            | Mo                                                                                   | ntgomery Residues 1                                                                                                           | 73  |  |  |  |

|              | 5.1                                                                                  | Montgomery Multiplication                                                                                                     | 75  |  |  |  |

|              | 5.2                                                                                  | Reducing the Recursion Cycle Time                                                                                             | 77  |  |  |  |

|              |                                                                                      | 5.2.1 Optimisation Techniques                                                                                                 | 78  |  |  |  |

|              | 5.3                                                                                  | Additional Processing                                                                                                         | 83  |  |  |  |

|              | 5.4                                                                                  | Summary and Discussion                                                                                                        | 85  |  |  |  |

| 6            | Cor                                                                                  | iclusion 19                                                                                                                   | 91  |  |  |  |

| Bi           | bliog                                                                                | graphy 19                                                                                                                     | 95  |  |  |  |

| $\mathbf{A}$ | VIC                                                                                  | CTOR, an Efficient RSA Hardware Implementation 2                                                                              | 15  |  |  |  |

| в            | A High-Radix Hardware Algorithm for Calculating the Exponential $M^E$ Modulo $N$ 217 |                                                                                                                               |     |  |  |  |

| С            | C Area Reduction for Bit-Sliced Layouts using a Commercial<br>Development System 219 |                                                                                                                               |     |  |  |  |

| D            | Simplifying Quotient Determination in High-Radix Modular<br>Multiplication 223       |                                                                                                                               |     |  |  |  |

| $\mathbf{E}$ | $\mathbf{RS}_{\mathbf{A}}$                                                           | A Processor, Preliminary Engineering Data 22                                                                                  | 23  |  |  |  |

## Chapter 1

## Introduction

This chapter provides an introduction to the subject and purpose of this thesis. Section 1.1 gives a motivation for the work presented. After a brief description of the services provided by cryptography, the RSA public key crypto system is introduced. The complexity of computing modular exponentials, expressions of the form  $M^e \mod m$ , represents the most serious limitation on the applicability of public key cryptography. In Section 1.2 the purpose of this thesis is described: To develop fast hardware implementations for supporting the computations required in RSA cryptography. Section 1.3 describes the approach chosen for achieving the goal of the presented work. Section 1.4 describes the overall organisation of the thesis. Finally, Section 1.5 provides a brief description of the papers included in the Appendices.

## 1.1 The Need for Crypyography

Electronic communication system are quickly overtaking paper-based systems and face-to-face meetings [DMW94]. Every day, millions of people use telephones, fax machines, and computer network for interactions. Sensitive data are transmitted over insecure channels. Landau et al. [LKB<sup>+</sup>94] describe cases, where weak links in the communication system have been used for penetration: In the 1970s thousands of phone conversations about business at IBMs private microwave network were systematically eavesdropped by Soviet intelligence agents. A group of students at the University of Wisconsin forged an email letter of resignation from the director of housing to the chancellor of the university.

The accelerating introduction of electronic communication will increase the importance of *information integrity* [Sim92a], i.e. all the questions concerning privacy, authenticity, authority etc.: Business will tele-connect with customers to sell and bill. Manufactures will electronically query suppliers to check product availability. Insurance companies, doctors and medical centres will carry on electronic exchanges about patient treatment.

Vulnerable communication can easily undermine user's confidence in a system. Hence, there is an urgent need for means to provide for the integrity of information. A very important part of the solutions on the information integrity is cryptographic in nature.

#### **1.1.1** Information Integrity Functions

Information integrity functions for paper-based communication systems have evolved over thousands of years. The needs for parties of the paper-based communication include such functions as listed in Table 1.1 [DMW94]. The table lists a few a the more common functions and is far from complete. The conventional paper-based information integrity functions motivate the need for similar functions in electronic communication and provide a basis for analogies. The same message or transaction that now is handled by a paper-based system will soon be sent by an electronic system, to improve the speed of communication and the cost of handling. As this evolution progresses, the security needs of users are not diminishing. In fact, with easy access to more information on-line, the threats to the information integrity are likely to increase.

Attacks on paper-based systems generally require *physical access* to one of the few copies of a paper message. In contrast, an electronic system may store multiple copies of messages. A sender and recipient of a message generally does not know exactly which nodes of a network carried the message. Furthermore, there is a potential for undetectable, *remote access* to systems storing or transmitting electronic messages. Some basic threats to the information integrity in electronic communication systems are listed in Table 1.1.1 [Fum91].

A more elaborate presentation of the information integrity functions needed

| Signature         | Verify the identity of the originator. Written signatures are the primary form of identifying the originator. In early times wax seals were imprinted with the symbol of an important individual or office.                                                                                                                                                                           |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Integrity         | Ensure that the message or transaction received is the<br>same as that sent, without accidental or intentional<br>modification. Transactions are recorded in ink on non-<br>erasable documents. Special papers have been deve-<br>loped that display certain indicators if they are mo-<br>dified.                                                                                    |  |  |

| Non-repudiation   | Prove to a third party that the transaction actually<br>took place. This prevents an individual from denying<br>having engaged in a transaction. Procedures have<br>been established to verify individual signatures, keep<br>duplicate copies of transactions, and entrust third par-<br>ties to adjudicate disputes.                                                                |  |  |

| Privacy (secrecy) | Keep communications private. Physical protection<br>mechanisms have evolved to ensure the privacy of<br>transactions. The glue seal on an envelope and the<br>wax seal on a document are used to discourage others<br>from reading a message. Cryptography, the basis of<br>much of the security in electronic communication<br>systems, is a method almost as old as writing itself. |  |  |

Table 1.1: Information integrity functions in paper-based communication systems.

| Interception of data    | Network meadia can be tapped.                                                                                                                                         |  |  |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Modification of message | Modification of a message occurs when the con-<br>tents of a message is altered without detection<br>and results in unauthorised effects                              |  |  |

| Replay of message       | A replay occurs when a message, or a part of it,<br>is repeated to produce an unauthorised effect.                                                                    |  |  |

| Masquerading            | A masquerade is when an entity pretends to be<br>a different entity. This can be used to introduce<br>invalid messages that are delivered as if they<br>were genuine. |  |  |

| Repudiation             | This refers to a senders (or recipients) denial of participation in a transaction.                                                                                    |  |  |

Table 1.2: Some information integrity threats.

in electronic communication systems, and of the corresponding threats, can be found in text-books on cryptography, e.g. [Den82, Bra88, PGV91, Sim92b].

### 1.1.2 Cryptography

As mentioned above, a means for providing some of the important information integrity functions is cryptography. In general, there are two types of cryptography denoted secret key cryptography and public key cryptography. The crypto systems for performing secret key cryptography are also known as conventional crypto systems. Until 1976, when the concept of public key cryptography was introduced by Diffie and Hellman [DH76], all crypto systems were secret key systems. The following brief description of both types of crypto systems gives the reader an introduction to the advantages, and the disadvantages, of the public key crypto systems. The description is based on [Nec92].

#### Secret Key Cryptography

A secret key system consists of two transformations: An encryption transformation  $E_K$  used for encryption of a message M, and a decryption transformation  $D_K$  used for decryption of the encrypted message, i.e.  $D_K(E_K(M)) = M$ . The transformations are parameterised with a parameter K, denoted the key. By imposing certain requirements to the transformations, it is possible to withstand some of the information integrity threats in Table 1.1.1. Suppose two parties, say Alice and Bob, are communicating messages on a public communication channel. Furthermore, suppose that a third party, say Charlie, has access to the communication channel:

- To prevent Charlie from intercepting a message M send from Alice to Bob, Alice encrypts M using  $E_K$ . Then, the resulting so-called ciphertext  $C = E_k(M)$  is sent to Bob. Finally, Bob decrypts C using  $D_K$ . The key K, used as parameter in the encryption and the decryption, is kept secret from Charlie. Hence, by requiring that it is infeasible for Charlie to compute  $D_K(C)$  without knowledge of the key value, Alice and Bob have achieved privacy in their communication.

- Furthermore, if it is infeasible for Charlie to compute  $E_K(M)$  without knowledge of the key value, Charlie cannot pretend to be Alice in a communication where M is send to Bob.

The secret key crypto systems are mainly used for providing privacy in a communication between two parties. The *Data Encryption Standard* (DES) system is the most widely used secret key crypto system, see e.g. [SB92].

#### Public Key Cryptography

One of the reasons [Dif92] for proposing public key cryptography was the problem of key distribution: If two people, who have never met before, are to communicate privately using secret key cryptography, they must somehow agree in advance on a key that will be known to themselves and to no one else. Another reason was the problems of signatures and of non-repudiation: A method was needed for providing the recipient of a purely digital electronic message with a way of demonstrating to other people, that the message had come from a particular person. Hence, the signature should allow the recipient to hold the author to the contents of the message.

Public key systems differ from secret key systems in that there is no longer a single secret key shared by a pair of users. Rather, each user has each own key material. Furthermore, the key material of each user is divided into two portions, a private component and a public component. The public component generates a public transformation E, and the private component generates a private transformation D. Often, E and D is denoted the encryption transformation and the decryption transformation, respectively. This is, however, an imprecise terminology: Depending on the actual system, it may be the case that D(E(M)) = M, E(D(M)) = M, or both. A common requirement to the public transformation E is that it must be a so-called trapdoor one-way function. "One-way" refers to the fact that Eshould be easy to compute from the public component of the key but hard to invert unless one possesses the corresponding private transformation D, or equivalently, the private component of the key. The private component thus yields a "trapdoor" which makes the problem of inverting E seem difficult from the point of view of all but the possessor of D.

The following examples show how privacy, signatures, and non-repudiation may be provided by a public key crypto system. The transformations  $D_A$ and  $E_A$  are those generated by Alice's key, and the transformations  $D_B$  and  $E_B$  are those generated by Bob's key:

- To prevent Charlie from intercepting a message M send from Alice to Bob, Alice encrypts the message by means of Bob's public available transformation  $E_B$ . Then, the ciphertext  $C = E_B(M)$  is sent to Bob, who decrypts C by means of his own private transformation,  $M = D_B(C)1$ . So, when the public key crypto system is used for obtaining privacy, only the transformations of the recipient are used. The requirement to the transformations is that  $D_B(E_B(M)) = M$ . It should be emphasised, that Bob never needs to share  $D_B$  with Alice.

- To convince Bob that the message M indeed originates from Alice and, hence, cannot have been generated by Charlie, Alice is able to sign the message: Alice transforms the message by means of her own private transformation. Then, the resulting signed message  $S = D_A(M)$  is sent to Bob. Finally, in order to verify the signature, Bob applies Alice's

#### 1.1. THE NEED FOR CRYPYOGRAPHY

public transformation to obtain  $M = E_A(S)$ . Since  $D_A$  is strictly private to Alice, Charlie could not possibly have generated the signed message. Note that only the transformations of Alice's are used. In order to provide signatures, the transformations must obey  $E_A(D_A(M)) = M$ .

• The signed message,  $S = D_A(M)$ , could not even have been generated by Bob. Furthermore, the signature can be verified by every person who has access to Alice's public transformation. Hence, Bob can prove to a third party that Alice indeed was the author of the signed message, and Alice cannot deny having signed the message.

To provide privacy, the transformations used in a public key systems must obey the condition D(E(M)) = M, and to provide signatures they must obey E(D(M)) = M. According to [Nec92] there is only one major system, the *Rivest-Shamir-Adleman* (RSA) system, that satisfies both conditions. This system will be introduced below.

Compared to the secret key systems, the public key systems provide a wider range of information integrity functions. Furthermore, the key distribution problem is significantly reduced: There is no longer a need for exchanging secret keys. Apart from the private transformation of a user, only the public available transformations of the other users are required in order to apply public key cryptography.

There are, however, a disadvantage of the public key systems: Compared to the secret key systems, they are based on very slow transformations, i.e. the obtainable bandwidths associated with public key cryptography are limited. A state-of-the-art dedicated hardware implementations of the DES secret key system is able to perform the transformations at a rate of up to 90 Mbit/set [Pij91]. This is close to 1000 times faster than the fastest known implementations of the RSA public key system. Indeed, the bandwidth problem represents the most serious limitation on the practical applicability of public key systems.

#### 1.1.3 The RSA Public Key Crypto System

The RSA public key crypto system is the best known public key crypto system. Many authors regard the system as the most versatile system that have been proposed. The system is invented by Rivest, Shamir and Adleman [RSA78]. It was published for the first time in 1977 [Gar77].

Both the public transformation E and the private transformation D are performed by a so-called modular exponentiation. The transformations have a common modulus m. They only differ in the value of the exponent. The pair (e, m), where e is the public exponent, constitutes the public component of a user's key. Similarly, the pair (d, m), where d is the private exponent, constitutes the private component,

$$E(M) = M^e \mod m$$

$$D(M) = M^d \mod m, \text{ where } M \in [0; m[ \qquad (1.1)$$

In order to obey D(E(M)) = E(D(M)) = M, and simultaneously to achieve that E has the properties of a trapdoor one-way function, the values of m, e and d must be selected with care. A brief introduction of how to generate the keys is given below.

In a typical application of RSA cryptography, the digital representation of the message M will be much greater than the modulus m. In this case the message is divided into a number of blocks,  $M = M_1 M_2 \ldots$ , where each block is less than m. Then, each block is separately transformed using E or D. Hence, a typical application consists of a (long) series of transformations, where the modulus and exponent is fixed.

#### Generating Keys

The following is a brief description of the basic requirements to a user's public key (e, m) and private key (d, m). For a more detailed treatment of the key generation topic, the reader is referred to e.g. [BO92, Moo92]. The keys are generated through the following steps:

- 1. Two large prime numbers p and q are chosen. Then, the modulus is computed as the product of the primes, i.e. m = pq. The so-called Euler totient function of m (see e.g. [Den82, p. 41],) is computed as well,  $\varphi(m) = \varphi(p)\varphi(q) = (p-1)(q-1)$ .

- 2. Choose an integer exponent, say e, such that  $e \in [1; \varphi(m)[$  and  $gcd(e, \varphi(m)) = 1$ . The last condition ensures the existence of a multiplicative inverse of e modulo  $\varphi(m)$ . Then, let the other exponent d be a multiplicative inverse, i.e. an integer d satisfying  $ed \mod \varphi(m) = 1$ .

#### 1.1. THE NEED FOR CRYPYOGRAPHY

When the modulus m and the exponents e and d are chosen in accordance to these rules, the following equation holds for all  $M \in [0; m]$ ,

$$D(E(M)) = E(D(M)) = M$$

(1.2)

A proof of (1.2) is included in the original article [RSA78] by Rivest, Shamir and Adleman. It should be mentioned, that several descriptions of the RSA system contain an *inadequate* proof of Equation (1.2). Even though the complete proof is pretty short, it is beyond the scope of this introductory description. So, the interested reader is referred to [RSA78].

#### Security of RSA

The public transformation  $E(M) = M^e \mod m$  is a one-way function since it is relatively easy to compute E(M) and relatively hard to invert the transformation without the knowledge of the private exponent d. Moreover, because it is relatively easy to invert E using the private transformation D, E is a trapdoor function.

Using a very rough measure of computing time, it takes about  $n = \log_2 m$ primitive operations to perform a modular exponentiation assuming all of the operands are of the same bit length n. The unit "primitive operations" is a very imprecise measure. However, the measure is satisfactory for the purpose of this introduction: To give a feeling of the computationally effort required to perform the transformations E and D, and to invert E without knowing D. Hence, the time for computing E, or D, is about n operations. The fastest known methods for inverting E without knowing d require a factorisation of m, i.e. a computation of the prime factors p and q of m. The problem of prime factorisation is believed to be a hard problem in the sense, that it is very resource demanding: One of the fastest methods, denoted the quadratic sieve, requires in the order of  $\exp(\sqrt{n \cdot \log n})$  primitive operations to factorise an n-digit number [Nec92].

In order to obtain a sufficient degree of security of the RSA crypto system, the length of the keys must be chosen such that it becomes infeasible to factorise the modulus. Until recently, it was believed that a key length of 512 bits was adequate. However, there have been a substantial progress in the development of methods for prime factorisation: In 1977 it was estimated that several billions of years was required to factorise a number of 129 decimal digits [Gar77]. Indeed, the inventors of the RSA system challenged the public by offering a \$100 prize to the first successful decoder of an encrypted message. The message was encrypted using a modulus of 129 decimal digits, or in a binary representation, 426 bits. In April 1994 the message was finally decoded in a factorisation project running over 8 months [AGLL94]. The computations was distributed to about 600 sites by means of the Internet, and a total of about 1600 machines were used. A 512 bit modulus has not yet been factorised. The authors of [AGLL94] estimate that such a project probably would require at least 100 times the computing power available in the factorisation of the 426 bit modulus. Similar projects are described in [LM89, DDLM93]. Today, a key length of 700-1000 bits is believed to sufficiently safe.

#### 1.1.4 Other Public Key Crypto Systems

Several public key crypto systems have been proposed since public key cryptography was invented in 1976. Several of these systems have been broken, as well. It is remarkable that virtually all systems, that have not been broken, employ transformations based on exponentiation [Dif92, p. 166]. In general, the "one-way" property of transformations based on exponentiation is due to either the prime factorisation problem or to the discrete logarithm problem:

The prime factorisation problem refers to the problem of finding the prime factors of a modulus m = pq. As discussed above, a factorisation of m can be used for inverting the public transformations of the form,

$$E(M) = M^e \mod m.$$

The discrete logarithm problem refers to the problem of inverting a public transformation of the form,

$$E(M) = a^M \mod p.$$

Here, both the prime number p and the base a are part of the public key. If the result of applying E to M is denoted C, then the discrete logarithm to the base a of C modulus p reveals the message,  $M = \log_a C \mod p$ .

The fastest methods for computing discrete logarithms, using n digit operands, have resource requirements of the same order as the requirements for factoring n digit moduli. Hence, the keys used in any of the transformations based

on exponentiation is expected to be of about the same length. However, compared to the RSA system, some public key systems based on the discrete logarithm problem require longer operands to achieve the same degree of security [vO92].

#### 1.1.5 Hardware Support

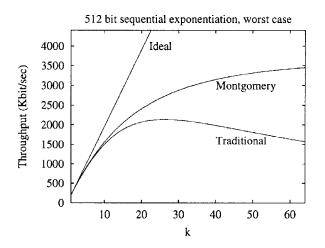

Shortly after the invention of the RSA public key crypto system in 1977, researchers began to develop dedicated hardware to support applications of RSA cryptography with more computing power. The very first hardware implementations of modular exponentiation were boards of discrete components. These were shortly after followed by special purpose VLSI (Very Large Scale Integrated) circuits. In 1980 Rivest, Shamir and Adleman developed a single-chip implementation for modular exponentiation of 512 bit operands [Riv80]. The chip should have been capable of encrypting at a rate of about 1.2 Kbit/sec. However, the chip never gotten to work correctly [Riv82, Riv84]. In 1981 a 336 bit chip was developed at Sandia National Laboratories, California. By combining two of these chips an encryption rate of 420 bit/set using 336 bit keys was achieved [Riv84]. In 1990, when the work presented in this thesis was initiated, the fastest known implementation had an encryption rate of 29 Kbit/sec using 512 bit keys. Today, in 1995, hardware implementations of the modular exponentiation operation have increased the available encryption rate to more than 100 Kbit/sec for key lengths of more than 512 bit. One of the implementations is a product of the work presented in this thesis. Furthermore, the development of new methods and the development of faster technologies implies that encryption rates of several Mbit/set soon will be achievable.

The voluminous literature on implementation of fast RSA cryptography witnesses the great interest of finding a solution to the bandwidth problem. Since 1980 more than twenty hardware implementations supporting RSA cryptography have been made<sup>1</sup>, and several methods and architectures suited for hardware implementation have been proposed.<sup>2</sup> Some of the im-

<sup>&</sup>lt;sup>1</sup>[Riv80, ST83, Koc85, Bar86, GD88, HDVG88, Tho88, Bri89, ICHO89, DK90, VVDJ90, SVB91, Dif92, IWSD92, Lin, Pij92, SV93, Sch93, Oru94]

<sup>&</sup>lt;sup>2</sup>[NS81, WC81, Bri82, Miy82, QC82, Bla83, Slo85, MA85, Mon85, ORS<sup>+</sup>86, SG86, Bak87, Sed87, KH88, Gib88, LHLH88, ZMY88, BG89, JM89, MP89, Mor89, KH90a, KH90b, Eve90, FDG90, OSA90a, WE90, Eld91, KH91, OK91, Wal91a, Wal91b, Tak92,

plementations are aimed for Smart Cards, where the available amount of circuitry is quit limited [Kno88, Mor89, dWQ90]. Methods, and hardware support, for other public key crypto systems have been developed as well [ORS<sup>+</sup>86, GG90, AMOV91, ABMV93]. A description of the first years of hardware development for public key cryptography is included in [Dif92], and partial lists of existing RSA chips can be found in [Bri89, BFS91, Sch93].

## 1.2 Purpose of the Thesis

In 1990, when the work presented in this thesis was initiated, the following specific subgoal was set up:

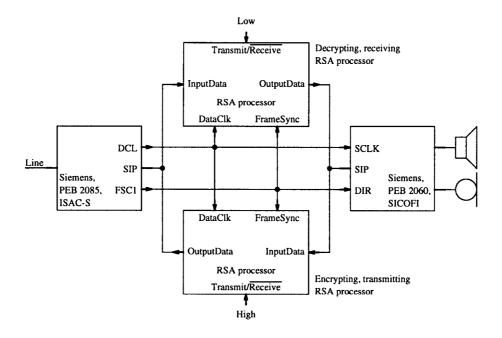

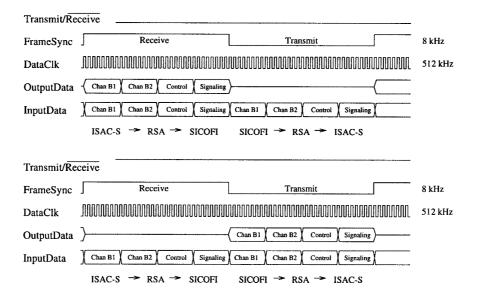

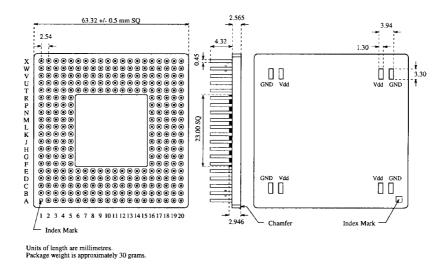

A VLSI implementation capable of performing modular exponentiation should be realised. The implementation should be able to compute the transformations used in RSA cryptography at a rate of at least 64 Kbit/sec. Hereby, it should be possible to apply real-time RSA cryptography to the data transmitted on an ISDN channel. To obtain a satisfactory degree of security, the length of the keys was specified to 561 bit. Furthermore, to enable the implementation to be embedded in telecommunication equipment, it should be implemented as a single VLSI chip. Finally, in order to demonstrate the capabilities of the chip, it should support a special interface used internally in some ISDN telephones.

Apart from describing the various decisions taken during the process of realising the VLSI chip, the purpose of this thesis is to provide the reader with an insight into the methods for performing modular exponentiation of operands of several hundreds of bits.

## 1.3 Chosen Approach

In the work presented in this thesis the strategy for achieving faster transformation rates for the RSA system is to develop *comptation methods*, that are more "efficient" than other known methods. The fastest implementation of RSA cryptography is achieved by constructing *dedicated hardware circuits*.

TY92, IMI92a, IMI92b, Sau92, EW93, Kor93b, OPT93, Wal93, Zha93, Kor94b, Oru95]

In contrast to methods aimed for standard micro-processors, the methods of this thesis are not constrained by a standard architecture. Indeed, the additional freedom of specifying special-purpose hardware architectures is utilised to obtain optimal solutions where the hardware architecture are developed in harmony with the computation method.

In general, the means for obtaining a fast hardware implementation can be divided into two independent contributions:

The technology used for the implementation has a major influence on the obtainable performance for a given computation method and architecture. One of the reasons that the hardware implementations are becoming increasingly faster, compared to the initial initiatives in 1980, is the improvement of the CMOS technology.

The effect of using a faster technology is often seen as increasing clocking frequencies of VLSI chips. A good illustration of this effect is reported in the article [IWSD92]: Ivey et al. have implemented the same architecture and computation method in two different technologies. In a bulk CMOS process they obtain a clocking frequency of 100 MHz, and in a Silicon On Insulator (SOI) CMOS process they obtain a frequency of 150 MHz. In [MP89] it is considered to use a Gallium Arsenide (GaAs) process.

The computation method and the architecture do, of course, influence the obtainable speed of an implementation. In the article reprinted in Appendix A it is observed that all of the fastest implementations known in 1990 use about the same number of clock cycles for performing a modular exponentiation. Hence, the underlying computation methods are characterised by requiring the same number of cycles, and the difference in computation speed can be attributed to the varying clocking frequencies. So, it is tempting to claim that, until 1990, the difference in the computation speed is mainly due to the difference in technology and to the skills of the VLSI circuit designers—it is not due to varying "efficiencies" of the computation methods. This basic observation is the reason for the approach chosen in this thesis: Through the development of efficient computation methods and architectures, the speed of hardware implementations for performing modular exponentiation is increased independently of the technology chosen. Of course, a combination of "efficient" methods and fast technologies leads to even better

|                         | Clock               | Throughput    | Cycles          | Reference      |

|-------------------------|---------------------|---------------|-----------------|----------------|

| Years 1980-1990:        |                     |               |                 |                |

| Cryptech                | $14 \mathrm{~MHz}$  | 17  Kbit/sec  | $42 \cdot 10^5$ | [Bri89, Sch93] |

| AT&T                    | $15 \mathrm{~MHz}$  | 19 Kbit/sec   | $40\cdot 10^5$  | [Bri89, Sch93] |

| Thorn EM1 board         | $24 \mathrm{~MHz}$  | 29  Kbit/sec  | $42 \cdot 10^5$ | [Tho88]        |

| Years 1990-1995:        |                     |               |                 |                |

| Calmos Syst. Inc.       | $20 \mathrm{~MHz}$  | 28  Kbit/sec  | $37\cdot 10^5$  | [Sch93]        |

| Cryptech PQR512         | $25 \mathrm{~MHz}$  | 32  Kbit/sec  | $40\cdot 10^5$  | [Lin]          |

| Pijnenburg PCC200       | $25 \mathrm{~MHz}$  | 40  Kbit/sec  | $32\cdot 10^5$  | [Pij92]        |

| University of Sheffield | $150 \mathrm{~MHz}$ | 92  Kbit/sec  | $83\cdot 10^5$  | [IWSD92]       |

| VICTOR                  | $25 \mathrm{~MHz}$  | 111  Kbit/sec | $12\cdot 10^5$  | [Oru94]        |

| Utilisation of CRT:     |                     |               |                 |                |

| Thorn EMI board         | $24 \mathrm{~MHz}$  | 56  Kbit/sec  | $22\cdot 10^5$  | [Tho88]        |

| DEC Perle-0 board       | $26 \mathrm{~MHz}$  | 200  Kbit/sec | $6.7\cdot 10^5$ | [SVB91, BRV93] |

| DEC Perle-1 board       | $40 \mathrm{~MHz}$  | 300  Kbit/sec | $6.8\cdot 10^5$ | [SV93, BRV93]  |

| Without CRT:            |                     |               |                 |                |

| DEC Perle-0 board       | $26 \mathrm{~MHz}$  | 50  Kbit/sec  | $27\cdot 10^5$  | [SVB91, BRV93] |

| DEC Perle-1 board       | $40 \mathrm{~MHz}$  | 75  Kbit/sec  | $27 \cdot 10^5$ | [SV93, BRV93]  |

Table 1.3: Existing hardware implementations performing 512 bit exponentiation.

#### performance.

The article of Appendix A defines an "efficiency" measure of the underlying computation methods. The measure is basically a measure of the number of clock cycles required for a modular exponentiation: A high number of cycles implies a low efficiency, and vice versa. All of the fastest hardware implementations known in 1990 had the same efficiency. It should be emphasised, that none of the slower performing implementations known in 1990 had higher efficiencies. So, in some sense, all of the fast performing implementations in 1990 used a state-of-the-art method.

In the meanwhile, since 1990 when the article of Appendix A was written, more hardware implementations have been made. Table 1.3 lists the fastest implementations known by the author.<sup>3</sup> The clocking frequency, the throughput (i.e. the computation rate) for a modular exponentiation using 512 bit operands, and the number of clock cycles required for an exponentiation are shown in the table. Some uncertainty in the performance of the implementations should be expected: Often the obtainable throughput depends on the actual data values. For the most common method of exponentiation, the worst case computation requires twice the number of cycles of the best case computation. For some of the implementations it is not known whether the performance refers to the best case, the average case, or the worst case. The first section of Table 1.3 lists the fastest implementations known in 1990. The second section lists the implementations that have appeared since 1990. The third, and fourth, section lists implementations that utilise the Chinese Remainder Theorem (CRT) to reduce the computational effort required to perform the private transformation of the RSA system. As described in Section 2.4 this can reduce the computing time by a factor close to four. Since the computing time for performing a general 512 bit modular exponentiation, where the CRT cannot be used, is not known for the DEC implementations, the fourth section of the table shows the expected performance when the effect of the CRT is removed.

As seen by Table 1.3, the Thorn EMI board does not fully utilise the potential of the Chinese Remainder Theorem: The number of cycles is decreased by less than a factor of two. Removing the effect of the CRT, it is seen that only four of the implementations made after 1990 have significant changes in the "efficiency" of the computation method: The Sheffield chip, the DEC boards, and the chip denoted VICTOR. The implementation of the latter chip is part of the work presented in this thesis.

• The Sheffield chip represents an approach where the "efficiency" of the

<sup>&</sup>lt;sup>3</sup>In the article [SV93] the performance for the DEC Perle-1 implementation is specified as 600 Kbit/sec. Therefore, many authors have been lead to the belief, that the DEC Perle-1 implementation is capable of performing a single 512 bit modular exponentiation in 0.85 msec. This is, however, not the case: According to a personal communication on July 4 1995 with Mark Shand, one of the authors of [SV93], the specified throughput of 600 Kbit/sec is an estimate of the total performance of two independent modular exponentiation units, each performing a 512 bit exponentiation. Therefore, a throughput of 300 Kbit/sec must be expected for a single exponentiation unit.

The throughput of 600 Kbit/sec have never been measured for the DEC Perle-1 implementation. However, a throughput of 185 Kbit/sec have been measured for a single unit performing modular exponentiations using 970 bit operands.

computation method has *decreased* in comparison to the implementations made prior to 1990. On the other hand, the clocking frequency is significantly higher than the rest of the implementations listed in Table 1.3. This illustrates the fact, that the "efficiency" measure is a bad stand-alone measure of the performance potential of a computation method: Even though a fast technology is used for implementing the Sheffield chip, the high clocking frequency is partly due to a short socalled *critical path* of the circuitry, i.e. the longest delay of the circuitry activated in a clock cycle.

- The VICTOR chip, and the DEC Perle-0 board, represents an approach where the increased performance is obtained by an increased "efficiency" of the computation method. Even though the technology used to implement the VICTOR chip is expected to be faster than the technologies used prior to 1990, the clocking frequency has not increased significantly. This indicates that the cost of using a more "efficient" computation method is a relatively longer critical path.

- The varying performance of the two DEC boards is not due to a difference in the "efficiency". The variation is expressed by a difference in clocking frequency. However, it is not solely due to the variation of the technology used for the implementation: In the Perle-1 implementation another computation method with the same "efficiency" as the Perle-0 and a shorter critical path has been used.

Hence, to obtain a high performance of a computation method, and the associated hard-ware architecture, both the required number of cycles and the critical path of the circuitry must be considered. For a further discussion on how to measure the performance, and on how to separate the contributions from technology and method, the reader is referred to e.g. [PH94, Chapter 2]. In the following chapters of the thesis, the term "efficiency" will not refer to a specific well-defined measure of performance.

### 1.4 Organisation of the Thesis

The thesis consists of two parts: The first part comprises six chapters, and the second part comprises five appendices. Each appendix contains a paper that has been written during the period from 1990 to 1995. The overall aim of the first part is to provide the reader with an insight into the research on computation methods for performing modular exponentiation. Furthermore, the aim is to report the work done by the author. Through a discussion of the existing literature on the research topic, the contributions represented by the papers in the appendices is set into a consistent frame. The chapters of the first part are on various topics. They can be read independently of each other. Each chapter ends with a summary and a discussion of the topic. It is assumed that the reader is familiar with the basic methods of computer science. The papers in the appendices assume some knowledge of the methods and techniques known from the fields of computer arithmetic and VLSI design.

The first four chapters are structured as a hierarchal presentation where the problems identified at one level are solved by introducing a new set of problems at a lower level. The lowest level in the hierarchy is the hardware level, where the solutions are realised as a hardware architecture capable of executing a specific computation. The fifth chapter describes a particular efficient computation method. The method can be viewed as the result of combining the experiences gained from the preceeding chapters:

- Chapter 1 gives a brief motivation to the subject of this thesis by considering applications of cryptography. The principles of public key cryptography are briefly introduced with an emphasis on the RSA crypto system. The problem of achieving sufficiently fast computation of modular exponentials is identified.

- **Chapter 2** is a relatively exhaustive description of methods for computation of exponentials. Since an exponentiation is performed by a series of multiplications the focus is directed toward methods using as few multiplications as possible and toward methods that can utilise a parallel computation scheme. An effort has been put into identifying various properties of the multiplication operation and explaining how these properties can be utilised to achieve efficient methods for computation of exponentials.

- Chapter 3 treats modular multiplication—the arithmetical operation used in modular exponentiation. As the previous chapter, this chapter contains a relatively exhaustive description of the methods and techniques used for computing modular products. The important concept of "representation" is introduced, and it is described how the properties of the

chosen representation can be utilised to achieve efficient methods for addition, subtraction, multiplication and division. These are the fundamental operations used in modular multiplication. The problem of determining quotient digits is treated in detail. It turns out that this is one of the major problems in the approach of high-radix modular multiplication described by the papers in the appendices.

- Chapter 4 is a description of a project of implementing a VLSI processor for computing modular exponentials. The style of the chapter is more descriptive than discussing. The chapter includes a description of the history of the project, the hardware architecture and the computation methods, and the results of the tests and performance measurements.

- Chapter 5 describes an efficient solution of the problem of determining quotient digits. The solution represents a break-through in the high-radix approach followed by the author. The chapter describes how the performance of future hardware implementations of modular exponentiation can be increased by more than an order of magnitude compared to the fastest implementations known today.

- Chapter 6 contains a brief conclusion on the work presented in this thesis.

### **1.5** Description of Papers

As previously mentioned the second part of the thesis consists of five papers written during the period from 1990 to 1995 In the Appendices A through E the original papers are printed in the original typesetting. Except from the paper in Appendix E, all of the papers are research articles. The paper in Appendix E is a document providing some of the essential data on the VLSI processor described in Chapter 4. The following listing of the papers provides information on co-authorship, publication status etc.,

Holger Orup, Erik Svendsen, and Erik Andreasen, "VICTOR, an Efficient RSA Hardware Implementation", in Ivan B. Damgård, editor, Advances in Cryptology – EUROCRYPT '90. Proceedings, volume 473 of Lecture Notes in Computer Science, pages 245–252, Aarhus, Denmark, May 21–24 1990. Springer-Verlag, Berlin, 1991.

#### 1.5. DESCRIPTION OF PAPERS

This article includes a short motivation for focussing on more efficient computation methods. The basic idea of using high-radix modular multiplication is introduced. However, the term "multiple bit scan" is used in place of "high-radix". It is noteworthy that the estimated speed of a suggested VLSI implementation is quit close to the speed of the fabricated VLSI processor described in Chapter 4.

Holger Orup and Peter Kornerup, "A High-Radix Hardware Algorithm for Calculating the Exponential M<sup>E</sup> Modulo N", in Peter Kornerup and David W. Matula, editors, Proceedings. 10th IEEE Symposium on Computer Arithmetic, pages 51–56, Grenoble, France, June 26–28 1991. IEEE Computer Society Press, Los Alamitos, California, 1991.

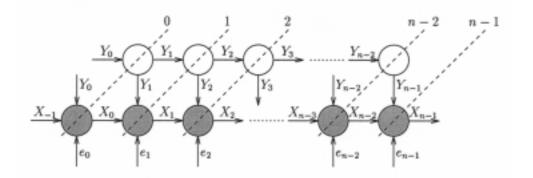

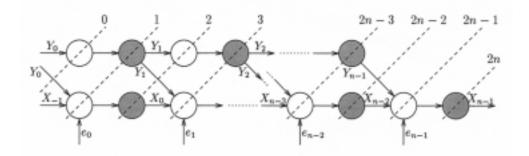

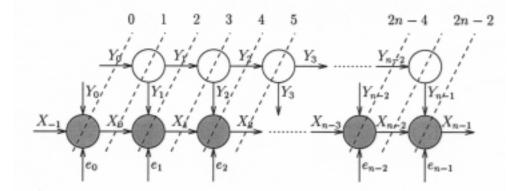

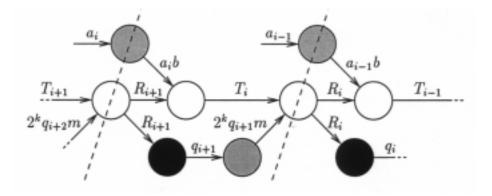

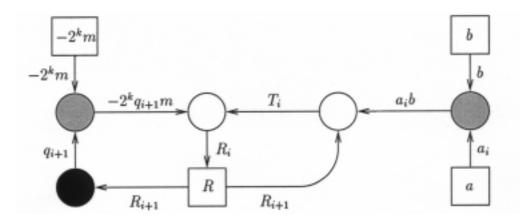

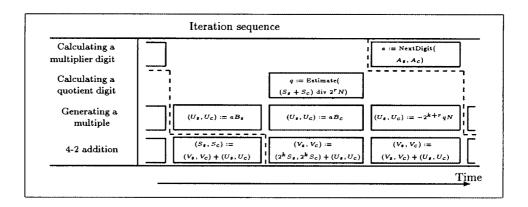

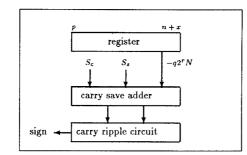

In this article the terminology known from the field of computer arithmetic is used. The article suggests an extended use redundant representations. Furthermore, a computation schedule based on pipelining is proposed.

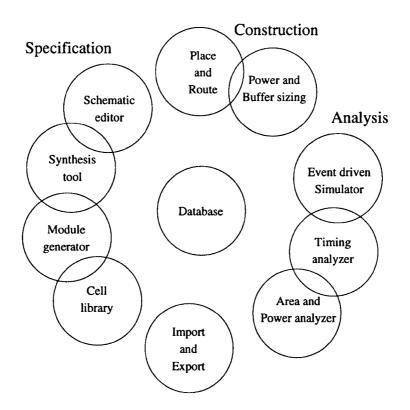

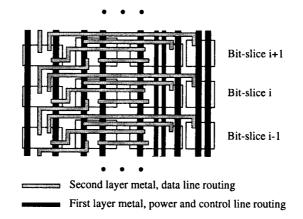

Holger Orup, "Area Reduction for Bit-Sliced Layouts using a Commercial Development System", Unpublished article, Department of Computer Science, University of Aarhus, 1994.

This article describes the experiences obtained from the work of reducing the area of the VLSI processor. The various techniques for reducing the area, and the effect of applying them, are described.

Holger Orup, "Simplifying Quotient Determination in High-Radix Modular Multiplication", in Simon Knowles and William H. McAllister, editors, *Proceedings. 12th IEEE Symposium on Computer Arithmetic*, pages 193–199, Bath, England, July 19–21 1995. IEEE Computer Society Press, Los Alamitos, California, 1995.

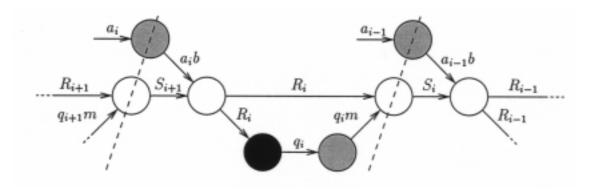

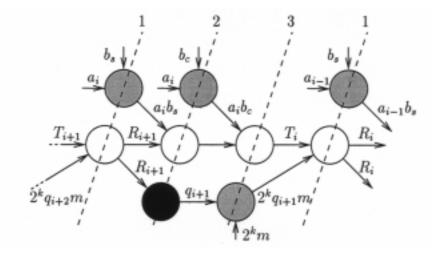

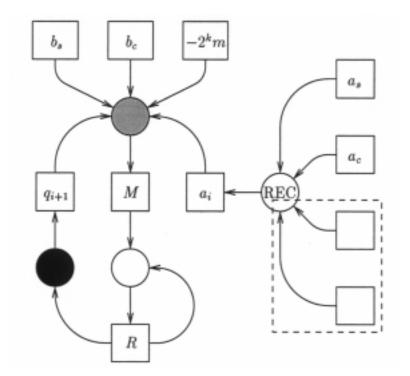

This article describes how a combination of optimisation techniques leads to a very simple quotient determination in high-radix modular multiplication. Furthermore, a pipelining technique is utilised to obtain a very short critical path in the hardware architecture.

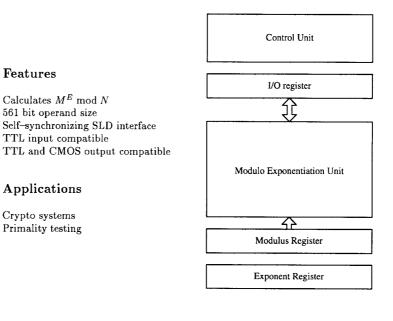

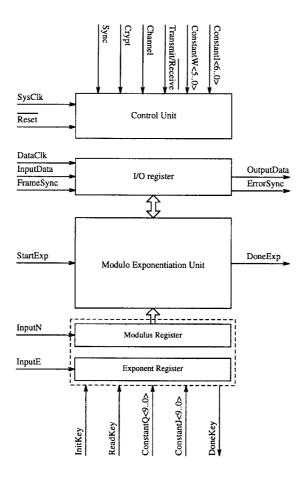

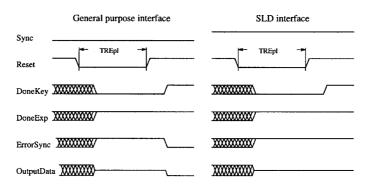

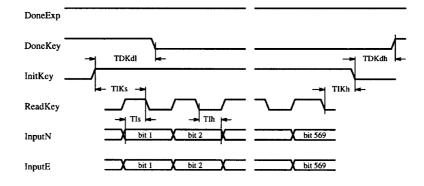

Holger Orup, "RSA Processor, Preliminary Engineering Data", Internal document, Department of Computer Science, University of Aarhus, 1993. This is a document that provides some of the essential data of the VLSI processor. It should be emphasised, that the document *in no means* pretends to be a satisfactory complete product description. It is a document providing preliminary descriptions of a prototype. The document is included in order to provide an impression of the functionality of the VLSI processor.

## Chapter 2

## Exponentiation

Exponentiation refers to the process of evaluating exponentials or powers  $b^e$ , where b is the base and e is the exponent. The eth power of b is defined recursively by

$$b^{0} = 1_{G}$$

$$b^{e} = b^{e-1} *_{G} b, \ e \in \{1, 2, 3, \dots\},$$

(2.1)

where b is element in a set G with a mutiplication composition  $*_G : G \times G \mapsto G$  and  $1_G \in G$  is a neutral element for multiplication. An example is the set  $\mathbb{Z}_n = \{0, 1, \ldots, n-1\}$  with the multiplication composition modular multiplication  $(x \cdot y) \mod n$  and the neutral element 1. In this case, Equation 2.1 defines modular exponentials as in the RSA crypto system. The RSA crypto system is described in Subsection 1.1.3. Taking into consideration, that this thesis primarily is directed toward efficient methods for computing modular exponentials, the definition seems very general. But, since the methods of this chapter only uses a few properties of modular multiplication, the methods apply to all sets, where a multiplication composition is defined. Other sets, that are used in crypto systems, are the Galois Fields  $GF(2^n)$ , where the elements are polynomials and the multiplication composition is defined as polynomial multiplication modulo an irreducible polynomial [Den82, p. 48].

A common characteristic for the computation of exponentials in crypto systems is the very large exponents. E.g., at present, exponent values in the range from  $2^{512}$  to  $2^{1024}$  are considered to be necessary to achieve a sufficient degree of security for the RSA system. In the future, even larger exponent values may be necessary.

A straight forward method for exponentiation is derived from Equation 2.1. It will be called the *unary method*,

$$b^{0} = b^{e-1} * b$$

$$= (\cdots ((1 * b) * b) \cdots) * b.$$

(2.2)

To simplify the notation the subscripts of the multiplication composition and the neutral element are made implicit. The unary method needs e multiplications and two registers: One register for b and one for intermediate results. Since (1 \* b) equals b the very first multiplication can be avoided, resulting in e - 1 multiplications when e > 0.

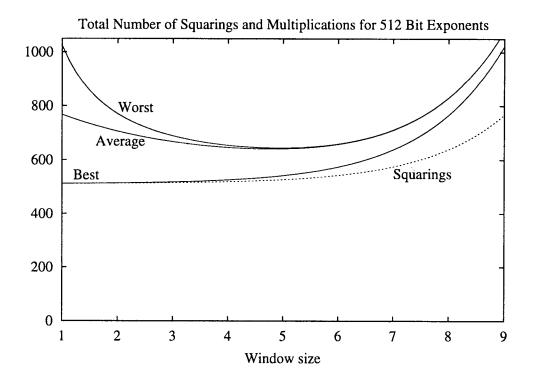

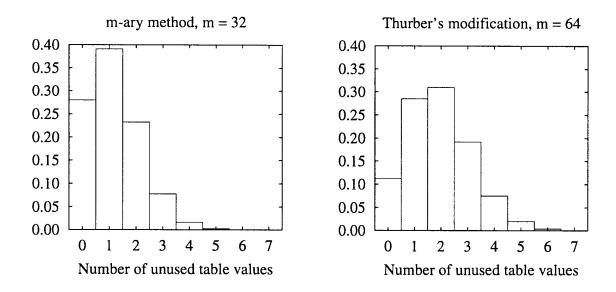

In the following, exponentiation methods will be discussed and compared in terms of the resource requirements: Computing time and memory requirements. The computing time is expressed as the necessary number of multiplications. It is assumed that the time for other operations such as additions and comparisons are negligible. In certain algebraic systems there may be a substantial difference in the computing time for a general multiplication and a squaring. E.g. Agnew et al. [AMV88] utilise that squaring can be performed much faster than multiplication in  $GF(2^n)$ . Consequently, whenever feasible, the total computing time will be split into a number of multiplications and a number of squarings. The memory requirements will be expressed as the number of registers needed, where a register is assumed to contain a single element from the set G over which exponentiation is performed. This is a rough measure since the binary encoding of two elements may require very different amounts of space in terms of bits. Indeed, this happens if exponentiation is performed by integer multiplication over  $\mathbb{N}$ , the non-negative integers. However, this rough measure is useful in the present context, since in most crypto systems the set of elements is finite and a modulo reduction is part of the multiplication. Memory for the exponent and for constants, such as the neutral element 1, will be implicit in the discussions of memory consumption. Furthermore, the required number of processing elements will be part of the resource requirements when parallel methods are described.

This chapter is divided into five sections. Section 2.1 describes different sequential computation methods. It is shown that if the multiplication composition is associative the computing time can be reduced to a logarithmic number of multiplications. Moreover, it is utilised that by precomputing of-

## 2.1. FEWER MULTIPLICATIONS

ten used values and by saving these in a table the computing time can be further reduced. Section 2.2 gives some theoretical lower bounds on the number of multiplications. This is used to access how well the different sequential computation methods perform. In Section 2.3 parallel computation methods are described. It turns out that a pipelined method is superior to the fastest sequential methods, both with respect to computing time and to hardware consumption. Section 2.4 describes how the algebraic properties of modular multiplication can be utilised to speed up the computation of modular exponentials in the RSA crypto system. Finally, Section 2.5 contains a summary and a discussion.

## 2.1 Fewer Multiplications

Compared to the unary method the number of multiplications can be dramatically reduced if the multiplication composition is associative, i.e. (a\*b)\*c = a\*(b\*c). This property implies that  $b^{2e} = b^e * b^e = (b^e)^2$ . Hence, if the exponent is even the number of multiplications can be reduced to nearly half. Furthermore, if the exponent is odd the rule  $b^{2e+1} = (b^e)^2 * b$  also reduces the computationally effort. These rules can be used recursively and the result is a logarithmic number of multiplications. This is the well known binary method described by Knuth [Knu81, p. 441]. According to Knuth the binary method was described as early as 200 B.C.. If the exponent is binary encoded as a string of n bits,  $e_{n-1}e_{n-2}\dots e_0$ , the value of e can be expressed as

$$e = \sum_{i=0}^{n-1} e_i 2^i, \ e_i \in \{0,1\}, e_{n-1} > 0$$

$$= ((\cdots ((e_{n-1})2 + e_{n-2})2 + \cdots )2 + e_1)2 + e_0,$$

(2.3)

using Horner's rule. Because of the constraint  $e_{n-1} > 0$  the trivial case, where e = 0, is disregarded. This constraint ensures that the string of binary digits does not contain any leading zeroes and, hence, that n - 1 equals  $[\log_2 e]$ . The *e*th power of *b* can now be written as

$$b^{e} = b^{((\cdots((e_{n-1})^{2}+e_{n-2})^{2}+\cdots)^{2}+e_{1})^{2}+e_{0}}$$

$$= ((\cdots((b^{e_{n-1}})^{2}*b^{e_{n-2}})^{2}*\cdots)^{2}*b^{e_{1}})^{2}*b^{e_{0}}.$$

(2.4)

This shows that exponentiation can be performed with n-1 squarings and n-1 multiplications. The memory requirement is one register for b and

another for the intermediate results. Since n-1 equals  $\lfloor \log_2 e \rfloor$  the method is logarithmic.

If bit  $e_i$  is 0 the multiplication by  $b^{e_i}$  reduces to a multiplication by 1 and can be neglected. Usually the number of bits, that are non-zero in the binary encoding of e, is denoted  $\nu(e), \nu(e) = \sum_i e_i \in \{1, 2, \dots, \lfloor \log_2 e \rfloor + 1\}$ . This function is called the *Hamming weight* of e. The number of squarings and multiplications can then be expressed by respectively  $\lfloor \log_2 e \rfloor$  and  $\nu(e) -$ 1. Since the method scans the exponent from most significant bit to least significant bit it is denoted the *left-to-right* binary method.

It is also possible to scan the exponent from right to left. Still using a binary encoding of e, the eth power of b can be written as

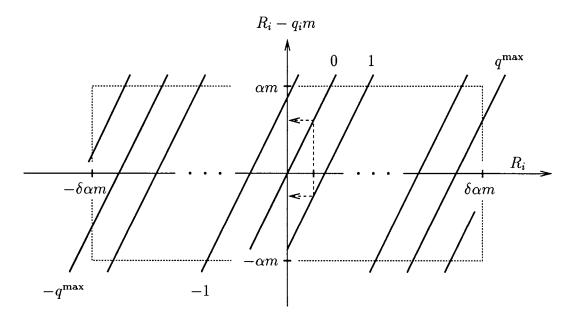

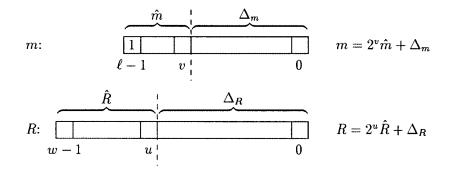

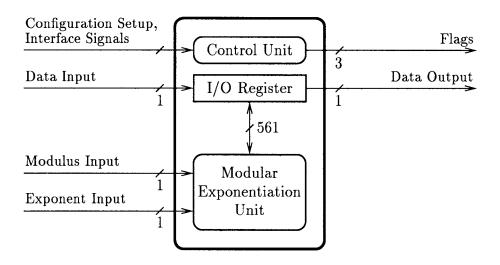

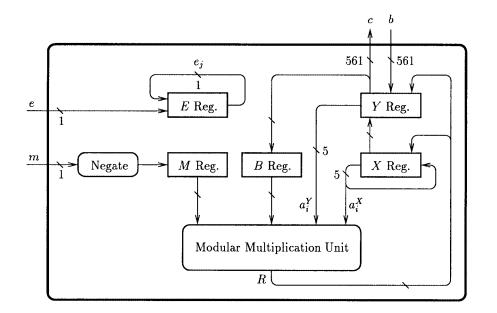

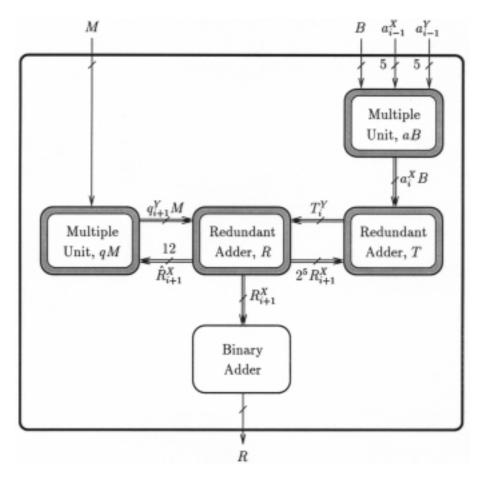

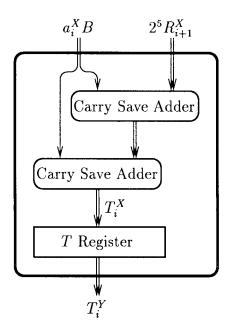

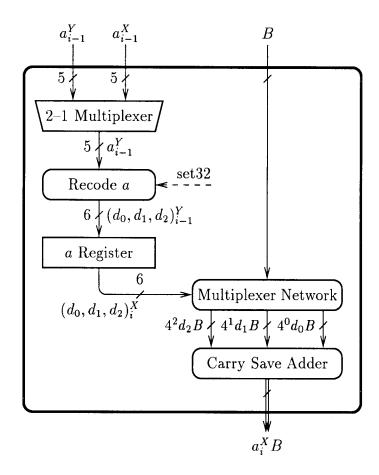

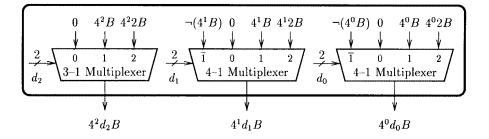

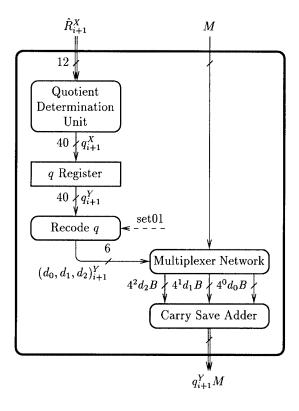

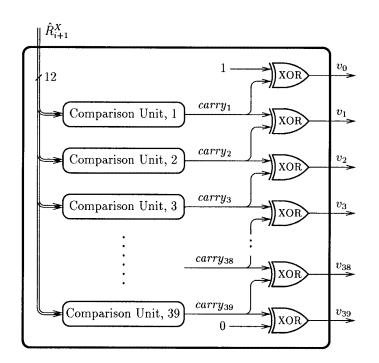

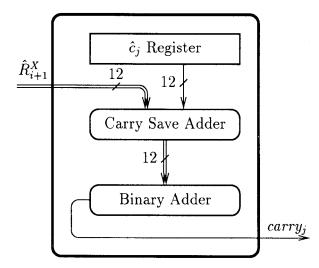

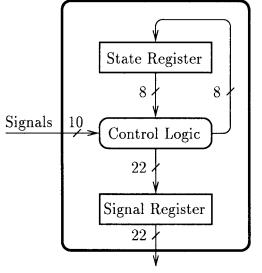

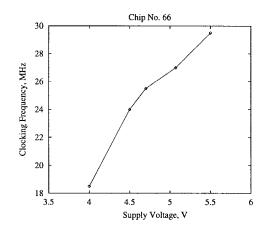

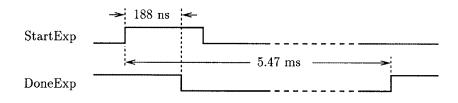

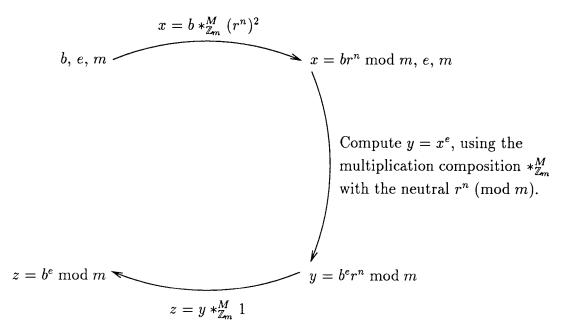

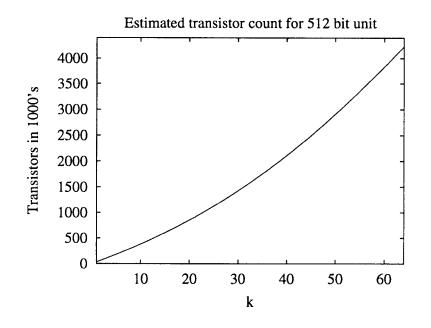

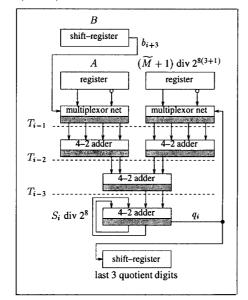

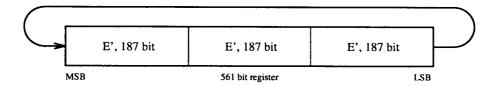

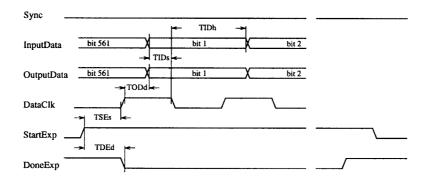

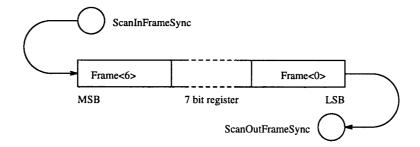

$$b^{e} = b^{e_{0}2^{0} + e_{1}2^{1} + \dots + e_{i}2^{i} + \dots + e_{n-1}2^{n-1}}$$