The Design of a Programmable Computer:

A Qualitative and Quantitative Analysis

by

Michael J. Manthey

DAIMI PB-31 JUNE 1974

This work was conducted with the support of NSF grant # GJ-993.

| Institute of Mathematics University of Aarhus             |  |

|-----------------------------------------------------------|--|

| DEPARTMENT OF COMPUTER SCIENCE                            |  |

| Ny Munkegade - 8000 Aarhus C - Denmark<br>Phone 06-128355 |  |

T

#### Abstract

A survey is made of the contemporary state of program construction and subsequently the isolation of the areas where errors and programming difficulties creep in. A machine architecture which attacks these difficulties is then presented, first in its larger outlines, and then a more detailed exposition of its operation. Finally, this machine architecture, which is based on block structure, is quantitatively compared to two "standard" machines (the IBM S/360 and the DEC PDP-10). The result of this comparison is that one should expect superior performance from the block structured machine herein presented, perhaps by as much as a factor of two.

<u>Keywords</u>: block structure, machine architecture, microprogramming, tag bits, delayed binding time, stack machine, dope vector.

| Contents.                                               | page  |

|---------------------------------------------------------|-------|

| Chapter 1. Contemporary Computer Usage.                 | 1     |

| 1.1 Historical Perspective.                             | 1     |

| 1.2 Problems in Applications Programming.               | 5     |

| 1.2.1 HLL Suitability.                                  | 6     |

| 1.2.2 Debugging.                                        | 6     |

| 1.2.3 Summary of Applications Programming Problem       | is. 7 |

| 1.3 Problems in Systems Programming.                    | 7     |

| 1.3.1 Programs that Generate Programs.                  | 7     |

| 1.3.2 Service Programs.                                 | 9     |

| 1.3.3 Programs that Manipulate Programs.                | 10    |

| 1.3.4 Other System Trouble Spots.                       | 11    |

| 1.3.4.1 Linkage/Loading.                                | 11    |

| 1.3.4.2 Interrupts.                                     | 12    |

| 1.3.4.3 Lockout and Events.                             | 13    |

| 1.3.5 Microprogramming.                                 | 14    |

| 1.4 Summary of Contemporary Computer Usage.             | 18    |

|                                                         |       |

| Chapter 2. Design Criteria for a Programmable Computer. | 20    |

| 2.1 Block Structure and Systems Programming.            | 20    |

| 2.1.1 Interrupts.                                       | 22    |

| 2.1.2 Multi-tasking.                                    | 22    |

| 2.1.3 Storage Protection.                               | 22    |

| 2.1.4 Conclusions on Block Structure.                   | 22    |

| 2.2 Data Representation.                                | 24    |

| 2.3 Evaluation of Expressions.                          | 25    |

| 2.4 Procedures and Parameters.                          | 31    |

| 2.5 Compiler Considerations.                            | 32    |

| 2.6 Binding Time.                                       | 33    |

| 2.7 Input/Output.                                       | 33    |

| 2.8 Conclusion.                                         | 34    |

| Chapter 3. The Design of the Programmable Computer.     | 36    |

| 3. 1 Pushdown Stack.                                    | 37    |

| 3. 2 Block Structured Addressing.                       | 40    |

| 3. 3 Memory Structure.                                  | 48    |

| 3. 4 Descriptors, Pointers, and Indexing.               | 48    |

|                                                         |       |

|                                                       | page |

|-------------------------------------------------------|------|

| 3.4.1 Descriptors.                                    | 50   |

| 3.4.2 Relocatible Addresses.                          | 50   |

| 3.4.3 Indexing and Contiguous Descriptors.            | 52   |

| 3.4.4 Pointers and Logical Addresses.                 | 56   |

| 3.4.5 Summary of Descriptors, Pointers, and Indexing. | 59   |

| 3.5 Opcode Structure and Code Stream Maintenance.     | 59   |

| 3.5.1 Short Operators.                                | 60   |

| 3.5.2 Long Operations.                                | 60   |

| 3.5.4 Code Stream Maintenance Registers.              | 64   |

| 3.5.5 Local Branches.                                 | 64   |

| 3.5.6 Non-Local Branches.                             | 64   |

| 3.6 Procedures and Parameters.                        | 64   |

| 3.6.1 Disabled and Enabled Code.                      | 64   |

| 3.6.2 Preparing to Enter a Procedure.                 | 66   |

| 3.6.3 Supplying the Parameters.                       | 67   |

| 3.6.4 Entering the Procedure.                         | 68   |

| 3.6.5 Exiting a Procedure.                            | 69   |

| 3.6.6 Summary of Procedures and Parameters.           | 69   |

| 3.7 Overall Structure of the Programmable Computer.   | 69   |

| 3.7.1 Tasks and Blocks.                               | 69   |

| 3.7.2 The Stack Vector.                               | 73   |

| 3.7.3 The Interrupt Procedure.                        | 73   |

| 3.8 Virtual Memory and Paging.                        | 75   |

| 3.9 Semaphores.                                       | 77   |

| 3.9.1 Semaphore Code Descriptor.                      | 77   |

| 3.9.2 Semaphore Pointer.                              | 79   |

| 3.9.3 Semaphore Data Descriptor.                      | 79   |

| 3.10 Generators.                                      | 80   |

| 3.11 Support of Sub-emulators.                        | 80   |

| 3.11.1 Emulator Storage Descriptors.                  | 80   |

| 3.11.2 Entering an Emulator.                          | 83   |

| 3.11.3 Life within an Emulator.                       | 84   |

| 3.11.4 Exiting an Emulator                            | 85   |

| 3.11.5 Some Final Observations on Emulators.          | 85   |

| 3.12 Input/Output.                                    | 87   |

| 3.13 Summary of the PC Design.                        | 88   |

|                                                     | page |

|-----------------------------------------------------|------|

| Chapter 4. Comparative Analysis of the PC.          |      |

| 4.1 Rationale for the Comparison.                   | 90   |

| 4.2 The Criteria and Data for the Comparison.       | 91   |

| 4.3 Comparison of Data Fetch Operations.            | 94   |

| 4.4 Comparison of Transfer of Control Operations.   | 108  |

| 4.5 Information Theory Approach.                    | 112  |

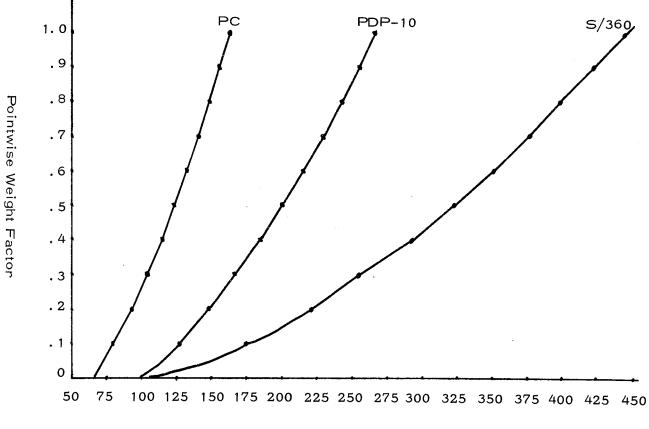

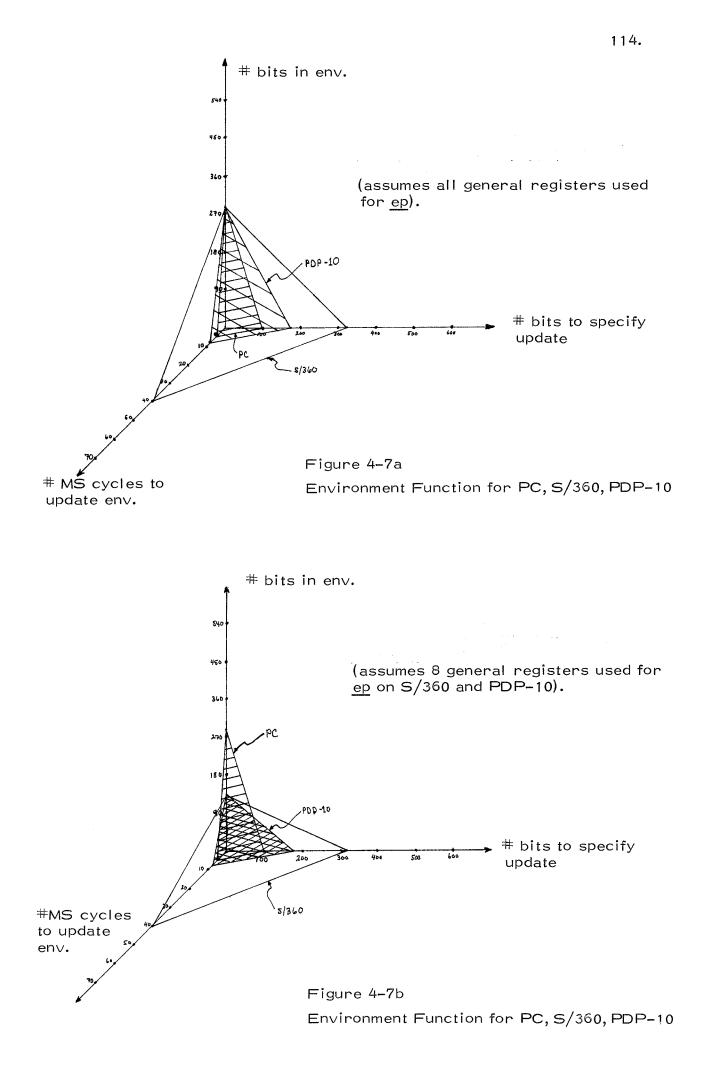

| 4.6 The Environment Pointer.                        | 113  |

| 4.7 Conclusion.                                     | 115  |

| Chapter 5. Major Conclusions and Future Directions. |      |

| 5.1 Acknowledgements.                               | 117  |

| Bibliography.                                       | 118  |

#### 1.0 CONTEMPORARY COMPUTER USAGE

#### 1.1 Historical Perspective

The usage of computers has progressed far from the days when it was estimated that five Univac I's could totally saturate the national requirements for computation. In large part this advance is the result of the realization that a computer is a general purpose symbol processor capable of far more than just floating point calculations. Indeed, the evolution of operating systems and concomitant software (loaders, assemplers, compilers) parallels the development of the computer as symbol processor. There can be no doubt that the early pioneers in the field would gasp in amazement at the sophistication and complexity of a modern computing system.

The development of these software complexes has not come cheaply, however. The history of computer usage is littered with failures large and small, and even the most glorious software triumphs have sprung phoenix-like from near disaster e.g. the SABRE airline reservation system, the B 5000/5500, and most currently MULTICS (whose Resurrection was by no means assured). Even when software projects have been successfully completed, they have most often been the product of cost overruns and downward-revised performance specifications. Part of this checkered success record is the result of the fascination of computerniks with their toys, their unshakeable faith in the potential of their children!. A second influence has been the unfortunate alliance between software's unprecedented malleability (the bell and whistle syndrome) and the nascent development of software construction, as a science instead of an art. [ The fact that Knuth could contemplate gathering all of programming technology in a unified work and then entitle it " The Art of Computer Programming" is a capsule statement of this situation. A third influence on software technology's stuttering progress is the hardware, the machines on which the dreams are to be realized: that hardware advances were each time hoped to solve the software problem! indicates the position that hardware was felt to hold in the minds

of implementors.

The current status of these problems is as follows:

- While computerniks are still entranced by the computer's potential, 20 years of experience now blends this fascination with realism.

- Fundamental theoretical knowledge of software primitives

(e. g. mass storage queueing, grammars) is slowly being

felt, but the seat-of-the-pants approach is still commonly

found.

- 3. The hardware supplied by manufacturers remains fundamentally unchanged but is garnished with certain features which are obviously required by the software plans e.g. bounds registers.

Looking back over the history of computing i. e. computers, one finds that computers were the creations of electrical engineers, who, until faced ( as they are now ) with the limitations of the speed of light, were in the vanguard of advancing computer technology. However, if we survey the current state of computing, it appears that software, and not hardware, is the stumbling block. It therefore makes sense that hardware must do more that just 'be there on the floor', but rather must take an active role in supporting the environment which software complexes demand.

Unfortunately, 'hardware types' are still much in control of the design process. The following true life parable illustrates the type of problems this causes.

K is a brilliant digital logic designer who is also an excellent programmer. He was told of the inconvenience of performing programmed I/O on devices such as teletypes, paper tape gear, etc. when one would rather relegate such business to a data channel. K himself had experienced this as well. Unfortunately the minicomputer involved did not allow this, so K set out to design a multiplexed data channel which would relieve the software people of their worries. And a wonderful design it was! The programmer had only to set up a table in core which contained the necessary parameters and then fire off the channel. Better yet, K was able to take advantage of some already existing hardware features and thereby build the device very cheaply. At this point it should be mentioned that logic designers are (rightly) obsessed with cost [\$] due (if only) to their formal education. True to form, K decided to build the device with the restriction that the parameter table must begin on a memory page boundary! The software people were horrified, as this caused severe memory allocation problems and restricted dynamic memory management. K's reply was that the restriction saved about \$20 since the low order bits of a register would be zeroes and thus buildable with much cheaper components.

The basic problem was that while K is an excellent <u>programmer</u>, he understands little about the environment in which programs execute. Grounded firmly in his knowledge of programming, he maintained that the restriction represented only a minor inconvenience. K won the day, and due ( in large part ) to the restriction, the device never saw use.

Another common hangup of hardware designers is speed - any operation which takes more than X micro ( nano ) seconds is " too slow ". When faced e.g. with the requirement for a set of semaphore primitives (which might have to make several accesses to memory and perform several different functions), the designer replies

- (1) it's too slow,

- (2) it costs too much,

- (3) and besides, all you <u>really</u> need is a " replace add 1 " which is both cheap and fast !

As in the preceding parable, this kind of reasoning indicates a lack of awareness of the environment in which e. g. semaphores are used. This environment is the dynamic and complex world of the operating system, a world where experience has shown that what can go wrong will go wrong, and hence hardware constructs which diminish the universe of potential bugs are valuable regardless of their speed or other such myopic qualities. After all, a program which runs with blinding speed, but usually crashes due to unfindable bugs, is of no value to anyone. The use of hardware constructs which directly reflect higher-order processes clearly has smaller potential for error than the simulation of these processes via software, which can be subject to unforeseen effects such as interrupts, mis-association of parameters or other names, violation of usage convention, or accidental overwriting. Thus what is needed is for the hardware to be structured in such a way as to create a comfortable <u>environment</u> for programs to execute in, an environment in which whatever basic operations are necessary can be stated as hardware primitives. If all the basic software operations e.g. expression evaluation, indexing, semaphores, etc. have counterparts in the hardware environment, then the 'distance' between the source language program and its implementation in hardware is greatly diminished, and concomitantly the universe of potential errors which enter as the result of improper bridging of the gap.

This 'distance' between the source language and the object computer can be seen to be proportional to the size of the so-called 'runtime environment': if the distance is great then the runtime environment is large, and vice versa. Thus a true e. g. Fortran machine would have no code devoted to runtime support. The seemingly ideal situation of completely hardware-based environmental support is not realistic, however, in view of the fact that contemporary computing requirements are for multiple languages on the same computer, and hardware which is suitable for Cobol I/O or Fortran addressing may not be for Algol or PL/I. In addition, certain aspects of the environment are most cost effectively accomplished in software e. g. I/O formatting. It can thus be concluded that completely hardware-based environment is not practical.

Impinging on the discussion of substitution of software by hardware is the much bandied about concept of 'efficiency'. Efficiency is usually associated with speed, as well as the converse: inefficiency equated with slowness. We define efficiency as accomplishment of certain specification with the maximum speed, given the available tools. Thus the complaints about early OS/360, bugs aside, are not totally justified since the slowness was only partly due to poor coding or whatever, the remainder coming from the unsuitability of the given tools: the 360 instruction set, etc. A second example is Snobol 4, which runs slowly enough, to be sure, but compared to what?

Efficiency also applies to hardware design, since all hardware is built out of the same logical building blocks. Thus if two groups are given the same specification and one builds it faster (costs being equal), that one is clearly more efficient. But what if the winner were also more expensive? Or what if the specification was to produce a system that minimized software costs? How does one measure?

The preceding discussion reveals that efficiency is a term that everyone understands, but whose meaning is very stippery. Indeed, defining 'efficiency' is not unlike Plato's defining 'the good'. Faced with this impasse, and yet unwilling to abandon the concept, we shall henceforth utilize the working definition that " X is inefficient if it could be done ( in some global sense ) better". Clearly this definition is more efficient that not using the word at all!

With these conclusions in mind, we next ask what contribution <u>should</u> the hardware make toward the environment? The answer is in the form of two choices which delimit a choice spectrum : (1) the hardware does what is minimally necessary with software 'filling in' the gaps, and (2) the hardware does as much as possible while still not restricting a particular language's needs. The former is characteristic of 2nd and 3rd generation computers, while the latter has been approached by several atypical architectures [ 12 ], [ B3 ], [ B5 ]. The principal problem posed by the second choice is the isolation of those primitive features required by <u>all</u> languages and systems, and the following sections examine contemporary programming practicees on the assumption that problem areas grow out of the lack of good environmental support. Isolating the problem areas is therefore the first step in the derivation of ( hardware ) environmental primitives.

# 1.2 Problems in Applications Programming.

Contemporary applications programming (by which is meant programs which fulfill a specific user need e.g. data processing, equation solving) is done almost exclusively in higher level languages (HLL's) such as Cobol, Fortran, Algol, and PL/1, the primary exception being real time applications.

Unfortunately, in spite of the popularity and proven effectiveness of HLL's, construction of even relatively simple programs is often a painful process. Even assuming (possibly incorrectly) that the chosen HLL is appropriate for the problem statement, the programmer still faces the difficulties of debugging, as well as interfacing his program to other programs, data files, and the ubiquitous System.

# 1.2.1 HLL Suitability

The applications programmer faces a dual problem in implementing a program in an HLL. The first is choosing (or learning) an HLL in which to write the program, and the second is adapting his problem to that language. The choice begins with "Cobol, Fortran, or PL/1?" versus a whole menagerie of less common and more special purpose languages. The choise is usually in favor of one of the Big Three since these are the best supported by, and also somewhat standard across, vendors. This situation exists primarily because even supporting three language processors is an awesomely expensive endeavor.

Having chosen one of the common ( and hence familiar ) languages, the programmer is faced with stating his problem within the syntactic and semantic confines of that language. Herein lies the fundamental issue: the program executed by the computer is doubly distant from the original application problem since

- (1) the problem was translated (by the programmer) into the HLL, and

- (2) the HLL was translated ( by a compiler ) into machine code.

The first translation's effectiveness is a function of the programmer's skill and cleverness and the language's suitability, which are more or less user controllable factors. The second, however, directly confronts us with the 'distance' between the source program language and the actual hardware machine.

# 1.2.2 Debugging

Program bugs can be classified as arising out of (1) the programmer's

translation from the problem to the HLL, and (2) the compiler's translation from the HLL to machine code. While the former is an intangible, the latter is ( theoretically ) amenable to action. This action could be in the form of better documentation or improved runtime diagnostics, but the real crux of the problem lies in the 'distance' mentioned earlier which seperates the source program from the object ( machine ) program. In effect, documentation explains how the compiler has bridged the gap ( via the runtime environment and generated code ) between the source and machine program, while the runtime diagnostics may or may not inform the programmer that he has violated certain explicit or ( worse yet ) implicit assumptions of that environment. Most often, these assumptions are based on the raw physical realities of the particular computer involved e. g. word length, type of arithmetic, and addressing peculiarities.

## 1.2.3 Summary of Applications Programming Problems

The preceding sections have discussed the problems faced by the applications programmer : choosing a language and debugging the program. The major conclusion is that the basic problem is the gap between the source language and the object language, the gap being filled by the user-unknown machinations of the compiler and a large and mostly mysterious runtime environment.

## 1.3 Problems in Systems Programming.

This writer's defination of a 'system program' is a program whose data are other programs. As such, system programs perform in the general areas of

- (1) generating programs e. g. compilers,

- (2) providing services to programs e.g. runtime environment,

(3) manipulating programs e.g. loading, scheduling. We now examine each of these areas in greater detail.

# 1.3.1 Programs that Generate Programs

Compilers represent a magnified view of the problems which faced the applications programs: choosing a language, debugging, and system interfacing. The source of this magnification is that a compiler must simultaneously be aware of two environments: its current executing environment, and that of the program it is generating.

For example, a compiler is a large complex program which utilizes broad range of system services and is usually written in assembly language. But because of the known [ productivity, documentation, correctness proving | disadvantages of a large program written in assembly language, the contemporary trend is toward HLL's with special packed tables ) is such that to state these manipulations in an HLL without such special features implies intolerable inefficiencies. Since additionally compilers are being written in their own language ( implyingtherefore that the compiler and user runtime environments are one and the same), the question now arises of the extent to which the 'special features' should be available to ordinary users - in view of the fact that system integrity could thereby be compromised. Yet such features as runtime availability of the symbol table and the ability to build code at runtime are obviously desirable. [ It should be observed at this point that the severity of this dilemma is lessened if a compiler is not 'special' to the system i. e. the hardware-software complex is such that even misuse of system services affects only the user program.

The gap between the source language to be compiled and the target machine also has the same doubled effect mentioned above. A compiler written in an HLL is itself remote from the object-form compiler, and must also generate code which plugs this gap. The wider the gap, the more difficult it is to bridge and the less efficient is the resulting compiler.

The issue of system interfacing in a compiler is particularly severe since the compiler must generate calls on service routines which will be executed by the generated program in a manner which is not completely predictable at compile time. Therefore the service routines must be general, extremely self-protective, and able to deal with a myriad of possible situations ( this last being particularly true of time dependent functions such as I/O).

In summary, compilers are faced with the following problems:

- -the nature of the compilation task versus the capabilities of the hardware host machine

- -the nature of the compilation task versus the capabilities of the target machine

- -the extent of user access to compile time information and abilities.

## 1.3.2 Service Programs

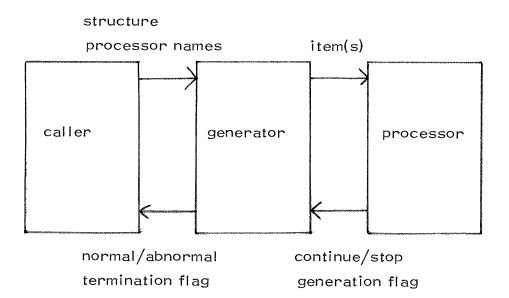

Service programs fall into two categories - those which can be viewed as subroutines (e.g. conversions) and those which must be viewed as co-routines (e. g. buffered I/O). The former tend to be small and logically simple functions which are very concerned with the conventions ruling themselves and their fellows; the latter are distinguished by their logical complexity and intimate relationship to the operating system. Likewise, the service subroutines are closest to the user and should be concerned with divining the cause of errors so that the user can be informed of the error in terms that relate to his source program; in contrast, the coroutine services tend to be invisible to the user and exclusive of simple user exceptions (e.g. end of file), any errors which they detect represent bugs or actual errors in the object code, whether due to the compiler or user self-destruction. Experience has shown that determining how code came to be destroyed is extremely difficult and we should therefore strive toward an environment in which such is not the case.

We should also take note of the peculiar nature of almost all service programs in that they give the user the ability to temporarily step outside of his formal execution environment i. e. they are a system approved means to 'break the rules'. As an example, consider type conversations : they are defined as an automatic mechanism in the Fortran, PL/1 etc. machine, but must necessarily be accomplished outside that environment. Often the System provides analogous services to the environment itself e. g. storage requests.

Since the fulfillment of such requests without error is so critical to the System, it must ensure that these routines are protected from accidental damage. In 3rd generation machines this has been accomplished through the Supervisor Call mechanism which asks the System to execute a piece of code which is not in the user's address space. This scheme is easy to implement on contemporary machines but in turn imposes an interrupt burden on the System. It is important to note that the purpose of this mechanism is not to <u>prevent</u> the user from invoking the service routine, but merely to ensure the integrity of the code. This scheme is used because the storage protection mechanism on most contemporary machines have insufficient resolution to allow multiuser access to code while ensuring entry only at designated entry points and forbidding write operations therein. Clearly it is desirable to relieve the operating system of the interrupt burden so long as the other constraints are met.

## 1.3.3 Programs that Manipulate Programs.

This category of system program is essentially the nuclear operating system plus allied functions such as the spooling and file management subsystems. The nuclear operating system includes the linkage editor/ loader, traffic controller and scheduler, memory and I/O device manager, and interrupt handler; these functions usually communicate with each other through a number of global tables which contain the status of all entities in the system.

The nuclear system is itself not very large, but is logically intricate due both to the complexity of the job it is doing and the presence of interrupts. It would be very helpful to be able to write the operating system in an HLL, but two considerations have traditionally discouraged this : the requirement for object code efficiency, and the lack of source language constructs for e. g. interlock, interrupts, and multi-tasking. Additionally, if the operating system is written in an HLL, then it is actually executing on an HLL machine and must move outside this machine when it wishes to break certain rules, as an operating system is wont to do. Note that this situation is exactly analogous to that of a compiler written in its language.

The reasons for the desire to write in an HLL are the usual ones clarity of statement, and ease of maintenance and debugging; these considerations are especially important when one considers the magnitude of coding represented by a full system. The requirements of efficiency and necessary language constructs have been the stumbling blocks; nevertheless, several outstanding examples exist of systems written in HLL's, notably the Burroughs MCP's and MULTICS. In the case of Burroughs, the hardware has been structured so that compilation is quite efficient, whereas MULTICS uses a PL/1 subset which contains only what is needed coupled with a compiler and documentation which together yield acceptable object efficiency.

The question of 'whither HLL' aside, operating systems in general can be characterized as having overlong childhoods and being rather fragile in adulthood. OS/360 is a case in point, but is by no means alone. They can also be characterized as being too large, too complicated, and too slow - this latter in spite of being written in assembly language. One exception to this bleak picture, but chiefly with respect to efficiency, is Burroughs who claims [ D4 ] system overhead on the order of 5-10 % while most systems are in the 15-25 % bracket.

## 1.3.4 Other System Trouble Spots.

## 1.3.4.1 Linkage/Loading.

The initial concept of a loader was a program which simply loaded an object program into memory. Unfortunately this happy state of affairs was quickly followed by a large number of demands on the loader's abilities: satisfaction of external addresses, overlay structures, memory ( data ) initialization, partial linkage etc. The result is that on most systems the loader is an exceedingly complex and creaky program, one that takes an inordinate amount of time to get rolling even for a trivial job; and heaven help the user who attempts to use the more exotic socalled 'standard features' – if they work, it usually is different from the manner specified in the documentation.

The root of the problem lies in the type of address space used by most computers: linear. The linear address space forces the System to demand that a program lie in a (address-wise) contiguous area of memory, and thus the loader must build a monolithic load module. Since the same loader is usually used for user jobs and the entire system, it must be prepared for even the most incredible eventualities relative to table space and options. Additionally, all external addresses must be resolved, whether or not they are ever invoked. It is safe to say that if loaders did not have to resolve external addresses and link everything together all at once, they would shed most of their problems. It is possible to structure hardware to help in this endeavor, as we shall see.

## 1.3.4.2 Interrupts.

An interrupt can be viewed as a time-random procedure entry in a program; as the result of some hardware generated condition, a procedure entry is forced to some environmentally-defined location, where execution is resumed. [ In most computers, this is accomplished by saving the program counter in a register, then setting it to the interrupt routine address. If the register contents should be destroyed, there is absolutely no way to either recover or possibly even to figure out why you are where you are. ] Presumably the interrupt handler does whatever it deems necessary and then causes execution to proceed once more from the point of interruption. As far as the typical user program is concerned, there are no problems.

However, if the interrupt should occur while the System is itself performing some state-dependent function, and the interrupt routine unknowingly modifies the state, disaster invariably ensues. The obvious solution is to allow interrupts to be disabled and enabled under program control, which works fine as long as interrupts are not disabled too long - after all, an interrupt often represents the occurrence of a time dependent event, and as such, cannot be ignored over long. Furthermore, some interrupts are more time critical than others, and many computers allow interrupts to be enabled/disabled on a proirity basis.

Especially in older systems, the interrupt handler always operated with interrupts disabled due to the difficulty of design which would otherwise be necessary. Indeed, most contemporary operating systems are either partially or entirely nonreentrant, and rely on interrupt discipline and coding conventions to prevent reentry to nonreentrant code.

## We can conclude that if interrupts

(1) could be forced in such a way that the path was unlosable, and

- (2) weren't time dependent, and

- (3) all code was reentrant, and

- (4) code which shouldn't be interrupted or reentered absolutely couldn't be,

then the impact of interrupts on operating system design and stability would be minimized.

## 1.3.4.3 Lockout and Events

The fourth item in the list above – code which can't be interrupted-is the subject of a classic paper by Dijkstra [D2], who denotes such code 'critical'. An example of critical code would be a routine which is responsible for updating a multiple entry table: if an interrupt occurs before all the entries have been made, and in the course of processing the interrupt this routine is reentered, the table will hereafter contain invalid information. Dijkstra demonstrates that this problem can be solved by the use of 'semaphore' variables i. e. variables which can be updated without possibility of being 'seen' in their transitory state by another piece of code.

While Dijkstra's paper assumes that multiple processors are executing cooperating pieses of code which must be coordinated by the use of semaphores, a single interruptable processor executing on logically distinct processes interrupts poses the same problems. In traditional computing systems, the situation has been resolved either by disallowing interrupts throughout the (logical) vicinity of critical code, or by using the increment memory (" replace add 1") feature, or a combination of the two. The increment memory instruction constitutes the necessary primitive to accomplish the semaphore strategy. In actual operation, what happens is that a process will increment and test the semaphore, and if it finds the semaphore 'busy' must either (1) continue to poll the semaphore until it becomes 'unbusy! (very wasteful of compute time) or (2) ask the System to place it in a wait state until the semaphore clears. Current terminology for this situation is 'waiting for an event', although events are not restricted to being semaphores e. g. an interrupt.

While it is true that Dijkstra's semaphores are useful primitives, they demand more than 'increment memory' to be truly efficient e. g. suppose

process A locks semaphore S, and then process B 'blocks' on S and is queued by the System. Now process A unlocks S; if the unlocking action neglects to inform the System that S is now unlocked, B is blocked forever. This can be avoided with today's hardware, but multiple instructions and programming conventions are required; in addition, the semaphore is associated with its target variable only by convention, not by hardware, and therefore bugs can creep in via misassociation. The problem of 'deadly embrace'[2] is a meta-problem in this context, and as such is outside this scope of this paper[see H3].

Another inefficiency deriving from the need to use multiple instructions to test and react to semaphores is that several different types of critical code are involved i. e. producer/consumer, non-reentrant code, and data lockout. While it is true that all can be accomplished using simple semaphores, usage becomes clearer and more efficient if the different types of lockout are available [R2], [H1].

Thus far the discussion has been directed toward the System's use of semaphores. However, contemporary usage e. g. real time subsystems, cries out for allowing user programs as well as the System to spawn subtasks coordinate their activity via semaphores and event variables. Furthermore, these facilities are most needed in HLL's since users prefer to write in HLL's and also because the System can then use the compiler to enforce adherence to conventions. Clearly if an arbitrary number of users in a large multiprogramming system wish to declare semaphores, the operating system will swell in size if it is demanded that semaphores be known a priori thereto; therefore we postulate that semaphores should operate in such a fashion that they need not be known before-hand to the System, and need only be of concern to the System when a task blocks or unblocks.

In summary, it is desirable that both system and user programs be able to spawn and coordinate parallel processes in a simple, clear, and flexible manner.

## 1.3.5 Microprogramming

This section deals with microprogramming as it impacts systems (and user) programming i. e. microcode as a resource, and not microprogramming as an implementation technology. We include it, besides for its own merits, to point out that a System must be forward looking relative to new and unique demands for allocation and control; the discussion also illustrates that often times what may seem new is really an old problem in disguise : in this case multiprogramming and block structure.

When the IBM Corporation announced System/360, it also provided emulators for prior systems (1400 and 7000 series machines). Although these systems were (usually) implemented 'on the 360' via microprogramming, there was no capability provided to multiprogram these emulators i. e. if the 7090 emulator was in use, this precluded the use of the hardware as e. g. a 360, with consequent disruption of job stream scheduling. System/370 attempts to remedy this problem by allowing emulators to be multiprogrammed within certain limitations, but in essence, when a given emulator is in control, the entire system acts as if it were e. g. a 1401. Upon occurrence of an interrupt or when control is transferred to the 370 machine, the 1401 machine logically disappears and the system is a 370. The barrier between the 370 and the other emulators is arranged to preclude any real communication between them.

At the present time, IBM and other vendors prohibit the user from tampering with or adding to the microcode. This is done for reasons of propriety and maintenance, but pressure from users of smaller computers which encourage experimentation with microprogramming will eventually force the large manufacturers to allow the use of microprogramming as a resource, and eventually all operating systems will be expected to allow multiprogramming of emulators. Unfortunately, the emulators which users are likely to construct will be for machines which have hitherto not existed. The following problem now arises : a computer is of no use without software-compilers, I/O drivers, loader, storage and file management disciplines, etc. Whereas the IBM emulators execute problem program cum operating system within the emulator partition ( thus supplying the problem program with a ready made software set ), new emulators will not have such a ready made system to greet them. The choice now facing the owner of a new emulator is between the nontrivial difficulties and expense of constructing a new software complex or finding a way to bridge the gap between his emulator and an existing system.

At this point it is useful to distinguish between two types of microcode

a user might write: simple extensions/replacements to the existing instruction set, or a complete subsystem (although the latter can be viewed as an extreme case of the former). The destinction is useful because it enables one to draw an analogy with extensible languages.

The discussion on Application Programming stressed the gap between the user's problem and the language in which it must be stated. Extensible languages are seen in many quarters as the bridge across this gap. In general, such languages allow new operators to be defined upon entry to a block which become undefined upon exit from the block. Such extensions constitute an execution environment which is elaborated by cascading the extended statement into calls on procedures in outer blocks. In figure 1.3.5-1, the 'less than' operator can be looked upon as such a procedure, to say nothing of the routine which coerces <u>inte-</u> gers to <u>reals</u>.

Clearly the example of the figure represents a trivial case of the type of extension which can be specified, and more extensive definitions would result in a more deeply nested sequence of procedure elaborations. Thus the user of such language extension features must pay for his 'convenience' in increased execution time, which is to say: emulation of a computer which simulates the desired execution environment. If however the extensions were implemented using microcoded subroutines, then the user could have the best of both worlds.

Unfortunately, the user with his microcoded language extensions still expects to be able to multiprogram jobs written in his augmented language, with perhaps different jobs employing different microprograms. Hence the liberal support of a microcode-extended language is tantamount to multiprogrammed emulation.

We have now gone full circle on the subject of multiprogrammed emulation in the sense that we have argued that a demand for multiprogrammed emulation arises out of the seemingly disparate areas of extensible languages and emulation of new computers. However the digression has paid a dividend if we notice that such language extensions, whether accomplished through procedures or microcode, always operate on a <u>block</u> basis. On the other hand, emulators are also implemented using micro-

```

op min = (real a, b) real: (a<b|a|b);

.....statements using min of two reals.....</pre>

```

# end

$\not c$  above <u>min</u> operation now no longer exists  $\not c$

# begin

end

$\notin$  examples from [L1]  $\notin$

# Figure 1.3.5-1

Algol 68 Program Skeleton Illustrating the Declaration of Operators within Block Structure Scope Definition Regulations. code. Language extensions operate on a <u>block</u> basis, so should the computer emulator. If we therefore complete the analogy and state that computer emulators should also be viewed as blocks, we have the key to multiprogrammed emulation, since multiple tasks can be thought of as parallel blocks.

The next chapter delves more deeply into the relationship between block structure and multiprogramming and it will be shown that a computer architecture that supports block structure ( and therefore multiprogramming ) well would be amenable to the inclusion of the ability to support multiprogrammed emulation. See [ 3.11 ].

## 1.4 Summary of Contemporary Computer Usage

The preceding sections have dealt with the contemporary problems of application and systems programming. With regard to the applications programmer, we saw

- (1) most programming is done in HLL's,

- (2) these HLL's do not correspond well either to the user's problem or the hardware on which they execute,

- (3) this lack of correspondence is a breeding ground for programming errors and bugs.

With regard to the systems programmer we found

- (1) a need to program in HLL's which is frustrated by the unsuitability of the hardware,

- (2) system software is very complicated, yet it seems that much of this complication is due to the unsuitability of the hardware,

- (3) this complication causes system software to be slow to stabilize, bulky, and inefficient,

- (4) even operating system primitives such as storage protection and semaphore processing are only minimally supported by the hardware,

- (5) there is a need to be able to easily write reentrant code,

- (6) there is a need to support user-program subtasking,

- (7) there will be a need to support multiprogramming of user microcode under existing software.

In conclusion we can state that in general, programs seem overly difficult to write and debug (particularly system software), and that ultimately the blame falls on an environment which is too much software and not enough hardware.

The remainder of this paper describes and evaluates a computer architecture which attacks the problems heretofore described by providing the supportive environment which has been lacking. The design is not perfect, but experience in writing a compiler and operating system for this machine indicates that it <u>is</u> eminently and efficiently programmable in a higher level language. That in itself is progress.

# 2. 0 DESIGN CRITERIA FOR A PROGRAMMABLE COMPUTER

This chapter presents design criteria which derive from attacking the software problems described in Chapter 1. In general, we are looking for a computer architecture which is a good host for divers higher level languages and system software. The latter therefore implies that our computer must be a good host for multiprogramming, subtasking, time sharing, and new developments such as user microcode. Although PL/I has demonstrated the problems of trying to be all things to all users, we shall demonstrate that the environment requirements of [ 1.0 ] can be accomplished while the overall structure remains fundamentally simple.

Our first topic is block structure, as well it should be, since the majority of extant HLL's are block structured. Clearly an architecture which is a comfortable host for HLL's would be of great value to applications programmers, but it would be unfortunate if such an architecture were unsuitable for the systems programmer.

# 2.1 Block Structure and Systems Programming.

This section explores the relationship between block structure and systems programming (or rather the logical structure of systems). Let us begin by stating some of the characteristics of block structure:

- (1) the nesting of blocks yields a tree structure,

- (2) data and code entities are known only to subsidiary portions of the tree,

- (3) dynamic allocation of storage is inherent,

- (4) recursion is inherent (given the existence of procedures).

The analogous characteristics of a running system are:

- (1) the nesting of tasks and subtasks yields a tree structure,

- (2) data and code entities are known only to subsidiary portions of the tree,

- (3) dynamic allocation of storage ( to tasks ) is inherent,

- (4) recursion is inherent (given the existence of interrupts).

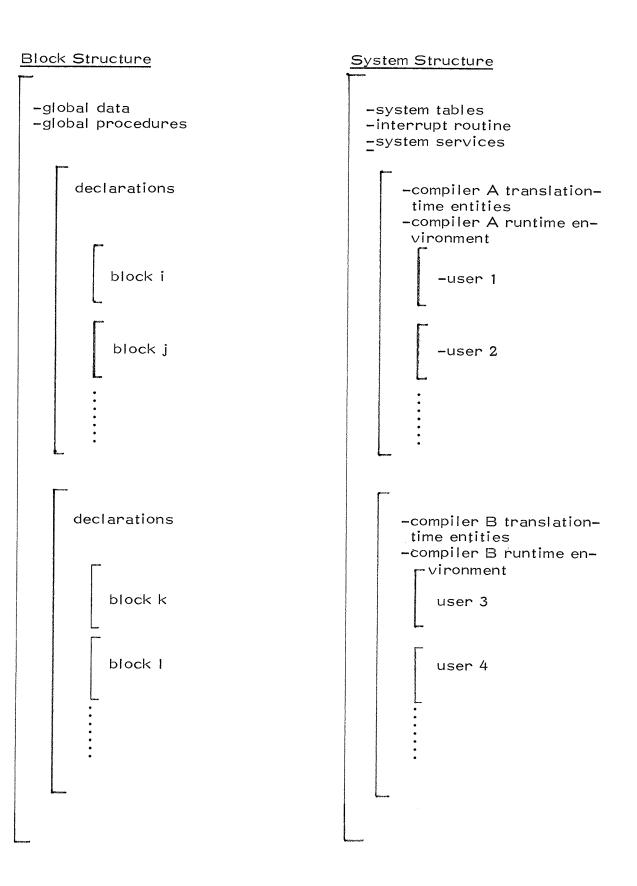

One can see that the analogy is very close, as Figure 2.1-1 illustrates. We now consider more carefully the application of block structure con-

Figure 2.1–1 Illustration of the Similarities between Block Structure and System Structure. ,

cepts to system structure.

#### 2.1.1 Interrupts.

As shown in the figure, the operating system is global to all other entities in the system, and therefore so is the interrupt processibg procedure. Thus processing an interrupt can be regarded as a (block structured) entry to a global procedure, with the interrupt type, etc. as parameters to this procedure. Nested interrupts merely cause the interrupt routine to be entered recursively. A subsidiary dividend is that subtasks can directly invoke the interrupt procedure, whether to signal 'soft' interrupts or external interrupts (e. g. for testing purposes).

#### 2.1.2 Multi-tasking.

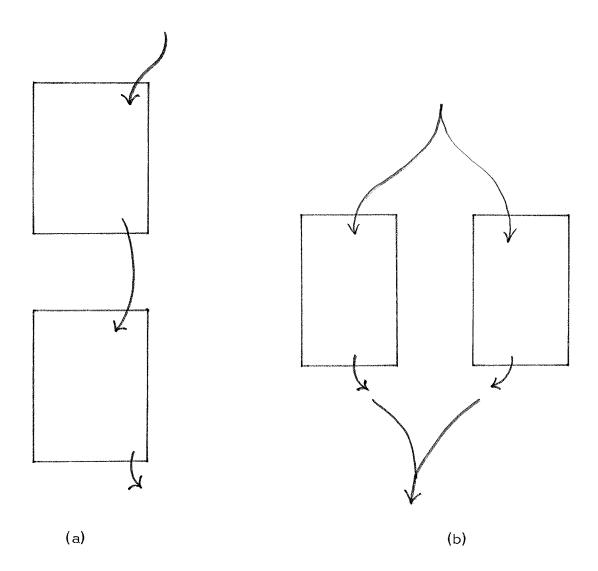

Consider a program in which two blocks exist on the same lexical level. Normally the two blocks would be executed in serial fashion – firstone, then the other. If however it made no difference in which order they were executed, then they could in fact be executed in parallel. See Figure 2. 1–2. The ability to execute in parallel is not restricted to blocks which have no common data; however, the sharing of data between parallel processes requires some mechanism such as semaphores to prevent ambiguity. Looking now at our two blocks executing in parallel (sharing or not sharing data), they have the same characteristics as two parallel tasks. Thus it would seem that an architecture which supports blocks ought to be able to support tasks with minor extensions.

#### 2.1.3 Storage Protection

The scope rules of block structure provide exactly a type of logical storage protection that is lacking in modern systems: if we accept the analogy between parallel blocks and parallel tasks, then disjoint tasks (jobs) cannot 'see' each other, subtasks can see their parent but not each other, and all can see their global environment, i. e. the runtime environment and the operating system. Furthermore, since only the procedure head ( and not its interior ) is 'visible', it is impossible to enter any procedure ( especially crucial system routines ) except at the designated entry point.

#### 2.1.4 Conclusions on Block Structure

The close analogy between block structure and system structure; the nat-

The arrows denote the path of execution.

Figure 2.1-2 Two Independent Blocks (a) Can also Execute in Parallel (b).

ural application to interrupts, tasking, and storage protection; coupled with the ubiquity of block structured languages; altogether comprise a compelling argument for hardware which conforms closely with the requirements of block structure.

## 2.2 Data Representation.

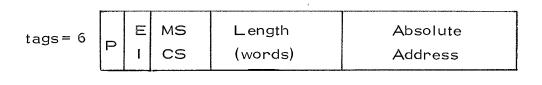

The basic data which programs manipulate are numbers, characters, and bits; furthermore these entities are often processed in groups which are commonly referred to as arrays, character strings, and bit strings. The more closely the environmental support of these latter entities resembles the source language semantics, the easier it is for the compiler to generate good code and the more likely that the environment can detect a violation of the source semantics. A particular case is array/string bounds violations: automatic hardware recognition of this condition not only aids during the formal debugging phase, but also recognizes that a program is never really ever completely bug-free.

A fourth type of data is addresses or pointers. Until recently, pointers were not supported by HLL's, and this lack only enhanced their unsuitability for systems programming. It is therefore helpful to both applications and systems programmers to include pointers in the HLL's, and given that a pointer appears to be merely an address; one would think that hardware support of this construct would be easy.

The first inkling that such is not the case appears when one realizes that the mapping of data onto the address space (1) is unknown to the user, and (2) often does not correspond to the lexical ordering of entities in the source program i. e. add one to an address, and you may not get a pointer to the expected variable.

Worse yet, there is great impact on the System if user programs can retain absolute addresses since this precludes the System from moving programs around in memory. Therefore if we want pointers in our source language, it is imperative that the environment support them in a relocatible form.

We must also note that pointers have the characteristic of being used as

a pseudonym for either a single datum or an entire set of data. Either the compiler (via its generated code) or the hardware must be cognizant of this distinction, since data arrays require indexing and simple data do not.

We have thus far discussed how the environment ought to support numbers, characters, bits, arrays, character and bit strings, and pointers. What about linked lists, associative arrays, array crossections, etc.? At this point we must consider the tradeoff between supporting them directly in hardware and forcing the compiler to generate code which implements them in terms of the existing structures. Clearly neither alternative is particularly desirable. Forinstance, besides the fact that a hardware implementation would be rather complicated, there are the two remaining problems of (1) choosing a particular set of semantics from the many possibilities ( e. g. singly or doubly linked lists?), and (2) melding these constructs into the existing environment so as to retain consistency and generality ( e. g. linked code ?).

In addition to choosing between compiler and environment support for such data structures, we can beg the issue by doing neither but providing the ability to extend the environment to allow later inclusion. The discussion in [ 1.3.5 ] of user microprogramming bears on this topic, and [ 3.11 ] discusses the required environmental 'hooks' for convenient microcode extension.

## 2.3 Evaluation of Expressions.

The sequential nature of (contemporary) computers dictates that the parenthesized manner in which humans write arithmetic expressions be linearized. This linearization is performed by the syntactic parsing of the compiler to produce an intermediate form called polish notation [G1] (although in many compilers, code is generated with the polish string's existing only implicitly). At this point the compilers' treatments (of the polish string) diverge due to differences in the target hardware.

If the target machine contains multiple general purpose registers, then the compiler must keep track of which registers are in use and deal with the movement of temporary results between the registers and memory. This inefficiency at compile time is (hopefully) recovered during execution since movement of temporaries between the registers and memory occurs only when necessary. If however the target machine is capable of executing the (reverse or suffix) polish string directly (KDF 9, B5500/6500 computers), then the compilation speed increases and execution speed decreases according to the number of temporaries and the number of top-of-stack registers on the machine [W6].

The most commonly heard arguments against direct execution of polish strings revolve around this very point of memory accesses. We now examine them.

#### Argument #1

Consider the expression "A: = B+C;". The reverse polish coding of this expression if "aAvBvC+:=" where 'a' denotes 'address of', 'v' denotes 'value of', and ':=' is the assignment operator. A machine which executes strict reverse polish would require the following code:

- -load the address of A

- -load the value of B

- -load the value of C

-add the top two items in the stack

-store the topmost item in the stack into the location specified by the second item in the stack.

[Each hyphenated line above represents one instruction with appropriate stack maintenance automatically performed by the hardware.]

The argument says that on a register machine, the STORE instruction contains the target address, and therefore the loading of the address of A onto the stack and subsequent (automatic)maintenance is pure overhead. The origin of the argument is probably the notion that operators (e.g. :=) must be zero address instructions, and therefore the address must be preloaded onto the stack.

The refutation of the argument is to postulate that the STORE operation shall be a single address instruction, just like the LOAD instruction. The object code now becomes

-load the value of B

-load the value of C -add the top two items in the stack -store the top-of-stack item into A

In terms of the actual instructions generated, this is no different code from a register machine (although, depending on the state of the topof-stack registers, there may be an extra stack manipulation).

## Argument #2

"But wait." say the opponents of stack evaluation. "If the expression is complicated, then there must be movement of temporaries between the top-of-stack registers ( of which there are usually 1-3) and main store. Even though the hardware does this automatically, it still takes time to read/write memory."

The argument is valid so far as it goes, but it neglects to consider that the movements can be overlapped (i. e. done at the same time as) the fetch and decode of the next instruction (given memory interleave and/ or multiple instructions per word). Moreover, if the next instruction is a single (instead of zero) address operation, there is even more time since an effective address must be calculated and possibly several memory accesses made.

# Affirmative Point # 1

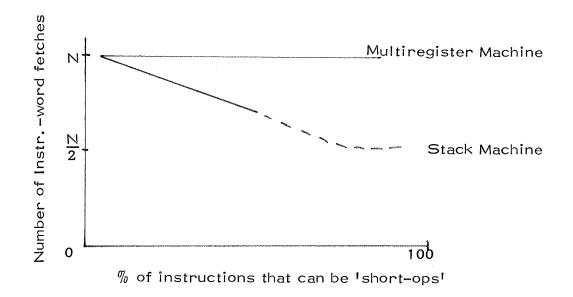

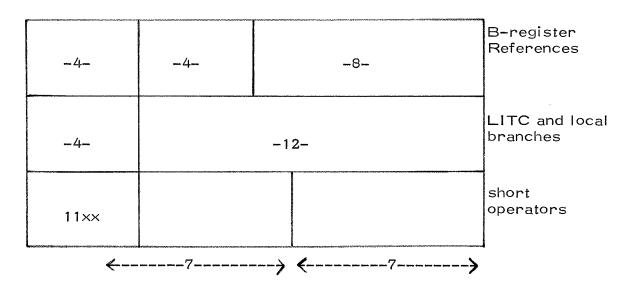

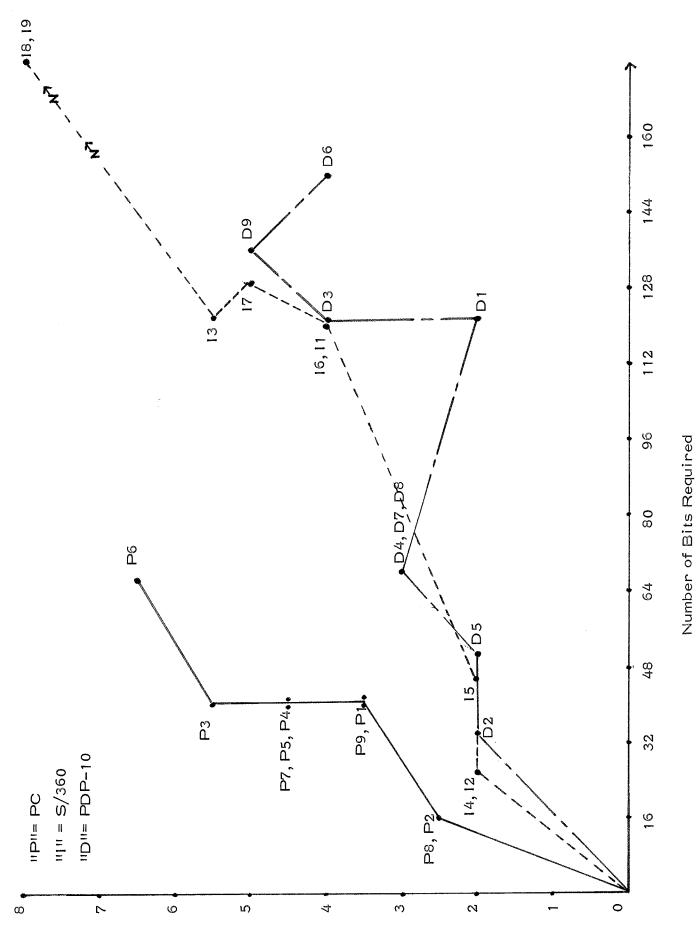

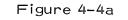

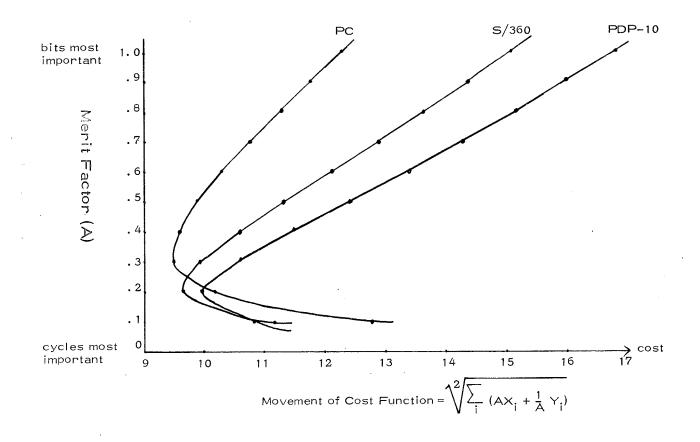

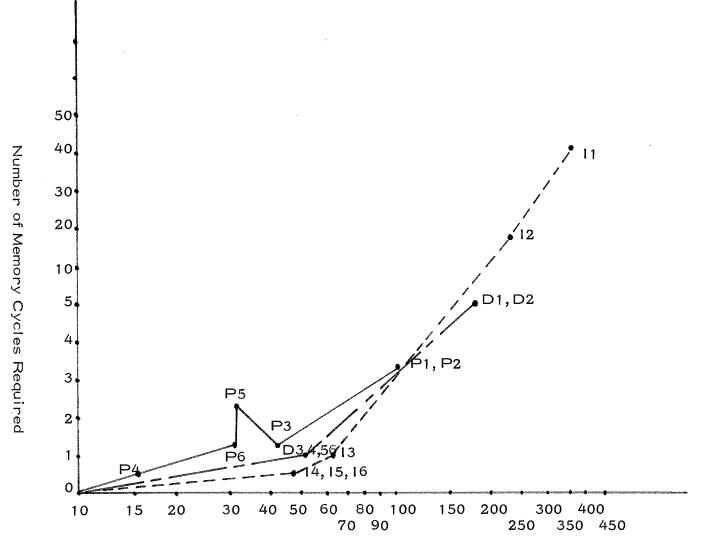

There is an argument in favor of 'polish hardware' which is often overlooked. Since there are a number of registers which can hold operands, an instruction for a multiregister machine must contain therein one (or several) register address(es), thereby increasing the length of the instruction (in bits). In contrast, there is no need for register addresses in a stack machine instruction since the source/destination of all operands is known by the hardware to be the top-of-stack; therefore stack machine instructions tend to be shorter than their multiregister counterparts. Since the instructions are shorter, more instructions can be packed into a machine word, thereby decreasing the number of instruction fetch cycles which must access memory (see Figure 2.3-1).

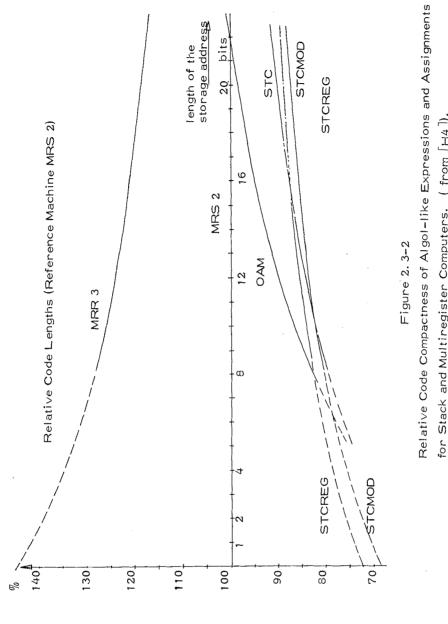

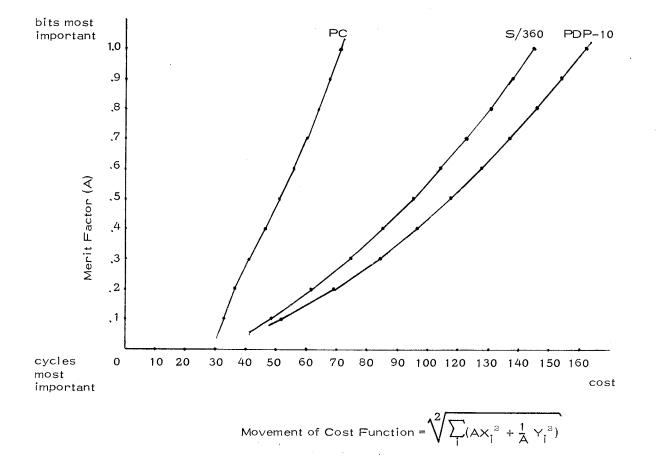

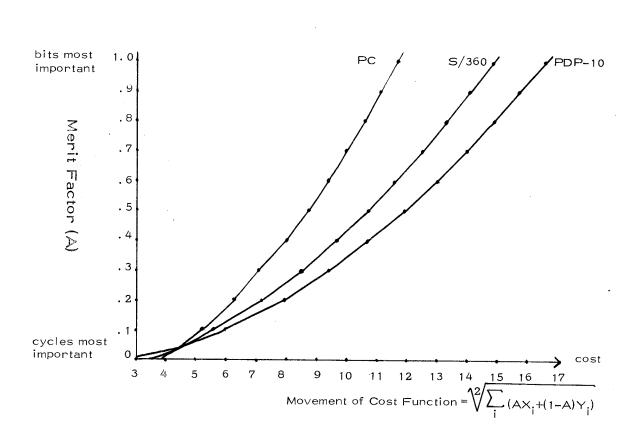

Figure 2.3-2 from [H4] (and see also [W3]) demonstrates that indeed code for stack machines is more compact.

The graph illustrates the fact that a multiregister machine must always specify the source and destination addresses for operands. The short operations of a stack machine  $[e. g. +, -, \wedge]$  on the other hand require no such addresses since source and destination are known to be the stack. The multiregister machine is unable to take advantage of the potential shortening, and consequently cannot achieve the code density of the stack machine.

## Notes:

- Long instructions are memory reference or register-instructions, while short instructions are zero-address stack-oriented operations.

- 2. The graph assumes(a) long instructions for both machines are the same length(b) short instructions are half as long as long instructions.

- 3. The reader should be aware that the figure oversimplifies considerably from the discussion in the text.

- 4. N/2 is an asymptote, since long instructions must be used to load operands onto the stack.

Figure 2.3–1 Number of Instruction-Word Fetches on Multi-register and Stack Machines.

Machine Types:

only between registers. sters or between a re-MRR3: arith metic operations MRS2: arithimetic operations either between regi-STCREG: multiple general gister and memory.

STCMOD: stack machine with ability to address nonregisters plus a stack.

Top-of-Stack elements, relative to the top.

can only address Top-STC: stack machine which of Stack element.

OAM: classic one-address, one-accumulator machine.

for Stack and Multiregister Computers. (from [H4]).

It must be pointed out that multiregister machines coupled with multiple parallel arithmetic units (e. g. CDC 6600) do an extremely effective job in evaluating expressions, whereas the means of accomplishing this on a stack machine is not apparent. The only counter-arguments are the relatively small number of such applications, the expense of such hardware, and that compilers which can take advantage of such hardware are both difficult to write and slow (e. g. CDC 6600 FTN compiler).

## Affirmative Point # 2

Because all operands, including parameters and return addresses, can be stored in the stack, object code for a stack machine is inherently reentrant. A stack is also the usual means of accomplishing the dynamic allocation of activation records [ W2 ] required by e. g. Algol 60 and PL/I AUTOMATIC.

## Affirmative Point # 3

Because the hardware knows where the stack is and how to store and retrieve items therefrom, it can use the stack to hold hardware generated items e. g. return addresses. This is in contrast to the typical register machine wherein the hardware cannot arbitrarily decide to use some of the registers for its own purposes because it doesn't know which ones ( if any ) are unused. Even if some registers were designated as belonging to the hardware , the many possible recursive situations that exist ( e. g. interrupts ) would cause the hardware to attempt to reuse its registers when they were already full.

We shall also see in  $\begin{bmatrix} 2.6 \end{bmatrix}$  that the ability of the hardware to use temporary storage has great impact on the deferral of binding time.

## Conclusion

The two arguments against direct hardware execution of polish strings are refuted above. In favor we have the ease of compilation, code compactness and reentrancy, and applicability to dynamic storage. Thus the decision would seem to favor a stack type architecture from the point of view of expression evaluation. See [12], [M1], [B6] and [W6] for additional discussion.

#### 2. 4 Procedures and Parameters

Procedures (or subroutines) constitute a doubly potent programming tool. In the first place they represent a means of structuring a program so that it can be comprehended, written, and debugged. [Incidentally, one wonders if an equally convenient tasking facility would not have the same benefits! ] Secondly, procedures imply object code compactness by allowing a body of code to be executed 'out of line' rather than being repeated in-line at each needpoint.

We now postulate that the environment should support reentrant and recursive procedures unless this causes undue inefficiency in the resultant object code. This seems reasonable in view of the recursive nature of the operating system, compilers, and artificial intelligence applications such as pattern matching, problem solving, game playing, and list processing in general.

The fact that procedures are out-of-line code means that they require parameters to particularize them for each invocation. The problem that now arises is how changes to the parameters inside the procedure body should reflect back to the point of invocation. Three schemes are in use: call by value, call by reference, and call by name. The first allows no changes to be reflected back to the caller; the second that changes <u>will</u> be reflected, but if the actual parameter is an arithmetic expression, then the expression is called by value; the third that changes <u>will</u> be reflected, and if the actual parameter is an arithmetic expression, references to the value of the parameter will( each time ) cause the expression to be reevaluated <u>in the environment of the caller</u>. This last requirement ( underscored ) turns out to have some rather subtle implications, the resolution of which has had great ( deleterious ) impact on object code efficiency; it was for this reason that PL/1 replaced call by name with call by reference.

The prevailing attitude toward call by name is that while it has its (really nice) uses [K2], [N1], for the most part the inefficiencies outweigh the benefits. Certainly this attitude had much to do with the PL/1 decision to call by reference. By far the thorniest problems with call by name occur when a procedure is passed by name, the problem being that the (block structure) environment at the time of the call must be saved and used with the procedure whenever it is invoked. However, besides the sort of 'tricky neat' uses of procedure call by name, there is one extremely useful one, demonstrated by the so called 'ON conditions' of PL/I.

The idea behind ON-conditions is to allow the programmer the ability to specify certain processing when and if certain exception conditions occur. Call by name has a perfect use here since the user can pass his error procedures by name to the System (at which time the current environment is saved) which can then invoke them when the condition occurs. Since the procedure's original operating environment is applied, the user gets exactly the results he wants, regardless of how far afield he has strayed from the point at which the ON-condition was established.

Since ON-conditions can also be associated with semaphore and other 'events' [ B4 ] the aggregate of usage possibilities for call-by-name argues for its support by the environment.

## 2.5 Compiler Considerations.

This section deals with a rather nebulous concept – that since a compiler tends to be somewhat myopic relative to the piece of source code it is currently processing, the eventual environment architecture should strive to operate in such a fashion that the compiler needn't care wether a particular variable is a formal parameter, actual parameter, name or value referenced, fullword, halfword, byte, bit, loop index ( even expression ), or 'involved' with pointers. Admittedly this is a stupendous wish, yet the payoffs in both compiler size and speed and object time efficiency are equally large.

Clearly if the compiler doesn't worry about these matters, then the environment must. Thus the crux of the problem is that the environment must somehow be able to make the appropriate decision at runtime, which therefore implies that it must have a means figuring out what it is it is supposed to do i. e. there must be a means for the environment to distinguish between several possible courses of action.

Section [3.3] discusses how this can be accomplished.

#### 2.6 Binding Time.

The preceding section was actually talking about something called <u>binding time</u>. Thus, [2.5] was saying that the compiler's life would be considerably simplified if the time at which action (i.e. code) is bound to variables could be deferred to runtime. In fact, binding time has cropped of several times in the preceding pages e. g. [1.3.3].Linkage/ Loading, [2.2] pointers, [2.3] Affirmative # 3, [2.4]ON-conditions.

One can trace the advances in computing by the increasing deferral of binding time e. g.

| 1st | generation | absolute code                                  |

|-----|------------|------------------------------------------------|

| 2nd | generation | relative code and subroutine libraries         |

| 3rd | generation | relocation hardware, virtual memory, incremen- |

|     |            | tal compilation, languages like Snobol 4 and   |

|     |            | APL.                                           |

Wegner states [W1] p. 18 that "Binding attributes as early as possible sometimes results in more efficient program execution, since it saves repetition. However, binding attributes as late as possible allows the decision regarding the bound attributes to be delayed and thereby allows greater flexibility in specifying the attribute". Using the reasoning that efficiency of use for programmers is more important than super-efficient execution by the hardware, we postulate that our environment shall strive toward maximal deferral of binding time.

### 2.7 Input/Output.

Two types of operating system bugs which are exasperatingly difficult to track down are (1) a lost interrupt due to an unexpectedly long lockout of interrupts, and (2) an error in the parameters to an I/O channel which results in its writing beyond the buffer limits. Both of these bugs have the characteristic that by the time they result in a <u>detectable</u> error ( usually unrelated to the real culprit ), all trace of the cause is gone.

The solution to the lost interrupt problem is to make <u>all</u> interrupts nontime dependent, though this seems to be a contradiction. If this can be accomplished, however, then we are in a much better position to make use of semaphores on the System (having resolved Wirth's dilemma in [W5] in which he can't seem to decide whether or not he <u>really</u> wants interrupts). The efficacy of using a semaphore approach is reported by Wirth [ibid] and Dijkstra [D3].

## 2.8 Conclusion

The design criteria established in the preceding paragraphs are

- (1) the hardware should support block structure,

- the hardware should support the source language data types directly,

- expression evaluation should be accomplished by direct execution of reverse polish strings,

- (4) call by name has valid uses and should be supported by the hardware,

- (5) the hardware should allow maximal deferral of binding, implying it can 'fill in' the semantics that the compiler left unbound,

- (6) I/O channels should be cognizant of the logical structures residing in the PC's memory,

- (7) interrupts should be time independent insofar as is possible.

The next chapter presents the actual design of a computer which meets these criteria. Since these criteria were derived from considerations of software "programmability", the computer described in [3.0] is called the Programmable Computer (PC).

#### Preface to Section 3

This section presents the actual design of the PC in a narrative fashion which explains the motivation behind the various constructs that are considered primary or highlights. As a result, some of these are treated in detail while other points are only mentioned.

The knowledgeable reader may become frustrated at the ordering of topics or the apparent missing details. However, the material has been organized for expository clarity to the unitiated and hopefully all the loose ends will have been gathered together by the end. Let us summarize the problems outlined in [1.0] and distilled into design criteria in [2.0]. The Programmable Computer (PC) attempts to optimize throughput by the following considerations:

- (1) ease of program creation via HLL's,

- (2) ease of debugging,

- (3) recognition of the relationship between block structure and multiprogramming,

- (4) recognition of the Dijkstra coordination primitives both between cotasks and between the PC cpu and the I/O processes.

These considerations result in the following design objectives:

- (1) The PC's instruction repertoire should be 'close' to the languages which execute on the PC, thus allowing easy compiler generation, efficient code, and execution time diagnostics relatable to the source program.

- (2) The PC hardware should automatically oversee all program execution ( including the System ) and trap all questionable semantics. This implies the existence of primitive features which allow the hardware to distinguish among different data types, addresses, and code.

- (3) Hardware support of the Dijkstra primitives implies an explicit hardware recognition of task structures i. e. block structure.

The resulting design can be summarized as a machine with a block structured address space, hardware supported dope vectors, hardware regulated pushdown stack, and timeindependent and PC-cognizant I/O channels.Asit turns out, variable size page virtual memory is a (nearly) free dividend of the dope vectors, so this is also included in the design along with several special instructions to help maintain storage.

The following paragraphs discuss these features and related topics.

#### 3.1 Pushdown Stack.

The hardware maintained pushdown stack is discussed first because it is basic to the evaluation of expressions and the block structured nature of the machine as a whole.

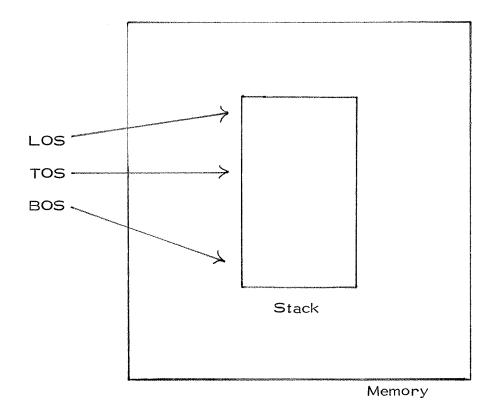

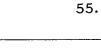

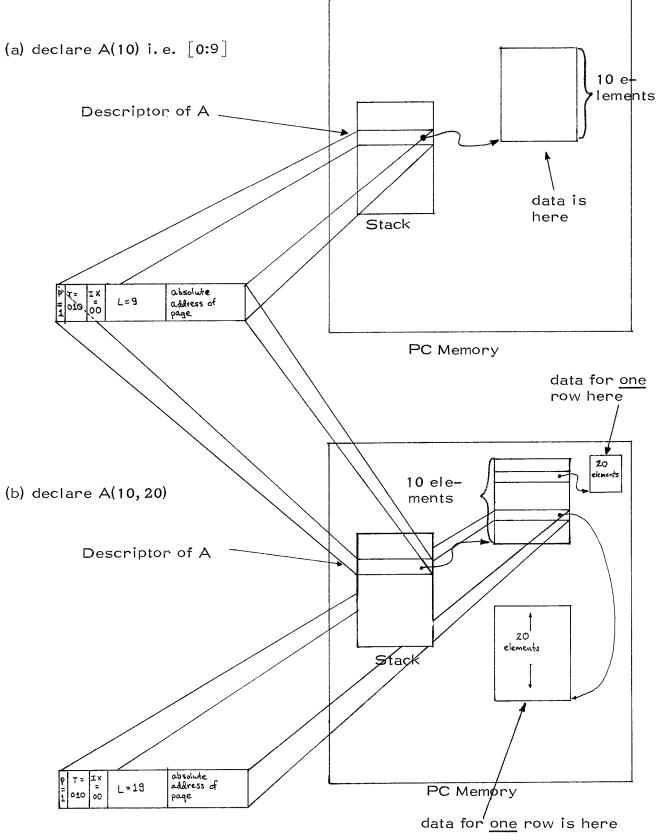

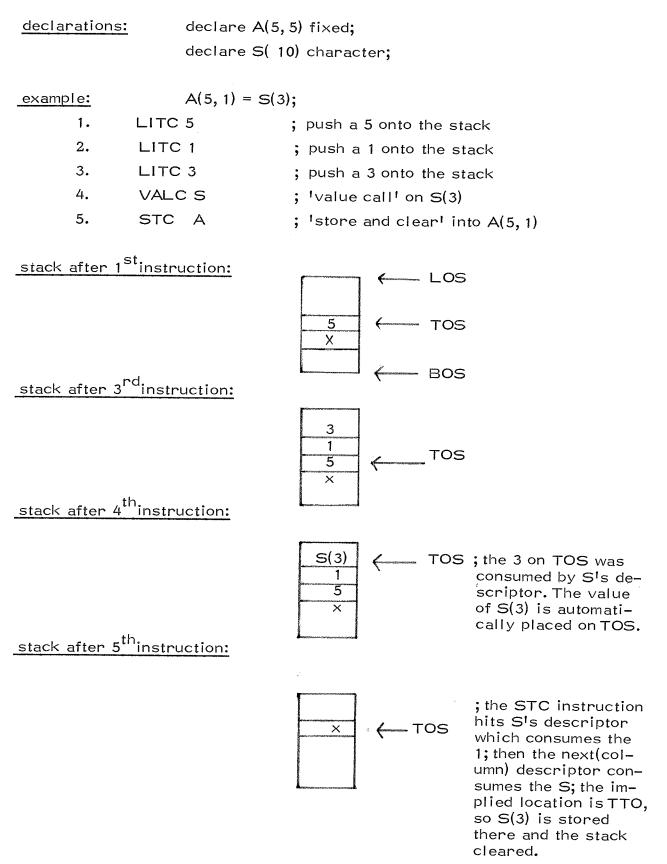

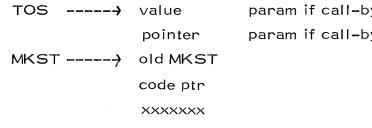

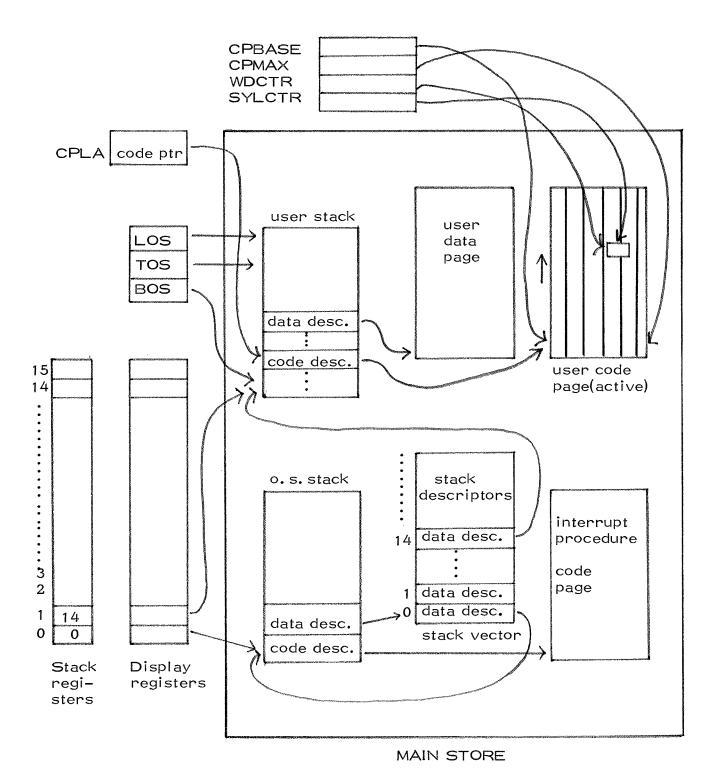

A pushdown stack can be implemented most easily in hardware with the stack itself residing in main store (hereinafter referred to as 'memory'), and the controlling registers in a fast store. Each element of the stack is one machine word; the limits of the stack are maintained in two registers called BOS (base of stack) and LOS (limit of stack); the address of the word currently on the 'top' of the stack is contained in TOS (top of stack). Normally, TOS is in the range BOS  $\leq$  TOS  $\leq$  LOS; stack underflow occurs when TOS becomes less than BOS, and stack overflow when TOS exceeds LOS. When an item is to be pushed onto the stack, TOS is incremented and checked against LOS, and then the item placed in the memory location pointed at by TOS. An item is removed (popped) from the stack by decrementing TOS and checking against BOS. Figure 3.1-1 illustrates.

A load-type instruction causes an item to be pushed onto the stack, while a store-type instruction causes an item to be popped off the stack and stored elsewhere in memory. Binary operations e.g. ADD, LESS THAN, cause the two topmost operands to be manipulated and the result placed on the stack i.e. as if the operation had performed POP, POP, PUSH.

The stack maintenance hardware assures that operands are always available to operations, and that TOS never violates the bounds of BOS and LOS.

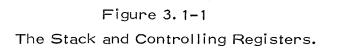

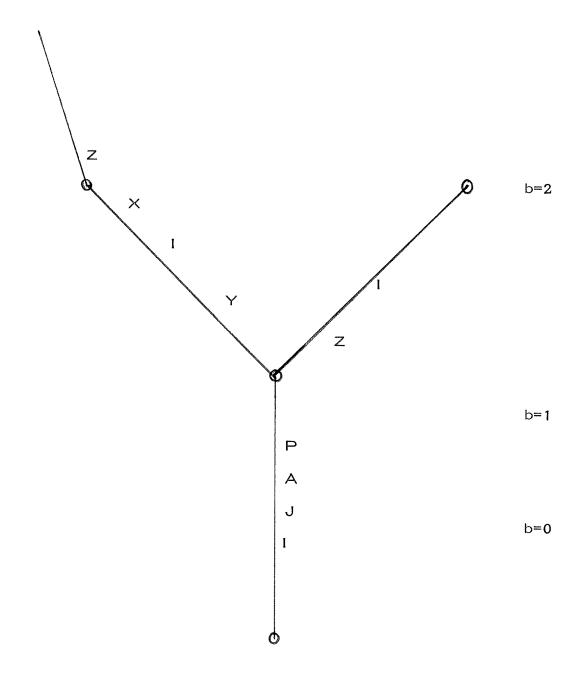

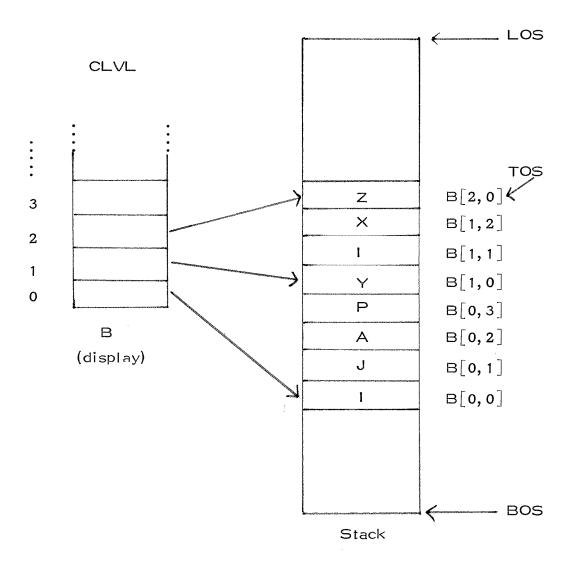

Also associated with the stack are the B or display registers, which are used to maintain the block/task structure of the running program. These registers point into the stack at those points where the storage for particular blocks are located, and are numbered 0, 1, 2, ....; the register CLVL denotes the maximal B[i] currently in use. Figure 3. 1-2 illustrates and the next paragraph explains their use further.

Figure 3.1–2 Stack with B/Display Registers

#### 3.2 Block Structured Addressing.

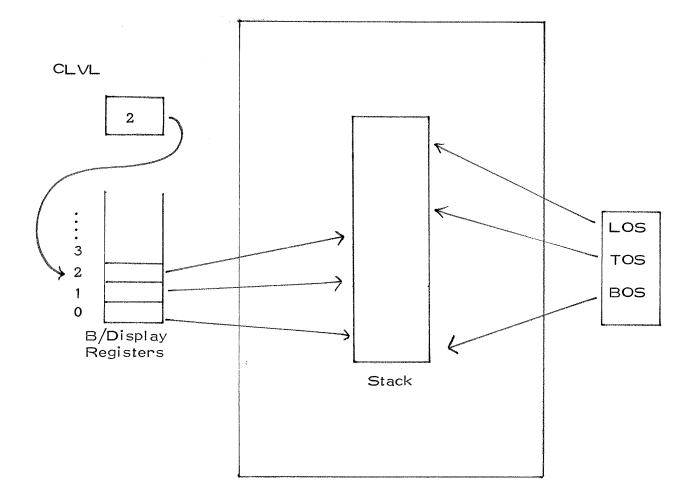

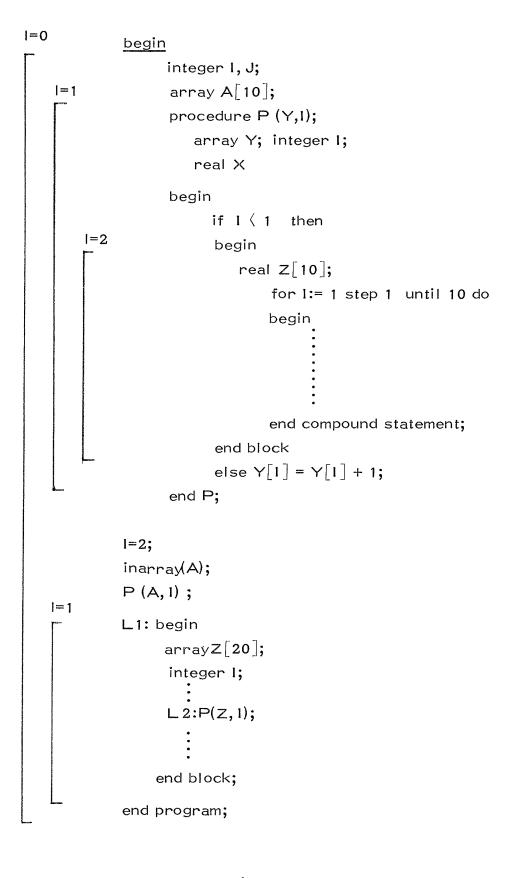

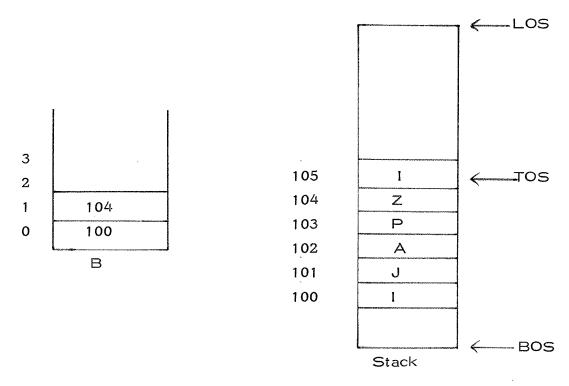

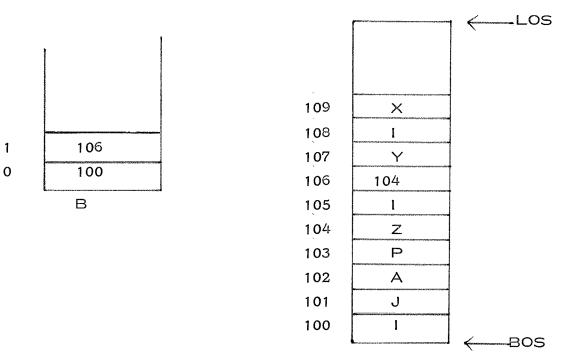

Figure 3.2-1 shows a simple Algol 60 program. Note that the various block have been dilineated and their nesting level labeled. We can now label the variables according to this nesting level e.g. I is in the first (b=0) block level, and is the first (d=0) variable therein decalred. Thus I is denoted [0,0]. Similarly, J is denoted [0,1]; A is [0,2]; and P is [0,3]. The bracketed pairs [b,d] are called address couples [R1], and Figure 3.2-2 lists the address couples for the entire program. Observe that there are three I's in the program (11, 16, 110), and that 16 and 110 both have the same denotation [1, 1]. This lack of uniqueness poses no problems however if we remember that one cannot simultaneously 'be! in two block on the same level, according to the definition of Algol. Thus within the definition of block structure, our [b,d] notation provides us with a method of uniquely addressing all variables, and furthermore, this method of addressing has the property that it reflects the source program natation within the variable's address, a valuable debugging tool.

Another way to view address couples is as addresses in a tree. Figure 3.2-3 illustrates this point af view.

The problem now facing us is how to map our tree space addresses into the linear address space found in computer memories. The mechanism by which this is accomplished utilizes the B-registers mentioned in the preceding section. An address couple [b,d] is mapped into an absolute linear address 'a' via the B registers by the algorithm:

$$a := B[b] + d.$$

Hence, so long as the address in B[b] is the address in the stack where the variable of block (nesting level) 'b' begins, this mapping preserves the intent of the source program. We can observe that the B registers are really nothing more than index registers, and thus the price paid for having block structured addressing is that all memory references

Figure 3.2-1 Block Structure of a Simple Algol 60 Program called SIMPLE.

|     | variable | block level | block displacement | address couple |

|-----|----------|-------------|--------------------|----------------|

| 1.  | I        | 0           | 0                  | [0,0]          |

| 2.  | J        | 0           | 1                  | [0,1]          |

| 3.  | А        | 0           | 2                  | [0,2]          |

| 4.  | Р        | 0           | 3                  | [0,3]          |

| 5.  | Y        | 1           | 0                  | [1,0]          |

| 6.  | I        | 1           | 1                  | [1,1]          |

| 7.  | ×        | 1           | 2                  | [1,2]          |

| 8.  | Z        | 2           | 0                  | [2,0]          |

| 9.  | Z        | 1           | 0                  | [1,0]          |

| 10. | 1        | 1           | 1                  | [1,1]          |

Figure 3.2-2 Address Couples for Program SIMPLE.

Figure 3.2-3 Address Couples as Tree Addresses (Program SIMPLE).

43.

require indexing. Figure 3. 2-4 illustrates how this addressing scheme is applied.

The next question which arises is how many B-registers should there be? At first glance one might think that an infinite number are necessary if recursion is allowed, but this is not true since a recursive procedure always executes at the block level at which it was declared ( thus causing the same B[i] to be continuously updated ). The only real requirement on the number of B's is whatever one considers to be a 'reasonable' maximum for block/task <u>nesting</u>. Clearly 8 is too few and 64 more than necessary, and therefore either 16 or 32 is probably a reasonable number.

Having decided on the number of B registers, we now must fix upon the maximum displacement (i.e. the maximum number of declarations at a given block level). It is necessary to choose a maximum because the [b,d] will be the address field of the PC's (single address) instructions. Employing logic similar to the above, 64 is probably too few, and 1024 too many. Thus we will choose among 128, 256, and 512. This decision has distinct impact on the System since the outermost block contains the declarations of all the system library routines and utilities. In effect, too small a d-field restricts the total number of 'externals' that can exist. There is, however, another approach to these field calculations, described in [W3, W4].

Two primitive operations are required to maintain the B registers: enter block (NTRB), and exit block (XITB). Figure 3.2-5 gives the function which each must perform. The attentive reader will note that upon entering a block, the contents of the associated B-register are pushed onto the stack. This is done, though it may at first seem unnecessary, because execution may be retracing the tree structure as the result of an outer block procedure call, and the hardware must save the register 'just in case'. [It is also crutial to realize that in the final machine, the contents of the B's cannot simply be pushed onto the stack ( as shown in Figure 3.2-5 ab ) because they contain absolute addresses, the bane of relocation. Hence they are converted to a relocatible form called [s,d] ( explained later ) and then pushed. ] XITB undoes the ef-

44.

Figure 3.2-4 Execution Snapshot of Program SIMPLE.

#### procedure enter;

#### begin

comment Interchange code page logical address and stack[f-1];