# A DESCRIPTION OF THE RIKKE 1 SYSTEM

by Jørgen Staunstrup

.

DAIMI PB-29 May 1974

| Institute of Mathematics University of Aarhus<br>DEPARTMENT OF COMPUTER SCIENCE<br>Ny Munkegade - 8000 Aarhus C - Denmark<br>Phone 06-128355 |  |

|----------------------------------------------------------------------------------------------------------------------------------------------|--|

|----------------------------------------------------------------------------------------------------------------------------------------------|--|

## Contents

|       |                                                                        | Page     |

|-------|------------------------------------------------------------------------|----------|

|       | Foreword                                                               | iii      |

| 1.0.  | Introduction                                                           | 1        |

| 1.1.  | Historical Notes                                                       | 1        |

| 1.2.  | General Design Criteria and Constraints                                | 2        |

| 2.0.  | The RIKKE 1 system                                                     | 5        |

| 2.1.  | The Register Group                                                     | 6        |

| 2.2.  | Counter A                                                              | 8        |

| 2.3.  | Bus Transport                                                          | 10       |

| 2.4.  | Working Registers<br>2.4.1. Microinstruction Format and a Few Examples | 12<br>14 |

| 2.5.  | The Bus Shifter                                                        | 19       |

| 2.6.  | Bus Masks                                                              | 24       |

| 2.7.  | Postshift Masks                                                        | 28       |

| 2.8.  | The Arithmetical and Logical Unit                                      | 35       |

| 2.9.  | The Local Registers                                                    | 38       |

| 2.10. | The Accumulator Shifter                                                | 40       |

| 2.11. | The Variable Width Shifter                                             | 46       |

| 2.12. | Double Shifter<br>2.12.1. Two examples using the shifters              | 48<br>50 |

| 2.13. | The Common Shifter Standard Group                                      | 54       |

| 2.14. | Loading Masks                                                          | 56       |

| 2.15. | The Parity Generator                                                   | 60       |

| 2.16. | The Bit Encoder                                                        | 60       |

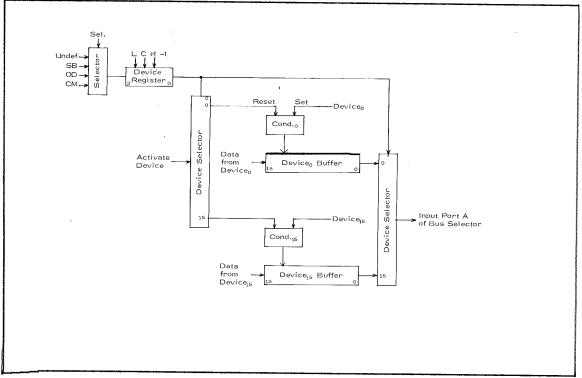

| 2.17.  | Input Ports                                                                                                                                                                                      | 61                         |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

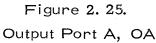

| 2.18.  | Output Ports                                                                                                                                                                                     | 64                         |

| 2.19.  | The Bus Structure                                                                                                                                                                                | 67                         |

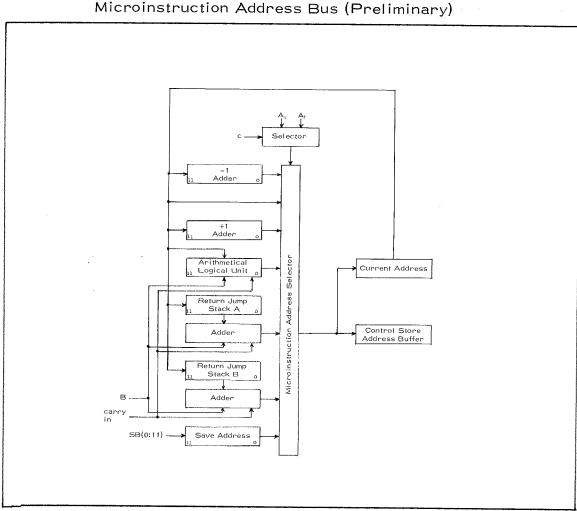

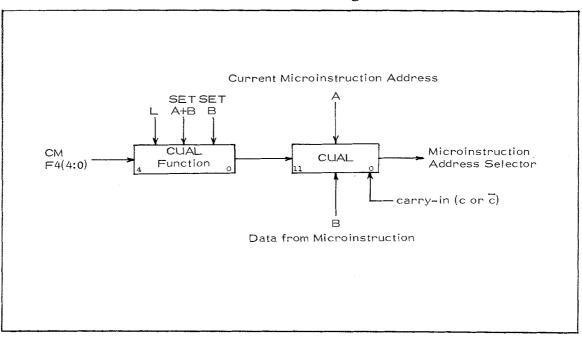

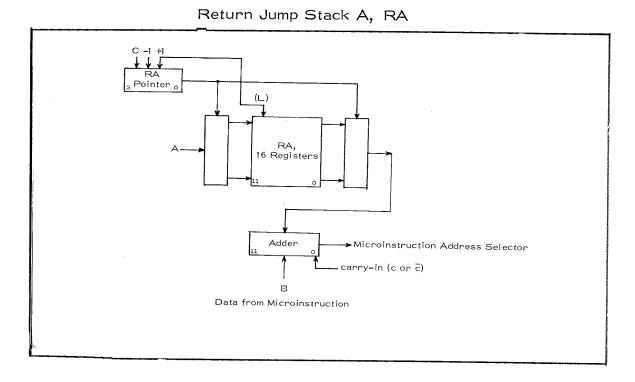

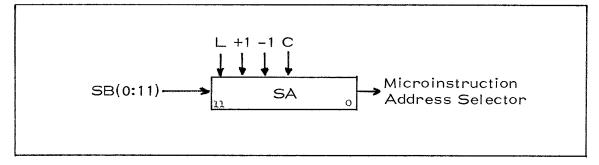

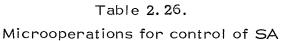

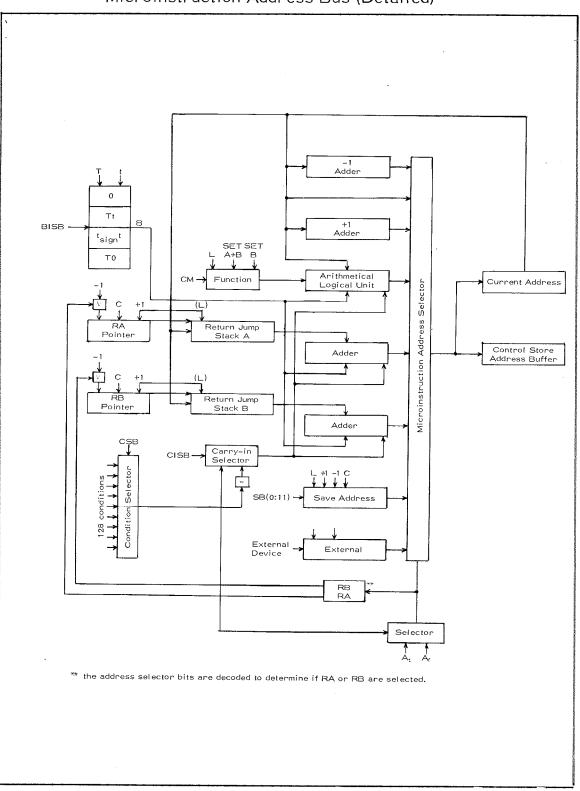

| 2. 20. | The Control Unit<br>2. 20. 1. Microinstruction Sequencing<br>2. 20. 2. The Control Unit Arithmetical Logical Unit<br>2. 20. 3. Return Jump Stacks A and B<br>2. 20. 4. The Save Address Register | 69<br>70<br>72<br>77<br>80 |

|        | 2. 20. 5. The Microinstruction Address Bus                                                                                                                                                       | 81                         |

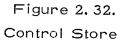

|        | 2.20.6. Control Store Loading                                                                                                                                                                    | 83                         |

| 2.21.  | Control Panel Switches KA and KB                                                                                                                                                                 | 84                         |

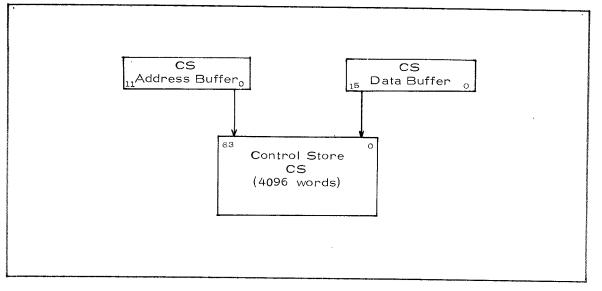

| 2.22.  | Internal Flags KC and KD                                                                                                                                                                         | 84                         |

| 2.23.  | The Conditions and Condition Selector                                                                                                                                                            | 86                         |

| 2.24.  | Short and Long Cycle                                                                                                                                                                             | 90                         |

| 2.25.  | The Real Time Clock                                                                                                                                                                              | 91                         |

| 2.26.  | Auxiliary Facilities<br>2.26.1. Counter B<br>2.26.2. Main Memory                                                                                                                                 | 92<br>92<br>93             |

| 2.27.  | An Alternate View of the Working Registers                                                                                                                                                       | 96                         |

| 2. 28. | An Alternate View of the Postshift Masks                                                                                                                                                         | 99                         |

| 3.0.   | Microinstruction Specification and Execution                                                                                                                                                     | 102                        |

| 3.1.   | Microinstruction Format                                                                                                                                                                          | 102                        |

| 3. 2.  | Microinstruction Execution<br>3.2.1. Example of how to use Clock Pulse 1                                                                                                                         | 110                        |

| 2 2    | and Clock Pulse 2                                                                                                                                                                                | 112                        |

| 3.3.   | Comprehensive Tables of Microoperations for<br>Individual Functional Units                                                                                                                       | 113                        |

|        | Tables of Microoperations                                                                                                                                                                        | 114                        |

|        | Table of First Occurrance of Abbreviations and Symbols                                                                                                                                           | 1 21                       |

|        | List of Figures                                                                                                                                                                                  | 125                        |

|        | List of Tables                                                                                                                                                                                   | 1 27                       |

|        | References                                                                                                                                                                                       | 129                        |

#### Foreword

It is the purpose of this document to give an introductory (yet reasonably detailed) description of the RIKKE 1 System. The bus structure, the registers and functional units attached to it, and the control which can be exercised on these components are discussed. The document is not a reference manual. Rather, it is written entirely from the pedagogical point of view, with the system described in a modular fashion. Examples are introduced after each component is added to the basic bus structure. The examples are written in the RIKKE 1 microassembly language (see [8]). The examples are deliberately kept simple so the reader will not spend time learning a complicated or clever algorithm but will learn the control mechanisms of the particular components involved. Thus, many of the examples are "contrived" and do not perform any particular components involved enhances the reader's understanding and underscores the overall simplicity and homogeneity of the structure and its components.

The present description is a modification of a similar one, describing another slightly different system called MATHILDA (DAIMI PB-13), written by Bruce D. Shriver.

For more detailed information the reader is referred to  $\lceil 9 \rceil$ .

## A Description of the RIKKE 1 System by Jørgen Staunstrup

#### 1.0. Introduction

RIKKE 1 is a dynamically microprogrammable processor which has been designed to be used as a tool in emulation-oriented and processor design research. For the sake of completeness we will discuss briefly a short history of the unit and then some of the criteria which served as a basis for its design.

#### 1.1. Historical Notes

In the spring of 1971 the Department of Computer Science of the University of Aarhus was considering the purchase of a standard minicomputer to act as a controller for a variety of peripherals and to simulate a medium speed batch terminal to the Computer Center's large system. A group of people were, at this time, working on the design of an integrated software and hardware description language called BPL [1]. To support this group and to make the use of such a minicomputer more flexible, it was decided to design and construct a microprogrammable minicomputer within the department itself.

The design was started and completed during the summer of 1971. The resulting machine, RIKKE 0 [2], was constructed and began running in early 1972. In the meantime a number of projects were proposed which were considered not to be compatible with that design. Among these were various projects in numerical analysis [3, 4] in which it was found that the word size and bus width of the RIKKE 0 (16 bit) was too short to obtain an efficient implementation of even standard arithmetic operations on numbers. It was then suggested that a microprogrammed functional unit with a wider data path and special features could be attached to

RIKKE 0 as an I/O device, or "functional unit", together with a wider memory, for use with these projects. A proposal was made to the Danish Research Council to obtain a grant to design and construct such a funcional unit. A grant was made i June 1972 in which funds were awarded for hardware and a memory (32K, 64 bit wide, 1.4  $\mu$ s access time). The manpower for the construction of the unit was, in part, granted by the Research Council; two staff engineers and one staff technician were provided by the Department. The design was started in May 1972 and completed during the summer of 1972. The construction of the resulting machine, MATHILDA, is due to be completed summer 1974.

The motivation for building the MATHILDA instead of purchasing a commercially available machine can be summarized as follows. First, there were ( as far as we knew ) no commercially available dynamically microprogrammable processors at the time we started our efforts which: (a) were in the price range we could afford, (b) were designed for or supported user written microcode or (c) offered a reasonable experimental and growth oriented structure. We felt that we had the in-house capability to design and construct the machine. The availability of LSI circuits and convenient mounting techniques and our experience with RIKKE 0 supported this view.

It was also decided that the new design for MATHILDE outdated the design of RIKKE 0, and with only minor modifications and additions could be used in the construction of a 16-bit machine, RIKKE 1, which is the subject of this description. Design criteria with respect to construction supported this view, these will be described in the next section.

#### 1.2. General Design Criteria and Constraints

The RIKKE-0 machine is intended to be a research oriented machine. Its main design criteria then, within the money and timing constraints on the project, was to provide a machine on which a large variety of experiments related to processor and emulator design and evaluation could be performed. We attempted to use the "top-down" design approach which quite frequently was tempered by the "forces from below", see Rosin [5]. Therefore, we tried to let various application-oriented and software ideas be reflected in the design.

Two general software concepts had a reasonable impact on design. The one being the ability to multiprogram virtual machines and the other being the concept that virtual machines would be defined through several layers, (e.g., R. Dorin [6]). The effect of these ideas is apparent in the design of the control unit, especially with respect to the capabilities of addressing. Many addressing features known on the virtual level are present here on the micro level.

Another criterion was to have a clean and consistent way of dealing with timing problems. We decided not to force the speed; rather we would have a slower machine than obtainable with the componentry at hand, and thus one, hopefully, with a reduced set of timing idiosyncrasies. It was also decided to be able to control all elements of the system from an immediate control or a residual control capability, or some combination of both. The residual control was made homogeneous to the user by having a reasonably "standard control register group" where ever such control was provided.

Another design criterion dealt with the actual construction of the unit. It had been decided, prior to the obtaining of the grant from the Danish Research Council, to construct additional RIKKE's by other funding. It became apparent, during the design phase of MATHILDA, that the machine would be reasonably complex and that several features of MATHILDA included or extended similar features on RIKKE 0. Because of the complexity of the design, the limited funds and manpower available, and the fact that we wished to design, construct, and test the machine within 1 year, it was decided that the additional RIKKE's (now called RIKKE 1's) should be modeled after the MATHILDA System. Thus, one design criterion was to ensure a modularity in the hardware design. This would enable an economy in print-lay out and construction to be achieved. As an example, the bus structure is laid out on one print board, 8-bits wide. Two of these boards, interconnected, comprise one RIKKE 1 bus structure with all registers, shifters, etc. Four of these RIKKE 1 boards, interconnected, give the MATHILDA bus structure. (For a description of the MATHILDA see Shriver [7]).

#### 2.0. The RIKKE 1 System

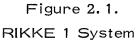

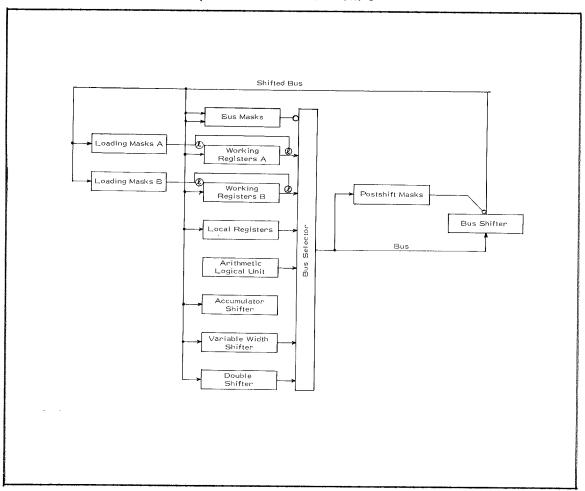

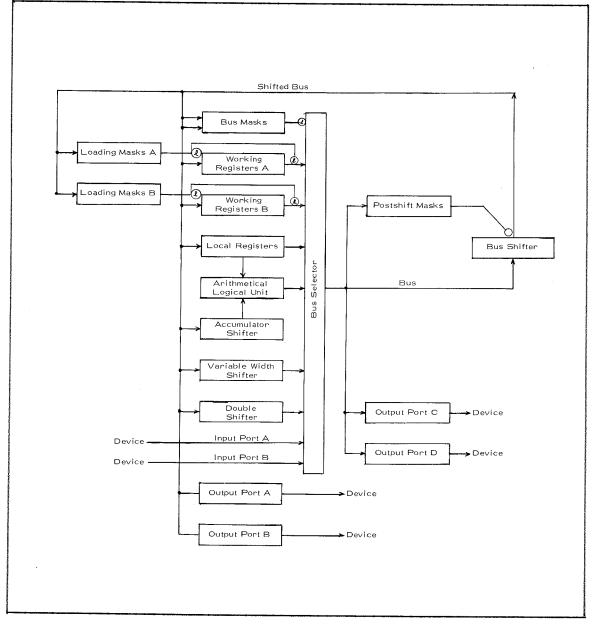

RIKKE 1, as has been stated earlier, is a microprogrammed controlled bus structure. The major elements of the system are shown in Figure 2.1. and are the:

- 1) bus structure.

- 2) control unit.

- 3) auxiliary facilities.

- 4) 1/0.

- 5) Memory.

In the following sections we will describe each of these systems independently and give examples of their utilization.

#### 2.1. The Register Group

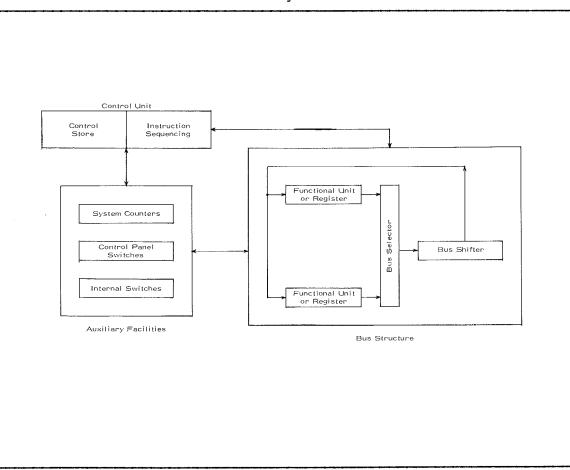

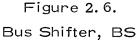

We begin by introducing a fundamental building block which is used in the various control mechanisms of the system, viz, a Register Group RG<sup>\*</sup>, as shown in Figure 2.2. A RG is a set of 16 or 256 registers. The width of the registers and the number of registers in a specific RG will be stated when it is introduced. The element of a particular RG, which is to be used as a source or destination for the transfer of information, is pointed to by the RG address register. This register is called the Register Group Pointer, RGP, as shown in Figure 2.2.

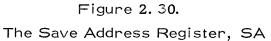

Figure 2.2. Typical Register Group

\*) After a particular system element is first introduced, an abbreviation for its name is given which, for the sake of brevity, is then used in the text; see the "Tables of First Occurrance of Abbreviations and Symbols", beginning on page 121, for the page of first occurrance. There are four microoperations associated with an RGP. They are marked L, +1, -1, and C in Figure 2.2. and all subsequent figures.

|    | Symbolic Notation   | Microoperation                       |

|----|---------------------|--------------------------------------|

| L  | RGP:=Pointer Source | Load the RGP from the Pointer Source |

| +1 | RGP + 1             | Increment RGP by 1                   |

| -1 | RGP - 1             | Decrement RGP by 1                   |

| С  | RGPC                | Clear (i.e., set to zero) RGP        |

Table 2.1. Microoperations for the control of an RG

The symbolic notation RGP + 1, RGP - 1, etc. is the notation which is used with our microassembler, and all of our examples will be shown using this notation. The abbreviation 'RG' will often be replaced by the abbreviation of the name of the functional unit with which that particular RG is associated. Not all of the RGP's will have the microoperation

## RGP:=Pointer Source

associated with them. For those RGP's which do have this microoperation it will be seen that the Pointer Source data itself can usually be selected to come from any of four different sources.

There is one additional microoperation required for the control of an RG; namely the function labelled "load" in Figure 2.2. If the loading of an RG can be initiated by a microoperation it will be indicated by an "L" on such a diagram.

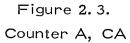

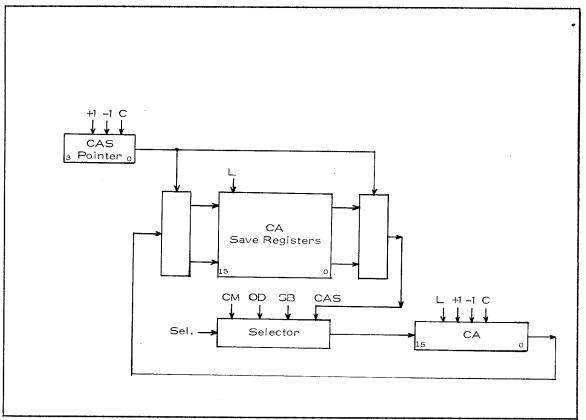

#### 2.2. Counter A

We will, from time to time, give small segments of microcode to illustrate the use of a device and its control. In order to make these examples clearer and also to give a more realistic view of how such a code is actually written we introduce the system counter, Counter A, CA. CA is a 16-bit wide counter as shown in Figure 2.3.

CA has four microoperations associated with it as shown in the box labelled 'CA' in this Figure. These microoperations are given in Table 2.2.

Table 2.2.

Microoperations for control of CA

|    | Symbolic Notation | Microoperation                                                                                                                        |  |

|----|-------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|

|    | CA:=CM OD SB CAS  | Load CA from either CM, OD, SB, or<br>CAS. Note the use of " " to mean "or"<br>in the symbolic notation for this micro-<br>operation. |  |

| +1 | CA + 1            | Increment CA by 1                                                                                                                     |  |

| -1 | CA – 1            | Decrement CA by 1                                                                                                                     |  |

| С  | CAC               | Clear (i.e., set to zero) CA                                                                                                          |  |

Both the box labelled "Selector" in Figure 2.3. and the explanation of the microoperation "L" in Table 2.2. state that CA can be loaded from one of four possible sources:

- 1) Immediate data within the Current Microinstruction, CM,

- A 16-bit Output Register, OD (discussed in Section 2. 18.),

- 3) Bits 0 through 15 of the Shifted Bus, SB (discussed in Section 2.5), and

- 4) From an element of a 16-bit wide, 16 element RG called the Counter A Save Registers, CAS.

Thus the microoperation

CA:=37

loads CA with the constant 37 from a data field within the CM. While the microoperation

## CA:=CAS

loads CA with the contents of the element of CAS which is pointed to by the CAS Pointer, CASP. Notice that the CAS can be loaded with the contents of CA thus allowing one to save the current value of CA. The four microoperations associated with the CAS and CASP are in Table 2.3.

| Tab | le | 2. | 3. |  |

|-----|----|----|----|--|

|-----|----|----|----|--|

Microoperations for control of CAS and CASP

|    | Symbolic Notation | Microoperation                                     |

|----|-------------------|----------------------------------------------------|

| L  | CAS:=CA           | Load the element of CAS pointed to by CASP with CA |

| +1 | CASP + 1          | Increment the CASP by 1                            |

| -1 | CASP - 1          | Decrement the CASP by 1                            |

| С  | CASPC             | Clear (i.e., set to zero) CASP                     |

We can test to see if CA contains zero. We will demonstrate the use of this condition and the microoperations in Tables 2.2. and 2.3. in sub-sequent examples.

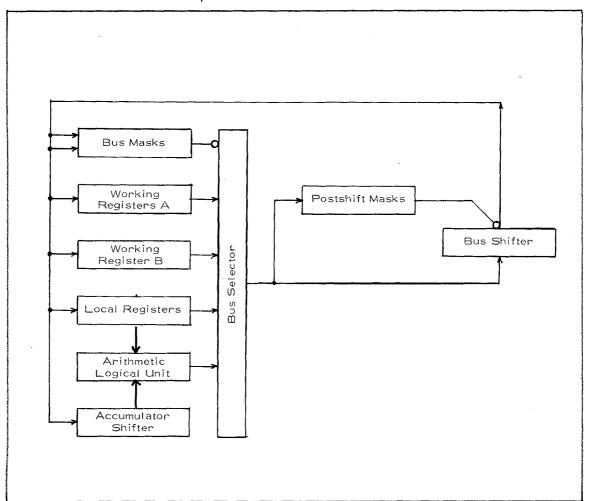

#### 2.3. Bus Transport

Having introduced some elementary notions we will now examine in some detail the bus structure, the registers and functional units attached to it, and the control which can be exercised on these components. We will construct the bus structure in a modular fashion – hopefully to enhance the reader's understanding and to underscore the overall simplicity and homogeneity of the structure and its components.

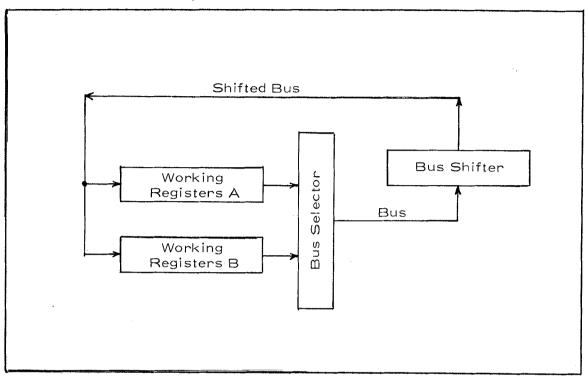

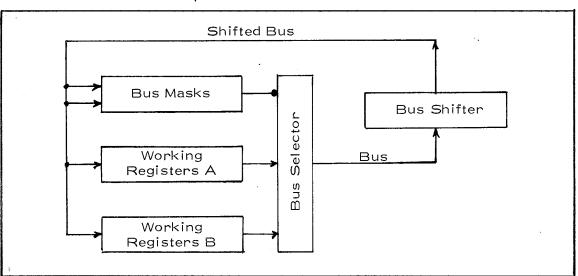

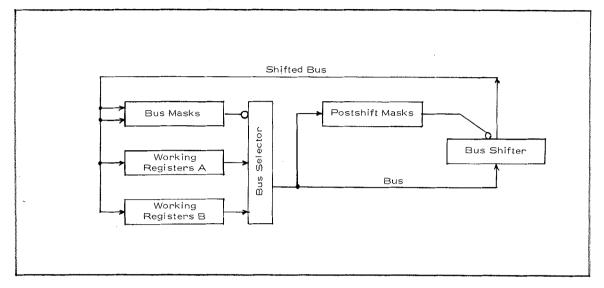

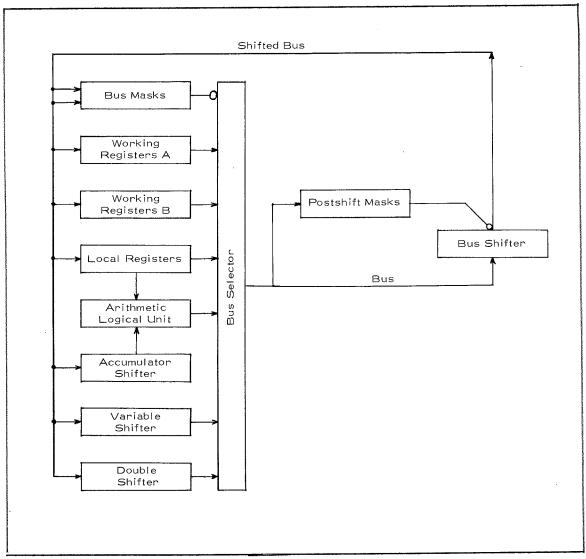

Let us introduce the concept of a bus transport by considering a subsystem of the bus structure consisting of the Working Registers A, WA, Working Registers B, WB, and the Bus Shifter, BS, as shown in Figure 2.4. The exact nature of WA, WB and BS is not important to us here.

Figure 2.4. Sub-system of the Bus Structure

The BUS is a 16-bit wide data path. The input to the BUS (its SOURCE) is obtained from a bus selector which has eight inputs, two of which are shown here. i.e., WA and WB. The particular input which is selected as the SOURCE for bus transport may be shifted a specified amount in the BS. The output of the BS, called the Shifted Bus, SB, can then be stored in at least one of seven possible 16-bit destinations (called Bus Destinations, BD, or DESTINATION). Two such BD's are shown in Figure 2.4. i.e., WA and WB. We will in this report specify bus transport information as we do in our microassembler, viz,

DESTINATION:=SOURCE, BS Specification.

If the BS Specification field is empty, i.e., the BS is not to be used (no shift occurs) then the bus transport is given by

DESTINATION:=SOURCE.

As an example, the bus transport WB:=WA has the obvious meaning of a register to register transfer from WA to WB. If a SOURCE is chosen to be transported but not stored in any of the BD's, the bus transport information is written

2

SOURCE, BS Specification

or

#### SOURCE

as is appropriate. The SOURCE may be stored in destinations other than BD's during a bus transport. We will learn what functional units or registers can serve as these "other destinations" as this report develops. If the SOURCE is to be stored in more than one destination, the DESTINATION portion of the bus transport specification is written as a list of destinations separated by commas, i.e.,

LIST:=SOURCE, BS Specification

or

```

LIST:=SOURCE

```

where

$LIST::=d_1$ , ...,  $d_n$ .

The value of n and the units which can serve as destinations,  $d_1$ , will be discussed later.

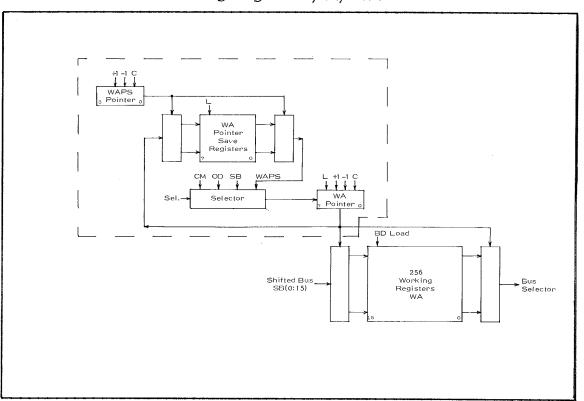

#### 2.4. Working Registers

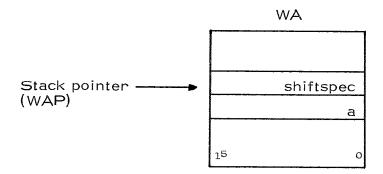

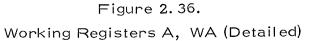

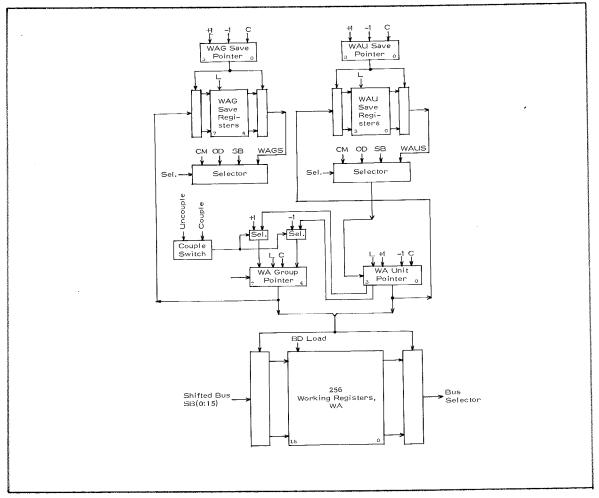

WA and WB, introduced in the previous section, are not single registers but each is a 16-bit wide, 256 element RG. Figure 2.5. shows WA; WB, not shown, is identical.

The first thing we wish to point out in this figure is that the WA Pointer, WAP, is a mechanism identical to CA except that it is 8-bit wide and not 16-bit wide. (Note the dashed-line box in Figure 2.5.). Therefore, WAP not only points to which element of WA can be used as a SOURCE for bus transport (or used as a BD), but also can be stored in an RG

called the WAP Save registers, WAPS. This is identical to CA being saved. Also, as indicated in the box labelled "Selector" in Figure 2.5. the WAP can be loaded from any of four sources:

- 1) immediate data from the CM

- 2) the least significant 8-bits from OD \*)

- 3) the least significant 8-bits of the SB, \*) and

- 4) an element of WAPS.

This is identical to the loading of CA. Thus the microoperations WAP:= 37 and WAP:=WAPS have well defined analogous meanings.

The WA (and WB) registers are not loaded by a microoperation but rather as a result of being chosen as a BD in a bus transport specification; thus the loading of these registers is shown by the function "BD Load" on Figure 2.5. This notation will be used in all subsequent drawings.

<sup>\*)</sup> WB is different with respect to 2) and 3) in the sense that loading of WBP takes place from the most significant 8-bits of OD and SB.

There are 8 microoperations shown in Figure 2.5. associated with the use of WA. These are listed along with the corresponding microoperations for WB in symbolic form in Table 2.4. The actual microoperation descriptions can be extracted from the previous tables and are not repeated here.

| ,                        |                                                          |

|--------------------------|----------------------------------------------------------|

| WAP:=CM OD -7 SB -7 WAPS | WBP:=CM   OD <sub>8-15</sub>   SB <sub>8-15</sub>   WBPS |

| WAP + 1                  | WBP + 1                                                  |

| WAP - 1                  | WBP - 1                                                  |

| WAPC                     | WBPC                                                     |

| WAPS:=WAP                | WBPS:=WBP                                                |

| WAPSP + 1                | WBPSP + 1                                                |

| WAPSP - 1                | WBPSP - 1                                                |

| WAPSPC                   | WBPSPC                                                   |

## Table 2.4. Microoperations for control of WA and WB

## 2.4.1. Microinstruction Format and a Few Examples

In order to present a few examples we will introduce the microinstruction format which we use in our microassembler. The format of a microinstruction is:

"A: bus transport; microoperations and data; microinstruction sequencing.",

where

- a) "A" is a symbolic name for the address of the microinstruction,

- b) "Bus transport" is a field giving the bus transport information as explained previously in Section 2.3.,

- c) "microoperations and data" is a field of up to 7 microoperations and immediate data to be executed or used during this microinstruction (the exact combination of microinstructions and data which can be included in this field and precise details of the timing of microoperations are given in Section 3.0.).

- d) "microinstruction sequencing" information will be written in the form

if c then  $A_t$  else  $A_f$

which is to mean: if a particular selected condition c is true then choose address  $A_{\rm t}\,$  as the address of the next microinstruction else choose  $A_{\rm f}\,$  .

It is not necessary or appropriate at this point to list all of the conditions which are testable by the system nor how  $A_t$  and  $A_f$  are functions of the address of the current microinstruction, A. These matters will be dealt with in Section 2. 20. 1. However, conditions and address functions will be introduced as needed for examples. If no condition is to be considered, i.e., if  $A_t = A_f$ , the sequencing information will merely be written  $A_t$  (and not "if c then A else A " where c is an arbitrary condition).

Thus, the microinstruction labelled A,

A: WA:=WB; WBP + 1; A + 1.

means: load the element of WA pointed to by WAP from the element of WB which is pointed to by WBP without shifting it during the bus transport; Then increment WBP by 1; then obtain the next microinstruction from A + 1. The action associated with <u>every</u> microoperation specified in a microinstruction is completed <u>before</u> the next microinstruction is executed. For example, in the above microinstruction if WBP had been set to 9 before the beginning of the execution of this instruction, then WB9 would be the SOURCE for the bus transport. At the end of execution of the instruction, the WBP would be set to 10. If, in the next microinstruction were again selected as the SOURCE, then the contents of WB10 would be gated onto the BUS. In order to give an example of a microinstruction using conditional branching, we establish the following convention for the testing of conditions which will be used in all of our examples (unless stated explicitly otherwise): <u>all</u> conditions which arise as a result of bus transport and microoperation execution specified by a particular microinstruction, M, are testable in the <u>next</u> microinstruction to be executed after M is executed. This means that all the conditions available or changed during the execution of microinstruction M are "saved". These "saved" conditions are those tested in the next instruction to be executed. Therefore, our microinstruction can be thought of being executed in the following sequential way:

- (a) save the conditions of the previous microinstruction

- (b) execute bus transport

- (c) execute microoperations

- (d) execute microinstruction sequencing based on saved conditions.

Let us introduce the notation that bit 15 of the WA input to the bus selector is testable, that is, bit 15 of the element of WA which is pointed to by WAP. If we wish, for example, to test bit 15 of WA7, and if it is set to 1, jump to the microinstruction labelled BITON, else continue with the next microinstruction, we could write,

> A-1: ; WAP:=7 A : ; if WA(15) then BITON else A+1 A+1:

We could not write

A : ; WAP:=7; if WA(15) then BITON else A+1,

according to our current convention. It is possible to conditionally repeat the same instruction. Let us give an example of this. Assume there is at least one register in WA which contains bit 15 set to 1, the following four microinstructions will: search WA starting with register 0 and transfer the first register of WA encountered with bit 15 set to 1 to register 0 of WB; then, store the address of the WA register which was transferred in register 0 of WAPS; and then continue with the next microinstruction.

; WAPC, WAPSPC, WBPC. LOOP: ; WAP + 1; if WA(15) then SAVE else LOOP. SAVE: ; WAP - 1. WB:=WA ; WAPS:=WAP.

We have introduced some standard defaults in this example:

- a) If the bus transport field is empty it means that an unspecified source is selected for bus transport but is not stored anywhere.

- b) If the microoperations field is empty it means that no microoperations are to be exectuted during this particular microinstruction.

- c) An empty microinstruction sequencing field implies the next microinstruction to be executed is that in A + 1 if the address of the current microinstruction is A. If you wish to use comments these must start with "." (period).

- d) Any instruction sequence shown is assumed to be located sequentially in control store and the symbolic address name is used only when needed in the microinstruction sequencing field of some other instruction.

- e) The symbol will be used to indicate the end of the group of microinstructions in the example.

The symbolic names HERE-1, HERE, and HERE+1 are used often in the microinstruction sequencing field to mean A-1, A, and A+1 assuming the address of the current microinstruction is A. As an example, the instruction labelled LOOP above could have been written

; WAP+1; if WA(15) then HERE+1 else HERE.

Through the use of CA the assumption that at least one register of WA contains bit 15 set to 1 is not required. CA can be used to control the number of elements of WA we will search. If we establish a routine labelled NONE which handles the situation when no element of WA contains bit 15 set to 1, then the code to perform the same task as related above is,

```

; WAPC, WAPSC, WBPC.

; CA:=255; TEST.

; WAP+1, CA-1; if CA then NONE else HERE + 1.

TEST:; if WA(15) then HERE+1 else HERE-1.

WB:=WA; WAPS:=WAP. ■

```

The final example in this section uses the capability of loading CA from the SB. In the previous example CA was loaded with N-1 where  $N(2 \le N \le 256)$  is the number of registers of WA to be searched. Let us suppose that this number is in register 0 of WB and furthermore that you wish to save it in register 0 of CAS because it may be written over if a transfer is made to WB. A possible code segment is,

If the  $A_t$  address is HERE+1 we will only write, from now on, if c then  $A_t$ . Thus, the fourth instruction of the above example would be written

; WAP+1; if CA then NONE.

### 2.5. The Bus Shifter

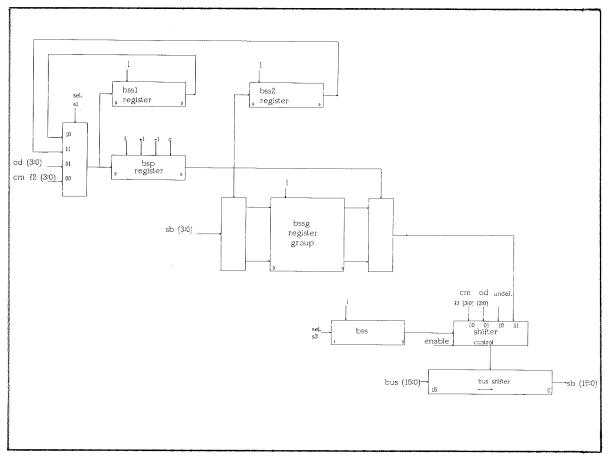

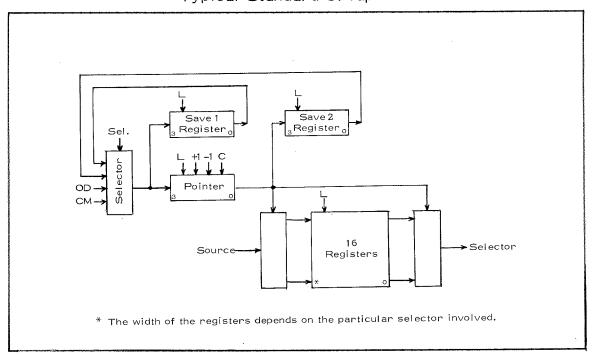

The Bus Shifter, BS, introduced in Figure 2.4. and shown in more detail in Figure 2.6. is a 16-bit wide right cyclic shifter which can be set to shift n bits,  $0 \le n \le 15$ . There exists a dedicated bit in each microinstruction to control the BS which indicates whether or not the BS should be used (enabled) during the current bus transport. If the BS is not enabled, no shift will occur.

If we wish to use the BS, the amount of shift can be selected from one of three possible sources as shown in the box labelled "Shift Control" in Figure 2.6., i.e., from

- 1) a data field in the CM,

- 2) the least significant 4 bits of the OD register,

- 3) an element of a 4-bit wide 16 element RG called the BSSG.

Which of these four sources is used is determined by BSS. This is loaded from CM S3(0:1). By default BSS:=CM, and you are advised to reset the BSS if you change it. The bus transport specification

WA:=WB

means: take the element of WB pointed to by the WBP and store it in the element of WA pointed to by the WAP without shifting is. While the bus transport specification

means: take the element of WB pointed to by the WBP, shift it 3 bits right cyclic and then store it in the element of WA pointed to by WAP, assuming that the BSS is set to select CM as the datasource. This will be assumed to be the standard setting of BSS in the following.

A 16-bit left cyclic shifter and a 16-bit right cyclic shifter are related by the expression

$$lcs = 16 - rcs$$

where

Ics is the amount of left cyclic shift and rcs is the amount of right cyclic shift.

We can therefore write as a notational convenience

WB:=WA, ← 5

to mean the same thing as

thus using  $\leftarrow$  (left shift) or  $\rightarrow$  (right shift) whichever makes the understanding of the processing clearer. The microassembler will do the proper computation and insert the correct amount for right shifting in the datafield.

The BS specification in the bus transport field of the microinstruction is given by

{→} CM OD BSSG

The BSS-selector chooses from which source the shifter-control data is to be taken, whether or not you indicate the source in the actual micro-instruction.You can load BSS by the microoperation BSS:=CM|OD |BSSG.

Having seen how the BS is controlled and how we specify this control, let us turn our attention to the BS register group Pointer, BSP. We see in Figure 2.6. that the data which can be loaded into the BSP can also be loaded into an additional register called the BS Save1 register, BSS1. If, for example, we know in advance the address of a particular register in the BSSG, which we will want to use as shift data (e.g., some highly used shift constant), we can store this pointer in BSS1 by loading BSS1 from the CM,

BSS1:=CM.

Whenever we wish to use this stored pointer we can load it into the BSP by executing

## BSP:=BSS1.

Now notice in Figure 2.6. that the BSP not only points to the element of the BSSG which can be chosen as data for the shift control unit, but also can be stored in a register called the BS Save2 register, BSS2. Suppose we are pointing at a particular element of the BSSG for the current shift control data and in the next microinstruction we wish to have register 9 of the BSSG to be used as shift data, <u>but</u> we do not wish to loose the pointer to our current control data. The following microinstruction achieves this,

and the off

#### ; BSS2:=BSP, BSP:=9.

Thus at some later time if we execute

#### BSP:=BSS2

the pointer information which had been saved in BSS2 would be restored.

A 16 element RG with the two Save registers and Pointer as shown in Figure 2.7. is a fundamental control element in the system and will be used with many devices in the subsequent sections. It will be referred to as a Standard Group (SG) and will be noted on drawings as such, i.e., it will not be explicitly be drawn out each time as it was in Figure 2.6. Each SG will, however, be given a name closely associated with the particular functional unit to which it is connected as, for example, in the current discussion the SG associated with the BS is called the BSSG.

Figure 2.7. Typical Standard Group

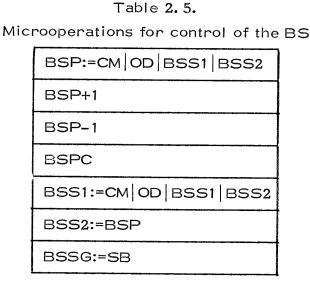

Table 2.5, below, lists the seven microoperations associated with the BS in their symbolic form; their meanings should be obvious from previous tables and the text. Note that the BSSG is loaded with the least significant 4 bits of the SB i.e., SB(0:3).

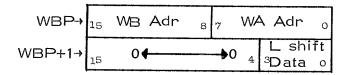

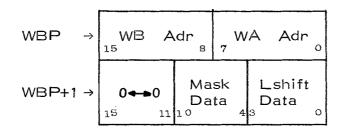

Let us assume the following information to be in WBP and WBP+1:

We wish to take a given WB register (WB Adr), shift it a given amount (L Shift Data), and store it in a given WA register (WA Adr).

The following code will: Load the BSSG with the L shift Data, Save the current WBP, load WBP with the WB Adr, Load WAP with the WA Adr, transfer the WB register pointed to by WB Adr to the register pointed to by WA-adr shifting it left cyclic by the amount L shift Data during transport, restore the old WBP, and then continue.

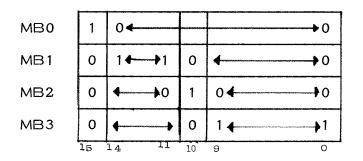

#### 2.6. Bus Masks

Let us now expand the initial bus structure given in Figure 2.4. by adding the Bus Masks, BM, as shown in Figure 2.8.

Figure 2.8. Expanded Bus Structure

The SOURCE is masked during <u>every</u> bus transport by the mask which is specified to be

where

- MA = an element of a 16-bit wide, 16 element RG called the Mask A registers,

MB = an element of a 16-bit wide, 16 element RG called the Mask B registers,

- v = logical "inclusive or".

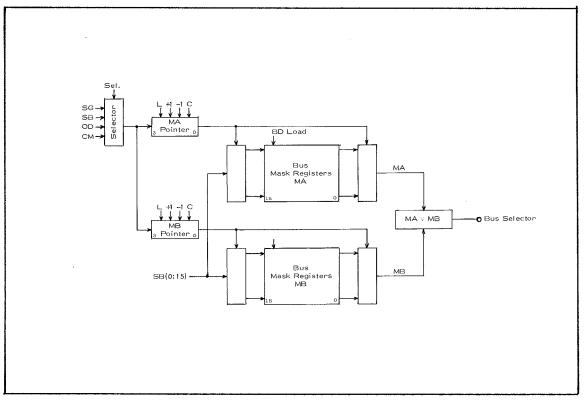

MA and MB are shown in Figure 2.9. Upon dead start, the system is

Figure 2.9. Bus Masks, MA and MB

such that the "no mask", i.e., 15 I's, is in register 0 of MA and the "bus clear mask", i.e., 16 0's, is in register 1 of MA. We will assume this to be the case throughout normal operation of the system. One can then look upon the pointer MAP as a switch for the use of the bus masks: If MAP = 0 then the BUS is not masked, if MAP = 1 then the BUS is masked by the mask specified by MB. This is, of cource, not the only interpretation of the use of the BM but it is a convenient one and one which we will normally employ unless otherwise stated.

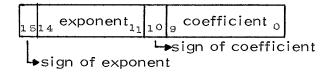

As an example, with no sensible applications, assume we are representing very small floating point numbers in the following sign magnitude format,

Suppose the following 4 masks are available in the first 4 registers of MB.

The following code will decompose a floating point number found in the register of WA pointed to by WAP and store the information as follows,

- 1) sign of the exponent in bit 15 of WB0

- 2) magnitude of the exponent in WB1(15:12)

- 3) sign of coefficient in bit 15 of WB2

- 4) magnitude of the coefficient in WB3(15:6)

It is suggested by this example that when one is decomposing formatted information (e.g., a virtual machine instruction) one may wish to coordinate the use of the BS with the use of the BM. Let us therefore suppose the shift constants 0, 15, 11, and 10 to be stored in the first 4 registers of the BSSG. The above decomposition and storage could be written as the following 3 microoperations:

The MA Pointer (MAP) and the MB Pointer (MBP) both of which were used in the above examples are loadable either separately or together; thus we can execute the microoperations

$$\begin{split} \mathsf{MAP:=CM} & | \ \mathsf{OD} | \ \mathsf{SB} | \ \mathsf{SG}, \\ \mathsf{MBP:=CM} | \ \mathsf{OD} | \ \mathsf{SB} | \ \mathsf{SG}, \ \mathsf{or} \\ \mathsf{MAP}, \ \mathsf{MBP:=CM} | \ \mathsf{OD} | \ \mathsf{SB} | \ \mathsf{SG} \ . \end{split}$$

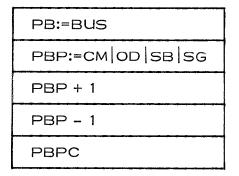

The name of the SG associated with the BM is the Bus Mask Pointer (BMP) Standard Group. The following table lists the microoperations associated with MA, MB, and BMP.

| Microoperations for control of the BM |                  |  |

|---------------------------------------|------------------|--|

|                                       |                  |  |

| MAP+1                                 | MBP+1            |  |

| MAP-1                                 | MBP-1            |  |

| MAPC                                  | MBPC             |  |

| MAP:=CM OD SB SG N                    | MBP:=CM OD SB SG |  |

| MAP, MBP:=CM   OD   SB   SG           |                  |  |

| BMP:=SB                               |                  |  |

| BMPP:=CM OD BM                        | 1PS1 BMPS2       |  |

| BMPP+1                                |                  |  |

| BMPP-1                                |                  |  |

| BMPPC                                 |                  |  |

| BMPS1:=CM OD B                        | MPS1 BMPS2       |  |

| BMPS2:=BMPP                           |                  |  |

|                                       |                  |  |

Table 2.6. Microoperations for control of the BM

## 2.7. Postshift Masks

The Bus Masks, as described in the previous section, are applied to the SOURCE as it is gated onto the BUS and thus before the SOURCE is shifted in the BS. There is also a possibility of masking the SOURCE after it has been shifted by using the Postshift Masks, PM, as shown in Figure 2.10.

Figure 2.10. Expanded Bus Structure

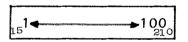

One of the purposes of the PM is to apply a mask to the output of the BS which will mask off the unwanted "cyclic" bits and replace them with 0's thereby simulating a logical shift. As an example, if the bus transport

is executed with the postshift mask

applied to the output of the BS, then we have taken a WA register, shifted it 2 bits left logical, and stored it in a WB register. Similarly, the bus transport

WB:=WA,

$$\rightarrow 6$$

with the mask

applied to the output of the BS means a WA register is shifted 6 bits right logical and then stored in a WB register. The output of the BS is masked during <u>every</u> bus transport by the mask which is specified to be

$$PA \lor PG$$

where,

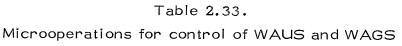

- PA = an element of a 16 bit wide, 16 element RG called the Postshift Mask A registers,

- PG = a functional unit called the Postshift mask Generator,

- v = logical "inclusive or".

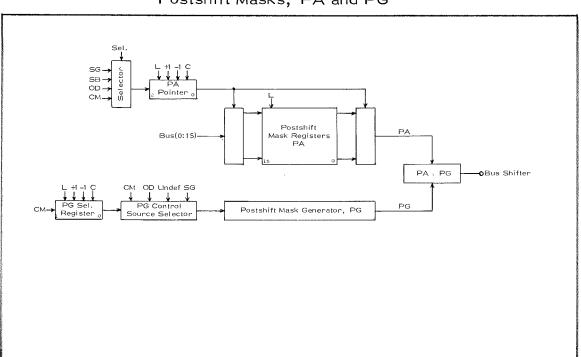

PA and PG are shown in Figure 2.11. This is quite similar to the BM where PG now takes the place of MB.

WARNING!!! As with the BM, when PA is loaded from the bus, it is the inverted bus which is loaded.

Figure 2.11. Postshift Masks, PA and PG

The PG is a 32 word ROM which can be addressed through PGS. The contents of the ROM is

## Table 2.7.

| Table representing | the READ-ONLY-MEMORY |

|--------------------|----------------------|

| containing the     | 32 Masks for the PG  |

| T                                                            |                                  |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | - I                        |

|--------------------------------------------------------------|----------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| I PG-DATA<br>I DEC BINARY                                    | Ī<br>I                           |                                                      | ECTED IN<br>MASK GENERATOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $\vec{I}$ $1 \le n \le 15$ |

| I 0 I 00000<br>I 1 I 00001                                   | I 1 1<br>I 0 1                   | 1 1 1 1 1                                            | 1 1 1 1 1 1 1 1 1<br>1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -I<br>I PG→0, PG+0<br>I)   |

| I 2 I 00010<br>I 3 I 00011<br>I 4 I 00100                    | I 0 0<br>I 0 0<br>I 0 0          | 0 1 1 1 1                                            | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | I<br>I<br>I                |

| I 5 I 00101<br>I 6 I 00110<br>I 7 I 00111                    | I 0 0<br>I 0 0<br>I 0 0          | $0 \ 0 \ 0 \ 0 \ 1$                                  | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            |

| I 8 I 01000<br>I 9 I 01001<br>I 10 I 01010                   | I 0 0<br>I 0 0<br>I 0 0          | 0 0 0 0 0                                            | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | I<br>I<br>I                |

| I 11 I 01011<br>I 12 I 01100<br>I 13 I 01101                 | I 0 0<br>I 0 0<br>I 0 0          | 0 0 0 0 0<br>0 0 0 0 0<br>0 0 0 0 0                  | 0 0 0 0 1 1 1 1 1<br>0 0 0 0 0 0 1 1 1 1 1<br>0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | I<br>I<br>I                |

| I 14 I 01110<br>I 15 I 01111<br>I 16 I 10000                 | I 0 0<br>I 0 0<br>I 0 0          | 0 0 0 0 0<br>0 0 0 0 0<br>0 0 0 0 0                  | 0 0 0 0 0 0 0 0 1 1<br>0 0 0 0 0 0 0 0 0 1<br>0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | I<br>I<br>I PG→16, PG+16   |

| I 17 I 10001<br>I 18 I 10010<br>I 19 I 10011                 | I 1 0<br>I 1 1<br>I 1 1<br>I 1 1 |                                                      | 0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0 |                            |

| I 20 I 10100<br>I 21 I 10101<br>I 22 I 10110                 | I 1 1<br>I 1 1<br>I 1 1<br>I 1 1 |                                                      | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                            |

| I 23 I 10111<br>I 24 I 11000<br>I 25 I 11001                 | I 1 1<br>I 1 1<br>I 1 1<br>I 1 1 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | 0 0 0 0 0 0 0 0 0 0 0<br>1 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | I<br>I ∕ PG <b></b> +n     |

| I 26 I 11001<br>I 26 I 11010<br>I 27 I 11011<br>I 28 I 11100 | I 1 1<br>I 1 1                   | $\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$ | 1 1 1 0 0 0 0 0 0<br>1 1 1 1 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | I<br>I<br>I                |

| I 29 I 11101<br>I 30 I 11110                                 | I 1 1<br>I 1 1                   | 1 1 1 1 1<br>1 1 1 1 1                               | 1       1       1       1       0       0       0         1       1       1       1       1       0       0       0         1       1       1       1       1       0       0       0         1       1       1       1       1       0       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I<br>I<br>I                |

| I 31 I 11111<br>II                                           | I 1 1<br>I                       | 1 1 1 1 1                                            | 1 1 1 1 1 1 1 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | IJ<br>-I                   |

The PG can generate the 32 masks required to view the BS as both a logical and cyclic shifter. As is seen from Figure 2.11. the postshift mask generation data can come from one of three sources, CM|OD|SG.

31

Which particular source is to be used as data for the mask generation is determined by the contents of a 2-bit Postshift mask Generator Selection register (PGS) as shown in this figure and in Table 2.8. below.

#### Table 2.8.

Source of Data for Postshift Mask Generation

| Contents of PGS | Source of DATA |

|-----------------|----------------|

| 00              | СМ             |

| 01              | OD             |

| 10              | (undef)*       |

| 11              | SG             |

If, what we will assume as standard, the PGS has been set to point to the CM as the data source, then the PG data are specified in the "microoperations and data" field of the microinstruction in the following symbolic way,

PG "arrow" n

where,

n = the number of 0's to be generated and the "arrow"

(← |→) indicates from which direction they should be generated; 0 ≤ n ≤ 16.

Thus, the previous two examples could have been written (assuming PGS and BSS points to the CM as the data sources).

WB:=WA,

$$\leftarrow$$

2; PG $\leftarrow$ 2

WB:=WA,  $\rightarrow$  6; PG $\rightarrow$ 6

Upon dead start, the system is such that the mask of all 1's is in register 0 of PA, and the mask of all 0's is in register 1 of PA. This is identical to the situation in MA. We will assume this to be the case

<sup>\*)</sup> At the moment undefined

throughout normal operation of the system. One can then look upon the pointer PAP as a switch for the use of the Postshift mask Generator: if PAP = 0 then the mask generator is not used, if PAP = 1 then the postshift mask which is to be applied will be that generated by the mask generator. This is, of course, not the only interpretation of the use of the postshift masks, but it is a convenient one and one which we shall normally employ unless otherwise stated.

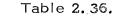

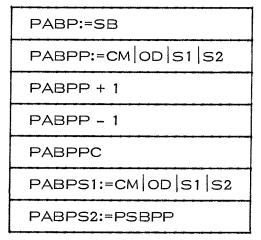

Table 2.9. is a list of the microoperations associated with the PM. The first half of this table deals with PA. The second half of this table deals with the PG. The name of the SG associated with the PG control is the Postshift Mask Generator SG (PGSG). Note, the name of the SG associated with the PA pointer is the Postshift AB Pointer (PABP). It is not discussed here but in Section 2.28.

| Table 2.9. | Tabl | е | 2. | 9. |

|------------|------|---|----|----|

|------------|------|---|----|----|

Microoperations for the control of the PM

| Operations associated with PA          |

|----------------------------------------|

| PA :=BUS                               |

| PAP:=CM OD SB SG                       |

| PAP +1                                 |

| PAP -1                                 |

| PAPC                                   |

| Operations associated with PG and PGSG |

| PGS:=CM                                |

| PGS +1                                 |

| PGS -1                                 |

| PGSG:=SB                               |

| PGP :=CM OD PGS1 PGS2                  |

| PGP +1                                 |

| PGP -1                                 |

| PGPC                                   |

| PGS1:=CM OD PGS1 PGS2                  |

| PGS2:=PGP                              |

33

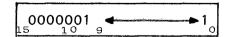

Let us extend the example of Section 2.5. in which we emulated a virtual machine instruction which performed a register to register transfer combined with left/rigth cyclic shifting. As shown below, if we use the PG we can execute an instruction which will take a given WB register (WB Adr), shift it left/right logical or cyclic (Shift & Mask Data), and then store it in a WA register (WA Adr). If the data for the instruction is in the current WB register pointed at by WBP in the form

a possible code sequence would be:

| WB,     | ; WAP:=SB, WBP+1.     |

|---------|-----------------------|

| WB, →4  | ; PG SG:=SB.          |

| WB      | ; BSSG:=SB, WBP-1.    |

| WB      | ; WBP:=SB, WBPS:=WBP. |

|         | ; PAP+1, PGS:= SG.    |

| WA:=WB, | ; PG- WBP:=WBPS       |

|         | ; PAPC, PGS:= CM .    |

Note well, there are two important assumptions in this example. The first is that MAP = 0 upon entry to this code, i.e., a bus mask is not applied to the source, and the second is that PAP = 0 upon entry to this code, i.e., no postshift masking occurs. Indeed, we will make these assumptions in all examples which follow (unless stated explicitly otherwise). They can be summarized as follows: bus transport normally occurs in an unmasked fashion; if a particular code segment requires the use of a masking facility it is responsible for leaving the system in this normal state after such masking occurs.

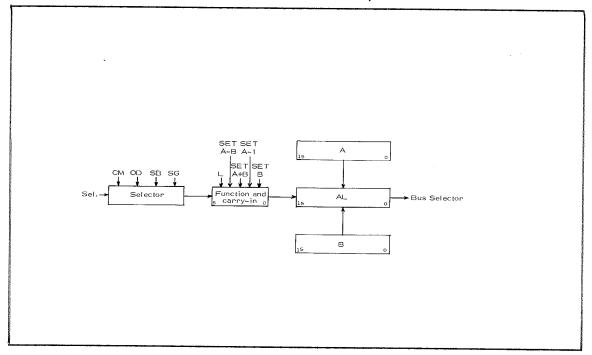

We will now add additional computational capability to the bus structure in addition to the shifting and masking already encountered by introducing the Arithmetical and Logical Unit (AL). The AL, shown in Figure 2.12., is a functional unit with 2 inputs which, for the moment we will call A and B.

Figure 2.12. Arithmetical Logical Unit, AL

6 bits are required to control the AL: 5 bits to select one of the 32 operations listed in Table 2.10. which this unit can execute on A and B and 1 bit which specifies the carry-in bit into the AL for any arithmetic operations.

| AL Functions        |                                                                                                                          |  |

|---------------------|--------------------------------------------------------------------------------------------------------------------------|--|

| ARITHMETIC          | LOGICAL                                                                                                                  |  |

| A<br>A V B<br>A V B | $ \overline{\mathbf{A}} \\ \overline{\mathbf{A}} \land \overline{\mathbf{B}} \\ \overline{\mathbf{A}} \land \mathbf{B} $ |  |

| minus 1*            | all 0's                                                                                                                  |  |

| A + (A∧B)           | ⊼∨B                                                                                                                      |  |

| (A∨B) + (A∧B)       | B                                                                                                                        |  |

| A-B-1               | А ‡ В                                                                                                                    |  |

| (A∧Ē)-1             | А ^ Б                                                                                                                    |  |

| A + (A∧B)           | А ∨ В                                                                                                                    |  |

| A + B               | A ≡ B                                                                                                                    |  |

| A√B + (A∧B)         | B                                                                                                                        |  |

| (A∧B)−1             | A ∧ B                                                                                                                    |  |

| A + A               | all 1's                                                                                                                  |  |

| (A∨B)+A             | A∨B                                                                                                                      |  |

| (A∨B)+A             | A∨B                                                                                                                      |  |

| A−1                 | A                                                                                                                        |  |

Table 2.10. AL Functions

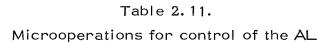

\* in 2's complement; the arithmetic operations are shown with the carryin set to 0. If the carry-in is 1, then the AL Function is F+1 where F is the specified arithmetic function. The logical functions are not affected by the carry-in. The 6 control bits which specify the current operation for the AL are the contents of the AL Function and Carry-in register, ALF, which can be loaded, ALF:=CM|OD|SB|SG, or set to the arithmetic addition operation A + B and other standard settings. The SG associated with the ALF is called the AL Standard Group (ALSG). The microoperations associated with the AL are given in table 2.11.

```

ALF:=CM OD SB SG

SET ALF +

SET ALF -

SET ALF B

SET ALF A - 1

ALSG:=SB

ALP:=CM OD ALS1 ALS2

ALP +1

ALP -1

ALPC

ALS1:=CM OD ALS1 ALS2

ALS2:=ALP

```

If the ALF is to be loaded with an operation specification from the CM, we will note this symbolically merely by writing the required function in the symbolic form which appears in Table 2.10. in the ALF assignment statement, i.e.,

$$ALF:=A + B$$

$ALF:=A \land B$

etc.

The AL is always running. If the ALF is changed in a microinstruction, then the result of the newly computed function is available for bus trans-

port in the very next microoperation. Thus the microinstructions

; ALF:=all 1 s, PAP +1.

WA:=AL; PG

$$\rightarrow$$

9, PAP -1.

will put a string of 7 1's in the WA register pointed to by WAP. The 1's will be least significant bits,  $b_0$ , justified.

There are many testable conditions concerning the operation of the AL. A few of these are

| Symbolic Notation | Condition                                                                        |

|-------------------|----------------------------------------------------------------------------------|

| AL<br>AL(0)       | result of AL operation all 1's<br>bit 0 of the result of the AL operation        |

| AL(15)            | bit 15 of the result of the AL operation                                         |

| ALOV              | Al overflow (equivalent to a carry-out<br>during addition and a borrow-in during |

|                   | subtraction)                                                                     |

Before giving examples of the control of the AL let us first discuss the nature of its inputs, A and B.

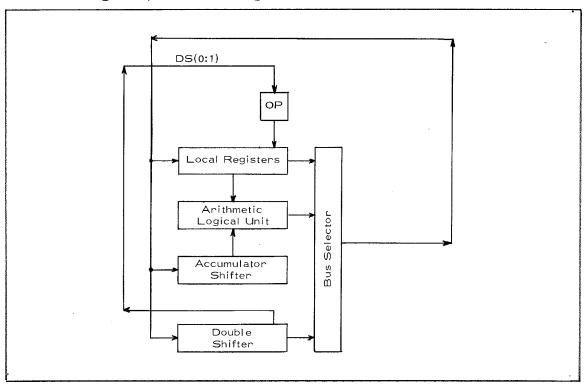

#### 2.9. The Local Registers

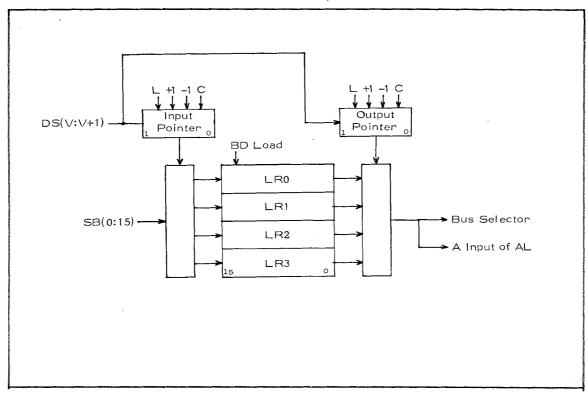

The Local Registers, LR, serve as the A input to the AL in the context of the AL Functions shown in Table 2.10. The LR, shown in Figure 2.13, are 4 16-bit wide registers which have independent input and output pointers. The input pointer, LRIP, points to a LR which can be used as a BD for the current bus transport. The output pointer, LROP, points to a LR which can be used as either the A input to the AL or as the SOURCE for the current bus transport.

Figure 2.13. Local Registers, LR

Both the LR input pointer, LRIP, and the LR output pointer, LROP, are incrementable, decrementable, clearable, and loadable with two bits from the Double Shifter, DS(V:V+1), see Section 2.12. The utility of this last feature will be demonstrated with examples when the Double Shifter is introduced. Table 2.12. gives the microoperations associated with the control of the LR.

Table 2.12. Microoperations for control of the LR

```

LRIPC

LRIP + 1

LRIP - 1

LRIP:=DS(V:V+1)

LROPC

LROP + 1

LROP - 1

LROP:=DS(V:V+1)

LRPC

LRP + 1

LRP - 1

LRP - 1

LRP:=DS(V:V+1)

```

The last four microoperations allow for the clearing, incrementing, decrementing, and loading of both the IP and the OP simultaneously.

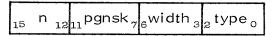

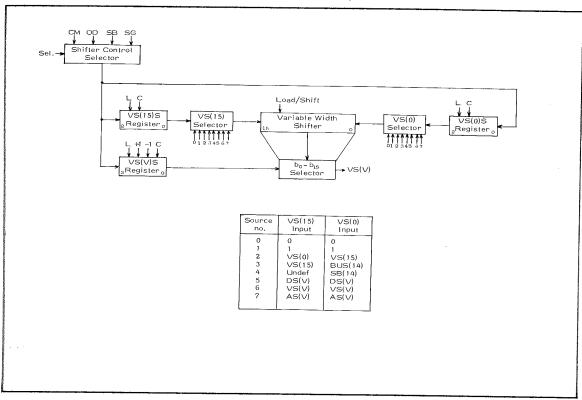

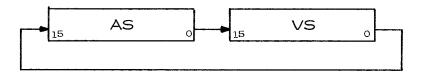

## 2.10. The Accumulator Shifter

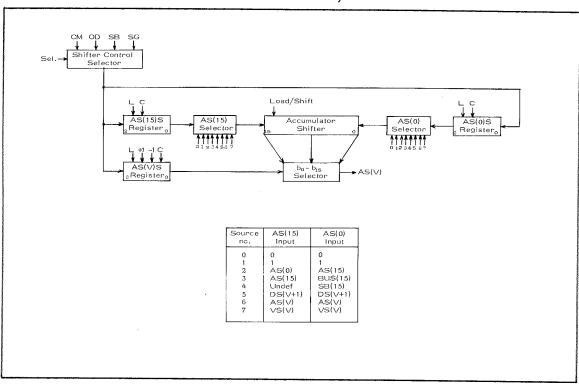

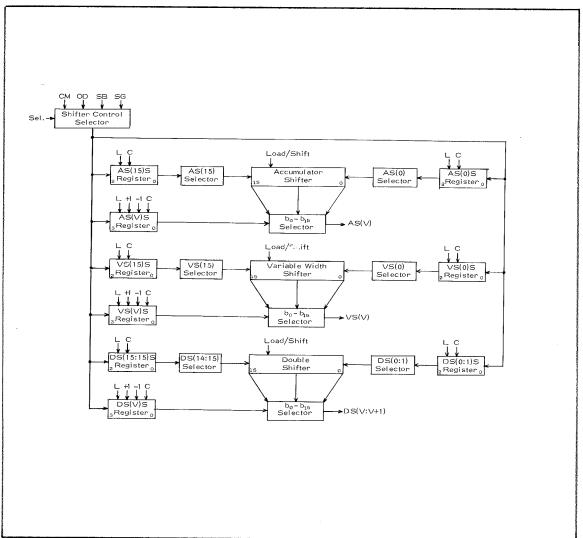

The Accumulator Shifter, AS, serves as the B input to the AL in the context of the AL functions shown in Table 2.10. The AS can serve as a bus DESTINATION; but to be read, its contents must be gated through the AL with the ALF set to B. The AS, shown in Figure 2.14., is a 1-bit shifter which can shift left, shift right, be loaded, or remain idle during the execution of any given microinstruction.

Figure 2.14. Accumulator Shifter, AS

There are 2 interesting features of this shifter:

- a) its variable width characteristic and

- b) its connection to other elements of the system.

The features are discussed in the following:

a) Although the shifter is 16-bits wide it may, in connection with either the BM or PM, be viewed as being m-bits wide ( $1 \le m \le 16$ ). This is accomplished by having each of the 16 bits of the AS input to a selector (labelled the  $b_0 - b_{15}$  selector in Figure 2.14). The output of this selector (called the variable bit, V) can then be a possible input into either the left or right end of the shifter, depending upon what particular type of shift one requires. When the AS is selected as a source for bus transport by gating it through the AL, after the desired shift has occurred, the bits not considered to be a part of the shifter must be masked off. This can be done either by using the BM or the PM. The width of the shifter is then determined by the contents of the AS(V)Selection register, AS(V)S, as shown in the above figure and the use of of an appropriate mask.

The AS(V)S can be loaded by the following microoperation

$$AS(V)S:=CM|OD|SB|SG.$$

Thus, for example, if we wish to consider the AS as a 12 bit left cyclic shifter, we would execute the microoperation

## AS(V)S:=11

while making sure that AS(V) be used as the input to bit AS(0) during the shift operation. Subsequent use of the AS as a source could be accompanied by use of the PG masking off bits  $b_{15} - b_{12}$ , e.g.

b) In Figure 2.14. it is seen that bits AS(0) and AS(15) can be filled by one of a variety of sources during a shift operation. Which source is to be used to fill the vacated bit position is determined by the contents of the AS(0) and AS(15) source selection registers, AS(0)S and AS(15)S respectively. An examination of the table in Figure 2.14. shows that the AS can be considered a logical shifter, a 1's fill shifter, a cyclic shifter, and a right arithmetic shifter. It can also be connected to another 1 bit shifter, called the variable width shifter, VS, to yield a long variable width shifter. It can be connected to a 2-bit shifter called the Double Shifter, DS, so it can be used in the merging of 2 bit streams into 1 or the diverging of 1 bit stream into 2. It can also be connected to the BUS and SB. These latter input is of an experimental nature and uses will be demonstrated in later examples.

Thus to use the AS, one must load the AS(V)S to set the width of the shifter and must load either the AS(0)S or AS(15)S to point to the source to be used as the input into the vacated bit position, i.e., one must set what the type of shift is, e.g., logical, 1's fill, long, etc. That both of these operations need not be done each time the shifter is used, but only when one is "changing" the width or type of shifter is obvious. Table 2. 13. lists the microoperations associated with the control of the AS. Note the AS can be set to a logical left, ASLL, or logical right, ASLR, shift.

Table 2.13. Microoperations for control of the AS

AS(0)S := CM | OD | SB | SGAS(15)S := CM | OD | SB | SGAS(V)S := CM | OD | SB | SG $ASLL \quad (\equiv AS(0)SC)$  $ASLR \quad (\equiv AS(15)SC)$ AS(V)SCAS(V)S+1AS(V)S-1

There are 2 bits in each microinstruction which control the operation of the AS: shift left, AS, shift right, AS, load, i.e., AS:=SB(0:15), or be idle. When the AS is to be shifted, the operation is put in the "microoperation and data" field of the microinstruction; when the AS is to be loaded, the operation is specified in the "bus transport" field of the microinstruction. As an example, the microinstruction

stores the output of the AL in a WA register and then shifts the AS left, while the microinstruction

LR, AS:=WB; WBP + 1.

stores a WB in both the AS and a LR and then increments the WB pointer. If the AS is not employed during a given microinstruction, it does not appear in the specification of that microinstruction.

Having introduced the AL and its inputs, LR and AS, we now have knowledge of the expanded bus structure as shown in Figure 2.15.

Figure 2.15. Expanded Bus Structure

Let us now give a few examples using these resources to demonstrate the use of their associated microoperations.

#### Example 1

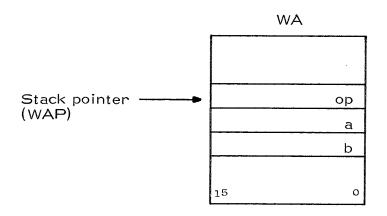

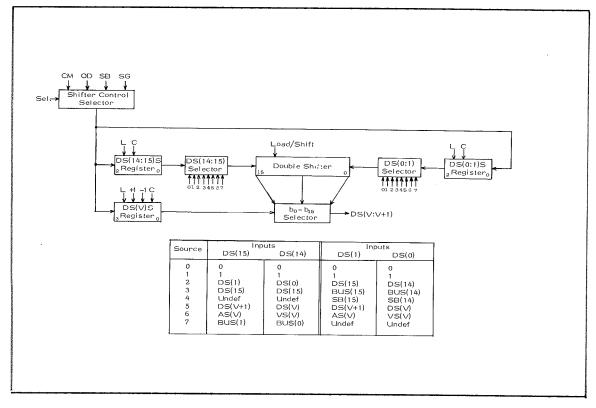

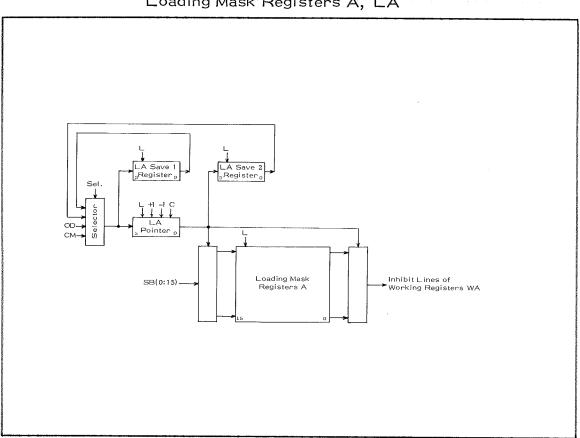

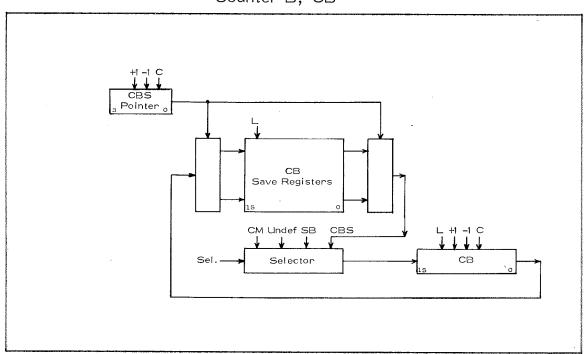

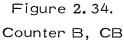

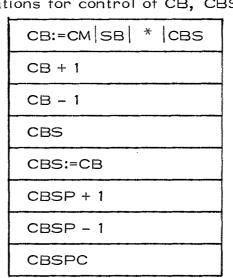

Let us consider WA as a stack as shown below